02 2023 档案

摘要:# AMBA总线介绍 ## 1 HSIZE AHB总线的地址位宽和数据位宽一般都是32bit,**一个字节8bit,一个字节占用一个地址空间**,但当一个32bit的数据写入一个存储器中或者从一个存储器中读取,**32bit数据几个时钟能够传输完成,这和hsize信号有关**,这个信号表示**一个时

阅读全文

摘要:AMBA总线介绍 AMBA总线概述 AHB APB 不同IP之间的互连 1.系统总线简介 系统芯片中各个模块之间需要有接口连接,使用总线作为子系统之间共享的通信链路 优点:成本低,方便易用(通用协议,不用协议之间的转换模块) 缺点:容易造成性能瓶颈(Bus上挂载很多模块,会有冲突,需要仲裁,造成性能

阅读全文

摘要:项目芯片介绍 面试中经常会问,在项目中负责什么?有什么难点?如何实现? 1.简介 1.1 需求 需要了解需求(芯片需要哪些模块,与哪些接口通信),这个项目是一个MCU的芯片,MCU中集成了一个轻量级的CPU,CPU以当前ARM的芯片为例(A系列芯片,M系列芯片)。 芯片需要与外界进行通信,SD接口,

阅读全文

摘要:CDC设计实例 加速器 假设要处理一项业务比如图像处理,有两种方向,第一种选择一些通用的处理器CPU\GPU\DSP等通用的处理器,第二种是将算法映射成IP,直接使用IP进行处理图像处理等专门的业务就是加速器。加速器是挂接到总线上的,类似于DMA,需要CPU派发一些任务给加速器执行。 软件配置 C代

阅读全文

摘要:CDC设计实例 Clock Gating Cell & Glitch Free Clock Switch(门控单元和动态切换时钟) 一个电路有多个时钟输入进来,希望在工作当中能够动态切换时钟;比如CPU根据工作负载(AI或视频处理),工作负载大,时钟频率快,功耗高,工作负载低(浏览图片或者待机),时

阅读全文

摘要:时钟域 所谓的时钟域的定义是以捕获时钟来划分时钟域。看上面的图,以捕获的时钟来划分时钟域,图1,它的launch时钟是CLKB,它捕获时钟呢,也是CLB,那么我们以捕获时钟来作为划分时钟,这个时钟域就是CLKB时钟域。 图2,数据的发送和接收不是同一个时钟。以C2捕获时钟来作为这个电路的时钟。所以一

阅读全文

摘要:异步时钟 之前提到同步时钟是来自于同一个源的,那么异步时钟指的就是来自于不同源。它们之间没有固定的相位的关系。 上面电路图,几个时钟之间是什么关系呢? 首先ClockA和ClockA_div2这两个时钟,它是同步时钟,因为它们之间有固定的相位关系。ClockA_div2就来自于clockA。 Clo

阅读全文

摘要:1 ASIC 中时钟的结构 ASIC电路中的时钟的结构。这是一个非常典型的MCU的时钟结构图。它的时钟结构和功能的划分。首先,我们通过外部振荡器发送了一个8MHz的时钟给PLL,经过分分频和倍频产生更多的一些时钟。这些时钟再经过一些多路选择器来送给后面的电路。从上图里面看,我们把它做了1,2,4,8

阅读全文

摘要:同步时钟 所谓的同步时钟,我们指的是同源。也就是说时钟,它来自于同样的源头 比如一个电路有一个时钟clk,然后经过一个分频以后送到另外一个寄存器。那么,这个分频出来的时钟和clk,它们之间就是同源的。它们之间有固定的相位的关系,所以成为同步的时钟。 对于右边这个电路来讲呢,两个寄存器它接的都是同一个

阅读全文

摘要:1 什么是时钟? 1.1 时钟定义 跨时钟域处理,是在设计过程中经常要处理的问题,决定芯片的正确和可靠性 电脑中有很多的芯片,每个芯片都是在特定的时钟下进行工作的,时钟信号是连续的脉冲信号;它是按一定的电压幅度在一定时间间隔内连数连续发出的脉冲信号。 1.2 时钟偏斜(clock skew)和时钟抖

阅读全文

摘要:Clock Domain Crossing CDC问题主要有亚稳态问题,多比特信号同步,握手信号同步,异步Fifo等 Topics Describe the SoC Design Issues Understand the tranditonal verification limitation Kn

阅读全文

摘要:运算符 算术运算符 算数运算符: + - * / // % ** # + var1 = 7 var2 = 90 res = var1 + var2 print(res) # 97 # - var1 = 7 var2 = 90 res = var1 - var2 print(res) # 83 # *

阅读全文

摘要:数据类型 Number - 强制类型转换(int float bool complex) 1. 强制把数据转换为整型 - int float bool 纯数字字符串 # 强制把数据转换为整型 - int float bool 纯数字字符串 var1 = 13 var2 = 5.67 var3 = T

阅读全文

摘要:#数据类型 Number - 数字类型 数字类型包含int,float,bool,complex类型 int - 整型 整型 - 正数,负数,0 # type(variable) 可以查看变量的类型 # id(variable) 可以查看变量的地址 age = 18 res = type(int)

阅读全文

摘要:python简介 python认知 1、python简介 89年开发的语言,创始人范罗苏姆(Guido van Rossum),别称:龟叔(Guido). python具有非常多并且强大的第三方库,使得程序开发起来得心应手. Python程序员的信仰:人生苦短,我用python! 开发方向: 机器学

阅读全文

摘要:进制之间的转换 1.1 计算机硬件的基本认知 cpu: 中央处理器. 相当于人的大脑.运算中心,控制中心. 内存: 临时存储数据. 优点:读取速度快。 缺点:容量小,造价高,断电即消失. 硬盘: 长期存储数据. 优点:容量大,造价相对低,断电不消失。 缺点:读取速度慢. 操作系统:统一管理计算机软硬

阅读全文

摘要:亚稳态问题 各种跨时钟域的问题都会归结于亚稳态的问题,IP设计时钟域不超过两个,对于CDC设计要求不高;对于SoC设计来说,CDC处理十分重要 1.什么是亚稳态? transition time 是可以计算出来的值,与output load(输出负载),输出负载越大transition time 越

阅读全文

摘要:同步FIFO和异步FIFO FIFO分为一个同步FIFO,一个异步FIFO,FIFO有读口和写口 读写时钟是一个,就是同步FIFO;读写时钟不是一个,异步FIFO IP核设计中,一般使用同步FIFO设计 SOC设计或者跨时钟域的内容使用异步FIFO RAM FIFO中的数据,存储在寄存器中或者是SR

阅读全文

摘要:# 有限状态机 写RTL的时候,实现一个功能的时候有很多种方法 1. 将系统划分为多个状态,状态之间有状态的转移,第一步,第二步......形成有限状态机 2. 流水线技术设计,从输入到输出有多个步骤,多个步骤可以并行执行 有限状态机,状态是有限的,比如8个状态,16个状态等,在进行设计的时候,状态

阅读全文

摘要:# 经典组合和时序电路 HDL的主流语言 * VHDL * Verilog * System Verilog 硬件描述层次 * 门级(gate-level) * 寄存器传输级(RTL-Level) * 行为级 RTL:Register Transfer Level * 可综合性,写的代码要可综合 *

阅读全文

摘要:Verilog-线程 并发线程 verilog和C语言有一个最大的不同就是并发性 并发--同时进行的过程 module tb_test; int a; initial begin a = 1; a = 2; a = 3; end initial begin A1 #1 //a = 1; end in

阅读全文

摘要:任务Task和函数Function 类似于c语言中的函数 Task task 含有input\output\inout语句 task消耗仿真时间 task中可以写延迟:#20 延迟20个仿真时间单位 时钟周期 @(posedge Clk) 等待下一个时钟周期上升沿 事件 @event 等待某一个事件

阅读全文

摘要:一.数据类型 二值逻辑变量 bit 不赋值的时候,变量初始默认为0 x或z的值会转变为0 bit vector--bit矢量 bit [msb,lsb] variable_name = [initial_value] 位宽:最高位为MSB,最低位为LSB 不加任何描述,默认为unsigned,无符号

阅读全文

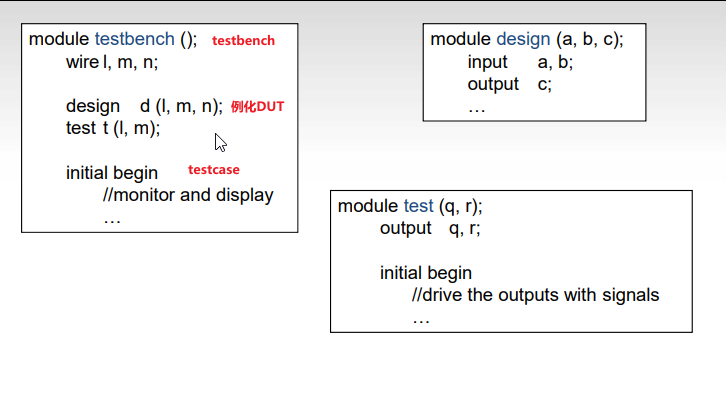

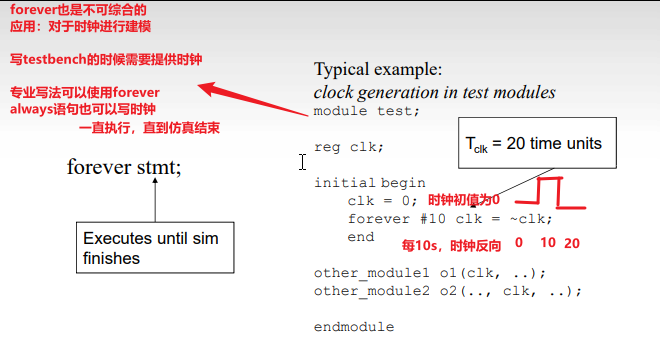

摘要:## How to build and test a module    ## System Tasks(系统任

阅读全文

摘要:# Module Module是verilog中的关键字,是对电路建模的最小单元。verilog中构建一个电路,对于一个硬件进行描述在module中进行。 的非,找的输出到地的通路,以原变量进行书写。最后将表达式取非,即可得到L。这种方法比看串并联快一些。 得到初步表达式的时候要化简 找齐所有的通路 例1 例2 例3 例4 例5

阅读全文

摘要:逻辑门电路习题 1.输入和输出之间电压的关系 前一级的输出作为后一级的输入,满足的输出电压和出入电压之间的关系。 2.多余门电路端子处理 3.扇出系数计算 高电平--扇出系数=输出的高电平/输入高电平 低电平--扇出系数=输出的低电平/输入的低电平 两者当中取小的 4.噪声容限 5.TTL门电路 6

阅读全文

摘要:逻辑门电路知识点总结 门电路注意事项 传输高低电压的问题 上一级输出为0,下一级的输入也要认为是0 逻辑0和逻辑1都是有范围或区间的,逻辑0有最大值,逻辑1有最小值 上一级输出和下一级输入之间电平的关系,加入上一级输出高电平的最小值是3.6V,下一级输入高电平的最小值要低于3.6V,这样才能保证,当

阅读全文

摘要:CMOS门电路 TTL是三极管构成的门电路,逐步被CMOS电路替代。CMOS电路能耗低、集成度高。 CMOS反相器 CMOS管是由PMOS和NMOS组成,这里用的都是使用的增强型。 COMS能够正常工作,对于电源是有要求的 输入为0 输入为0的时候,NMOS截止,PMOS导通 NMOS和PMOS都有

阅读全文

摘要:绪论 电信号 什么是电信号 信号是反应消息的物理量,比如温度、压力、流量、声音等,信号是消息的表现形式。 电信号比较容易传输、处理和控制,因此人们将非电物理量通过各种传感器转换成电信号,以达到信息的提取、传送、交换、存储的目的。 电信号是指随时间变化的电压u或者电流i,因此在数学上可以将它表示为时间

阅读全文

摘要:三态门(TSL) 普通的逻辑电路只有两个状态,还有一个高阻态。 EN是高电平1 A,B,EN之间的关系是与的关系,当EN为1得时候,EN就不起作用了,输入由A,B决定。EN端为高电平,所以二极管D2截止。就是一个正常的与非门,只有两种状态0和1。 EN是低电平0 EN为低电平,输入为低电平,T2,T

阅读全文

摘要:集电极开路门(OC门) OC门 两个与非门,要实现非,一般来讲再与一下就可以。 能不能将输出端并在一起?普通的门电路永远不可能输出端并在一起,连在一起的。 TTL与非门输出端连在一起 集电极断开之后连接在一起,可以将输出导线连接在一起。 用导线直接实现与逻辑,叫做线与。 与电源相连接的电阻称之为上拉

阅读全文

摘要:TTL与非门的电压传输特性 传输特性 输入电压连续发生变化,输出电压发生什么变化?需要研究输出电压与输入电压之间的关系 输入小的时候,输出大的信号;输入大时候输出小信号 中间有截止和导通,需要过渡过程,并不能进行突变,通过实验可以进行测定。 高电平和低电平是有区间的 中间不确定,实际不可避免,所以这

阅读全文

摘要:TTL与非门 集成电路有两大类COMOS和TTL(三极管) 电路结构 工作原理 多发射结的三极管,两个输入之间是与的关系 输入低电平 输入高电平 A、B都是高电平 倒置放大 压差大的先导通 T3,T4是推拉式的,一个通,另一个不通 多发射结效率高,输出端使用推拉式,提高带负载能力 如果负载中有电容,

阅读全文

摘要:卡诺图化简法练习 知道四变量卡诺图表示的最高位和最低位 给与或项形式 给与或项编码形式 含有无关项 给出F=(xxx)' 给出非式,在卡诺图中写0 F圈0,F'圈1 给出的卡诺图右上角是F',那么非式在卡诺图中要写1,圈0 第四题最后一项写是ABD哦 结果化成或与式 卡诺图得到与或式,变为或与式要圈

阅读全文