UVM - 18(Review and Lab4)

test

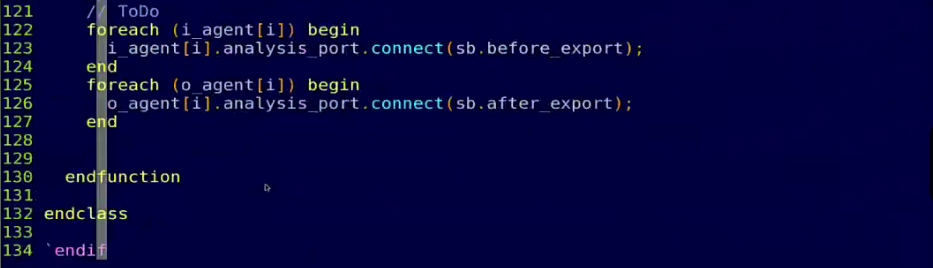

Makefile

- Makefile中定义变量,在运行Makefile的时候可以传入参数

make verbosity=UVM_HIGH

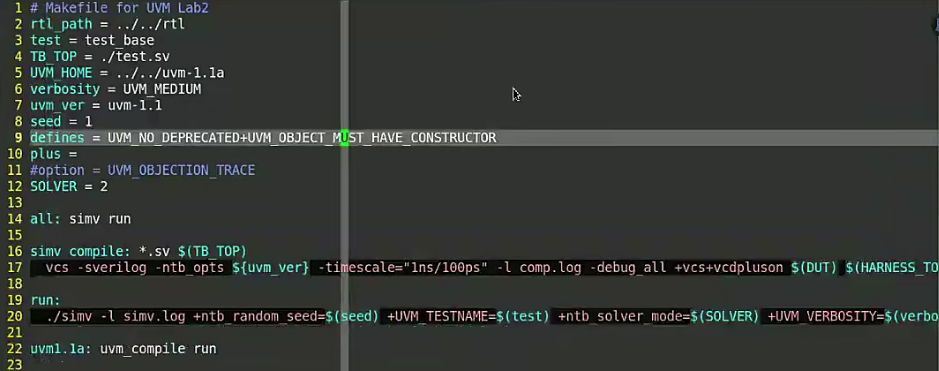

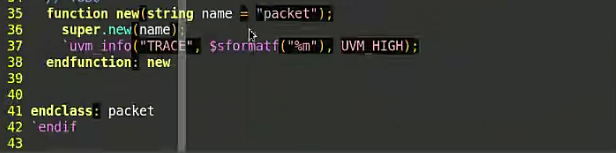

packet

- 继承自uvm_sequence_item

- 定义随机变量并创建约束

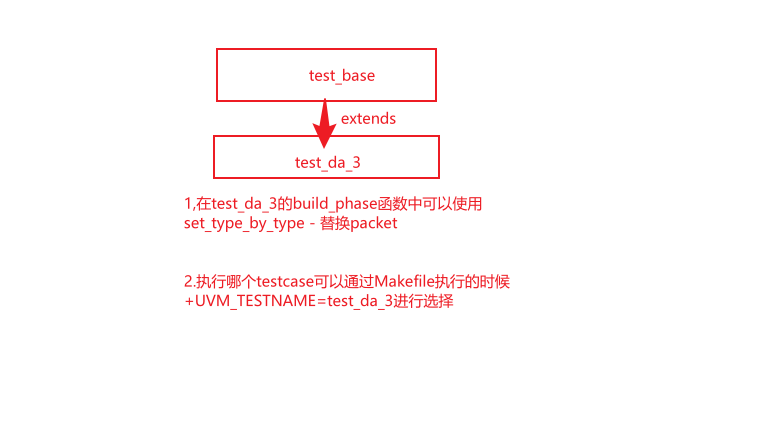

test_base

Virtual interface

- interface不能在class中进行例化,需要使用virtual interface

- virtual interface需要和实际的interface进行

- driver中定义虚接口,在使用的时候使用uvm_config_db的形式get接口

- 可以在test中用umv_config_db的形式配置接口

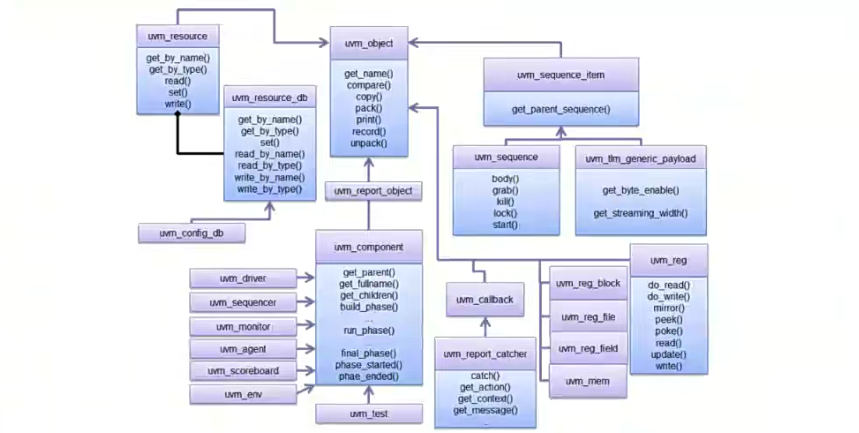

UVM_base Class Tree

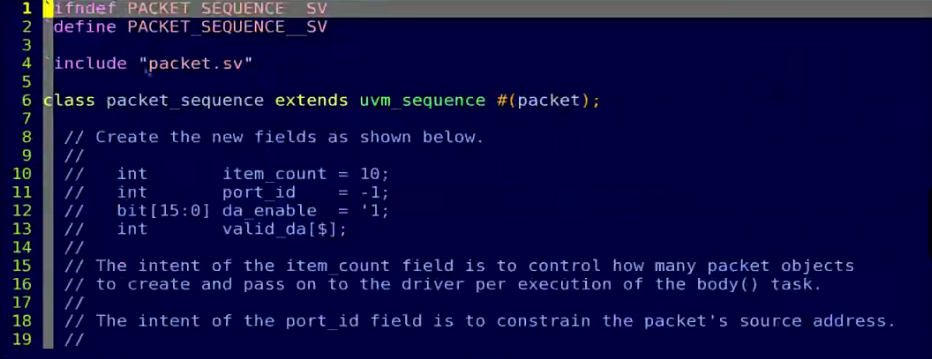

Lab3 - sequence

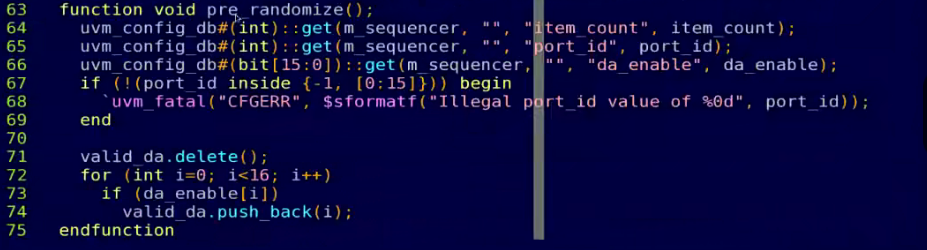

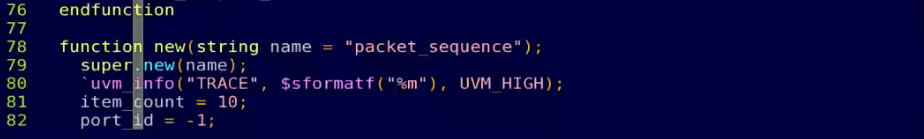

packet_sequence

- 定义变量赋初值可以在定义变量的时候赋初值,也可以在new函数中给变量赋初值

- pre_randomize()是在调用randomize之前进行调用的函数

- pre_randomize和post_randomize是自动进行调用的

- m_sequencer - 使用uvm_config_db配置其中的变量,然后设置一些约束

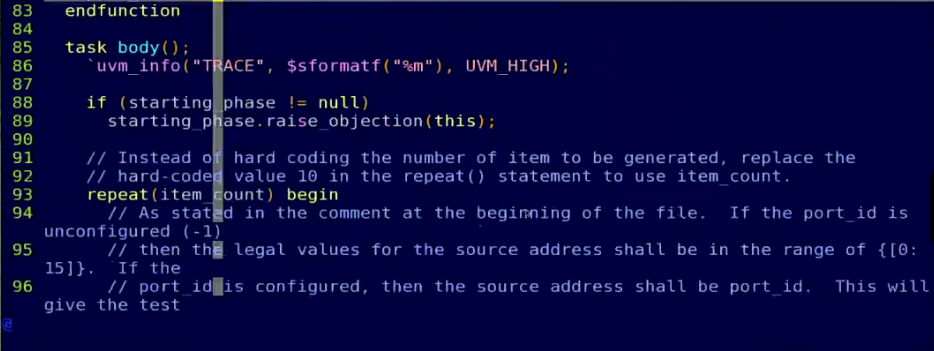

agent

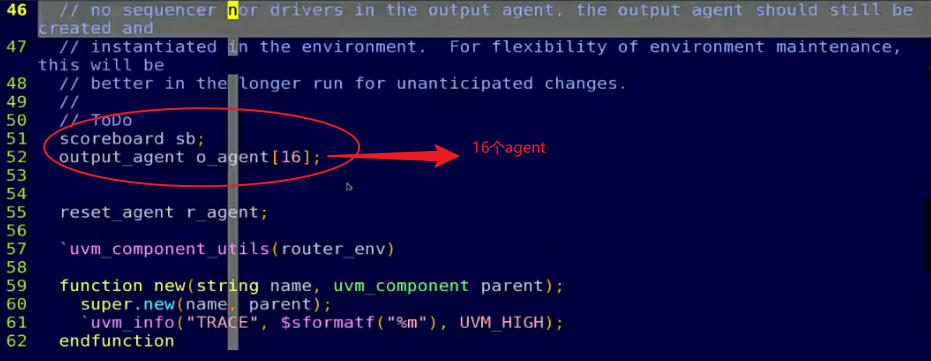

env

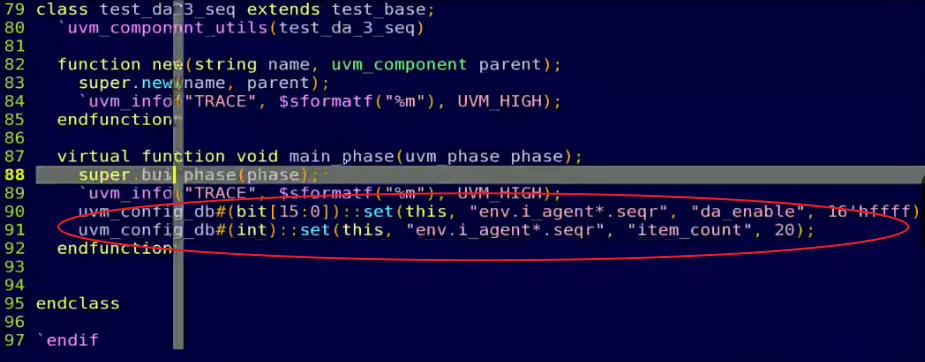

test

- 在test中的build_phase中设置sequence中变量

- sequence在main phase阶段可以通过config_db得到配置的变量的值

Lab4 - driver and monitor

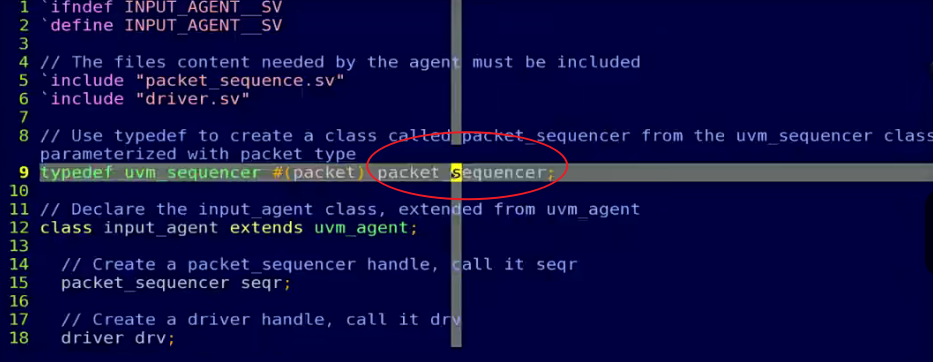

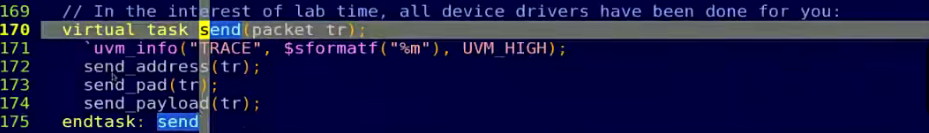

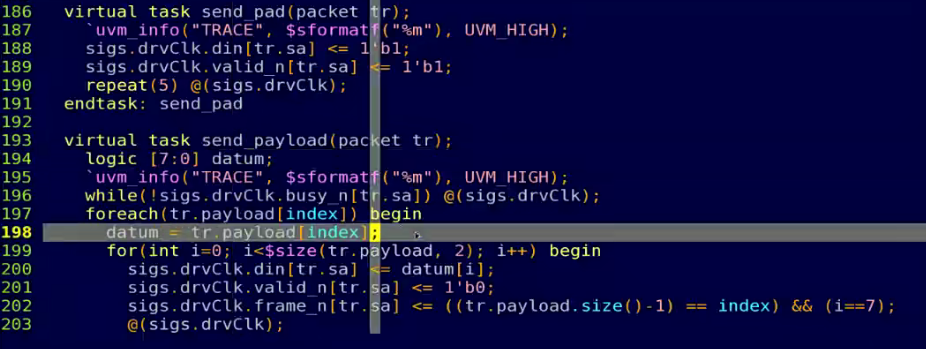

driver

class driver extends uvm_driver #(packet);

`uvm_component_utils(driver)

virtual router_io_sigs; // 定义接口

int port_id = -1;

function new(string name,uvm_component parent);

super.new(name,parent)

endfunction

virtual task run_phase(uvm_phase phase);

forever begin

seq.item_port.get_port_item(req);

if(port_id inside {-1,req.sa}) begin

send(req);

end

seq.item_port.item_done();

end

endtask

endclass

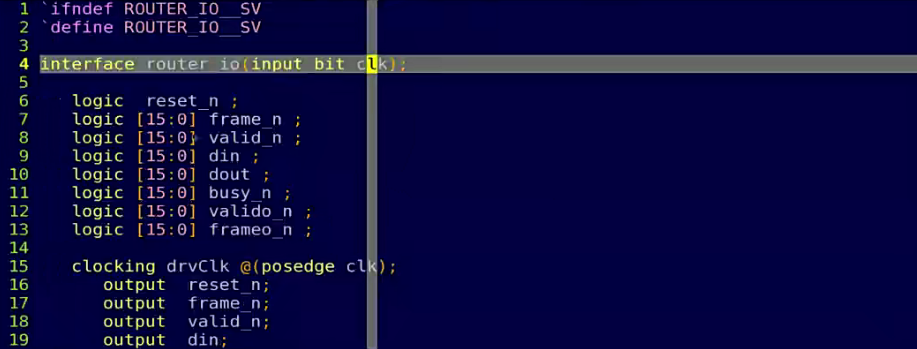

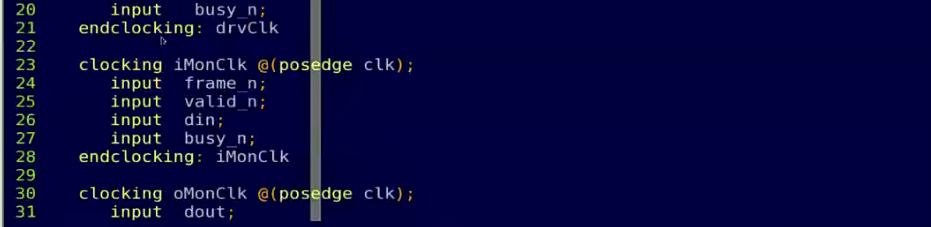

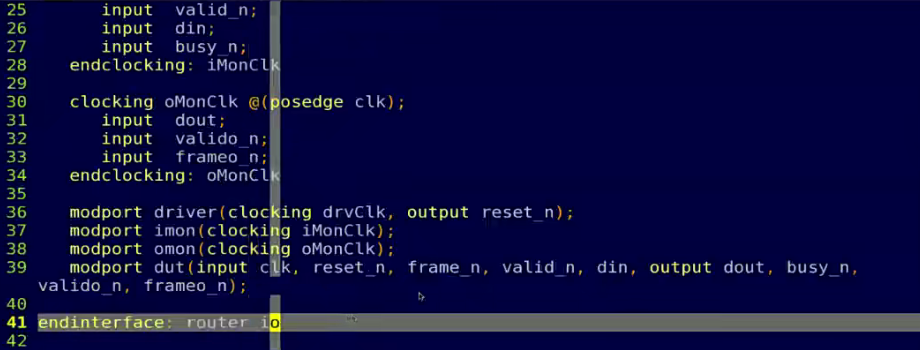

router_io(interface)

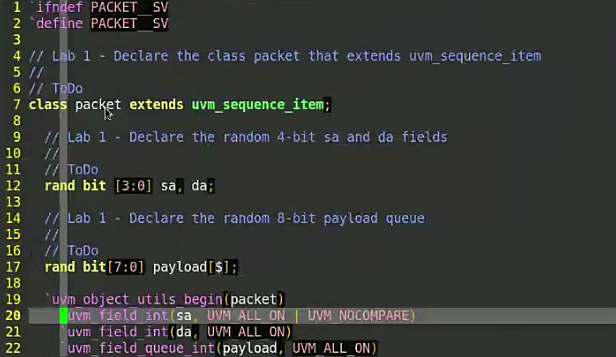

Lab5 scoreboard and monitor

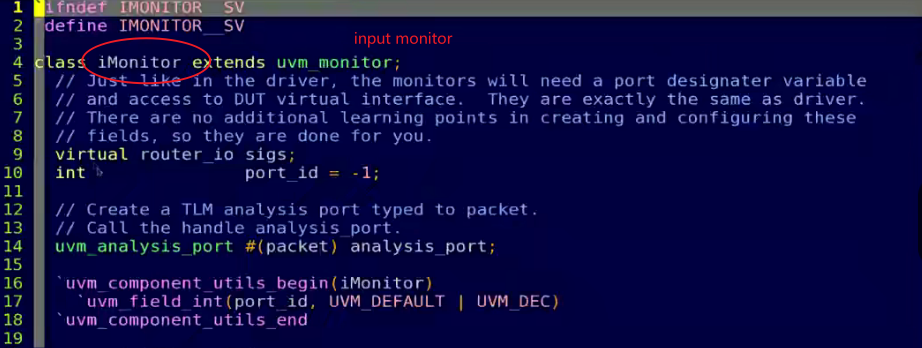

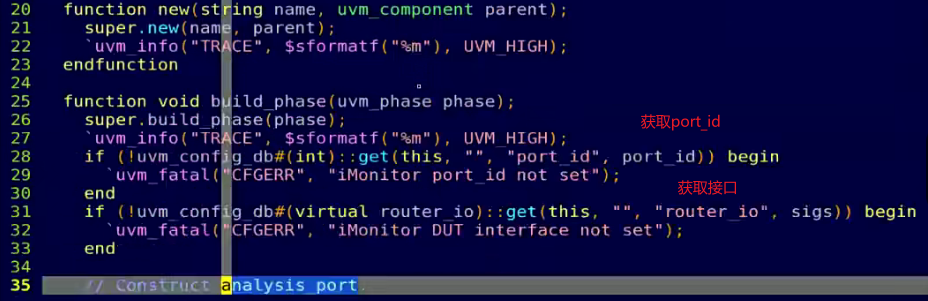

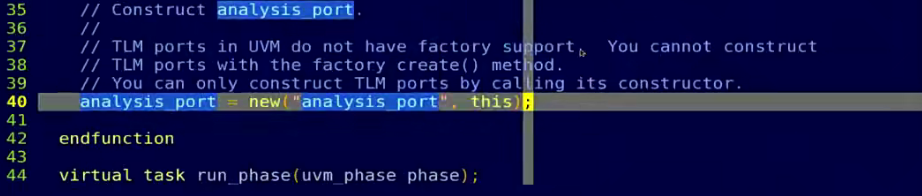

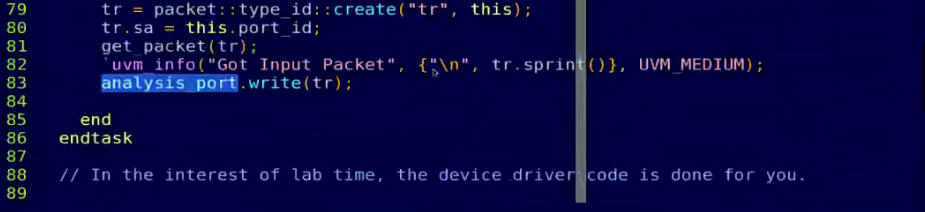

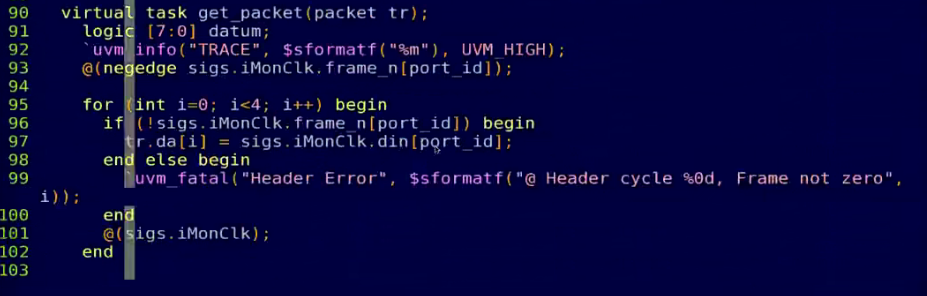

monitor

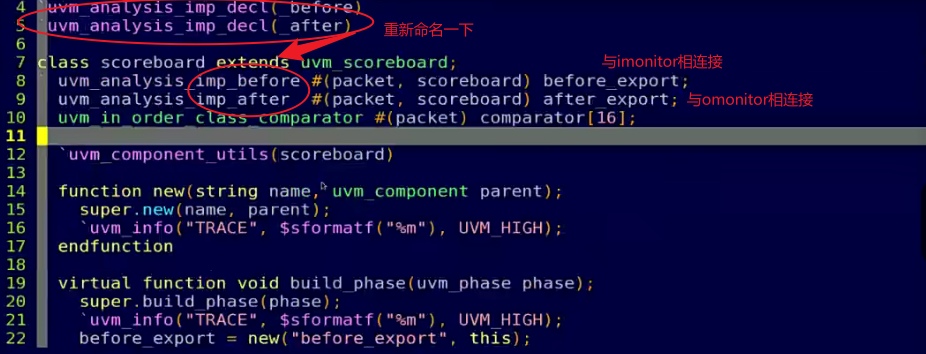

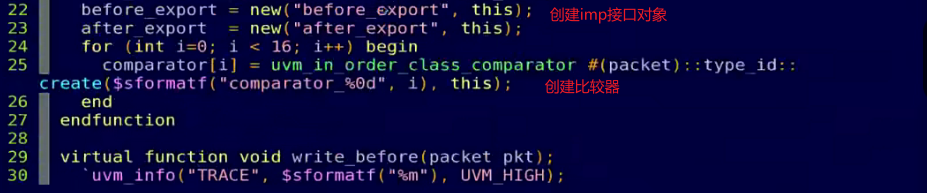

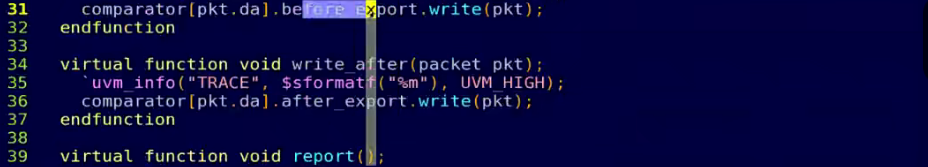

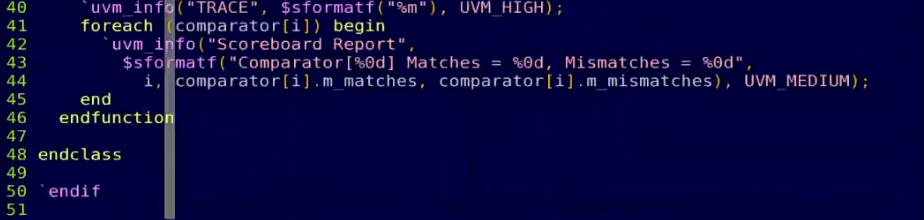

scoreboard

env