UVM - 10 (Sequence机制-2)

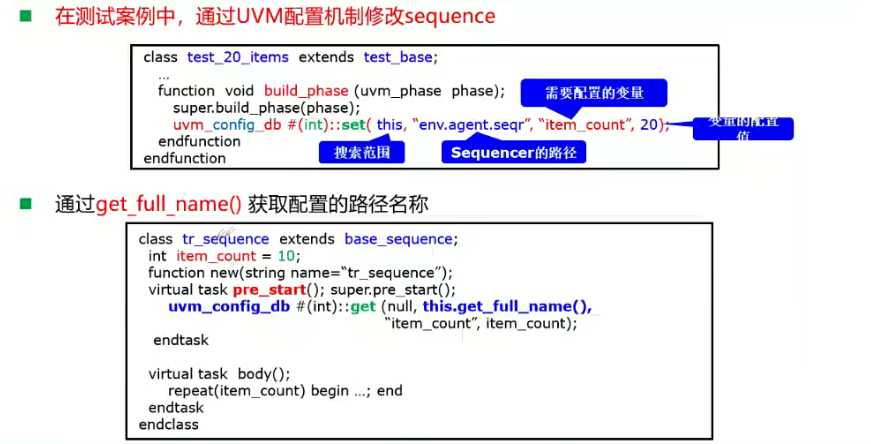

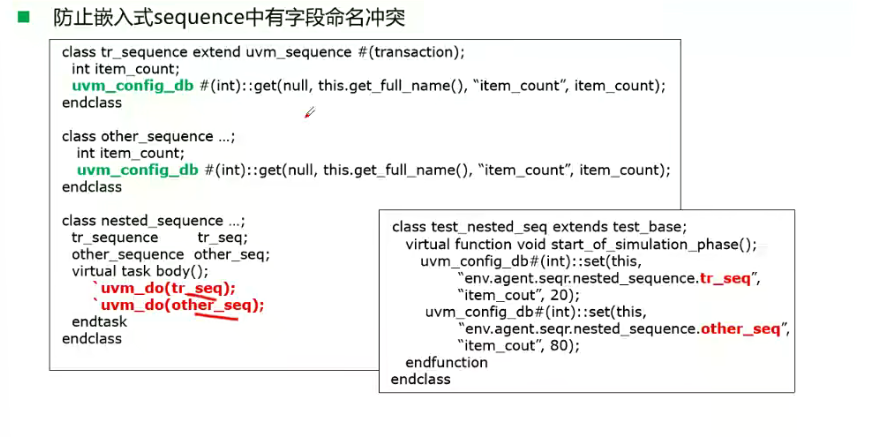

配置sequence:基于instance

基于instance配置的好处

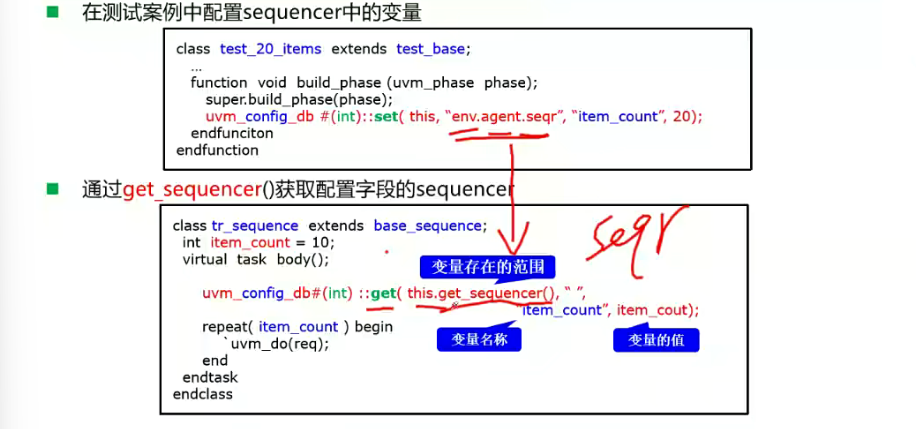

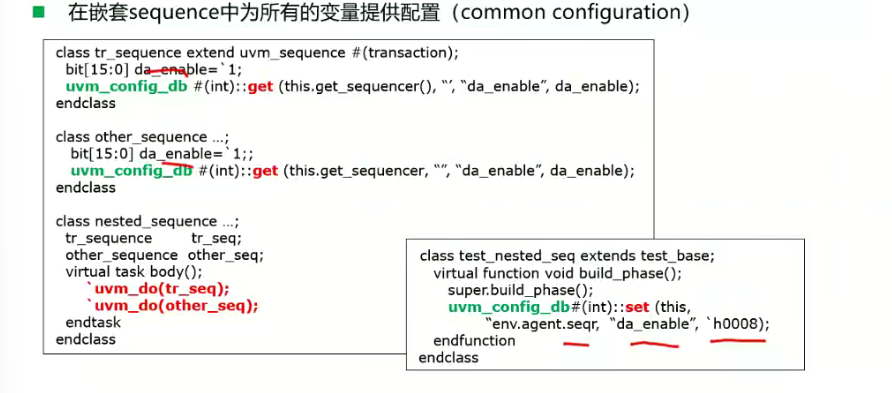

基于sequencer配置sequence

基于sequencer配置的好处

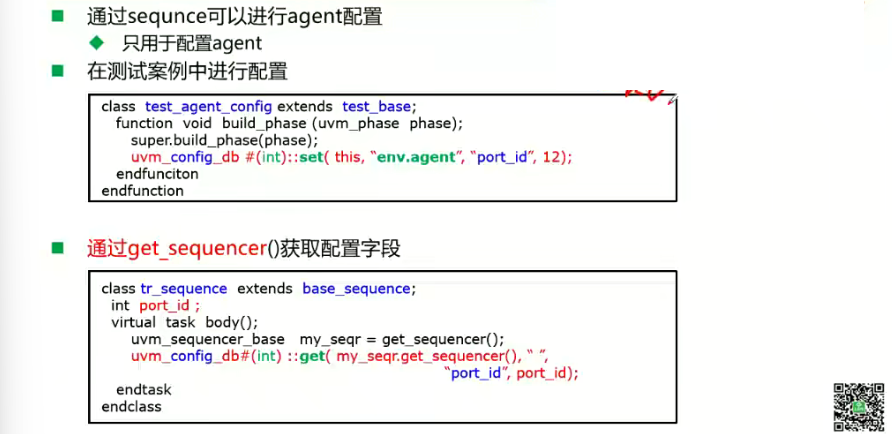

基于agent配置sequence

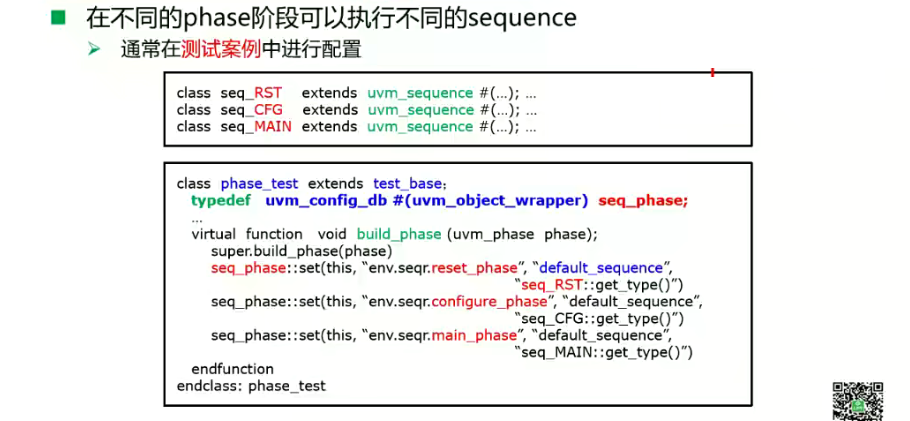

在phase中隐式执行sequence

显式执行sequence

sequence的优先级和权重weight

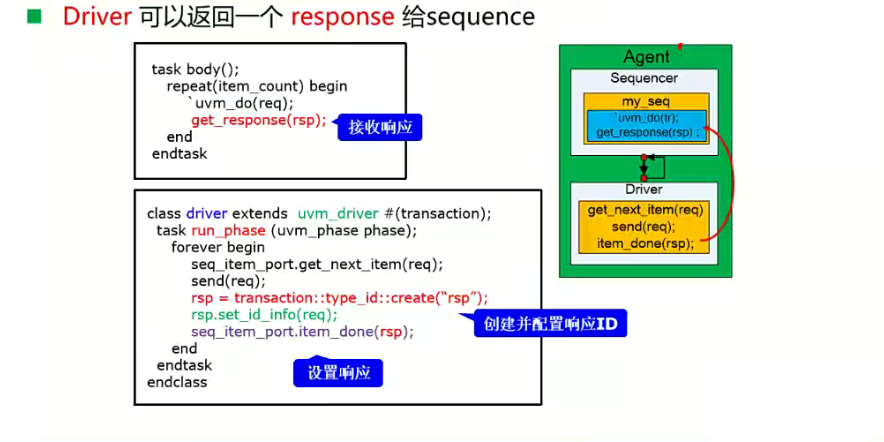

sequencer-driver 响应端口(report port)

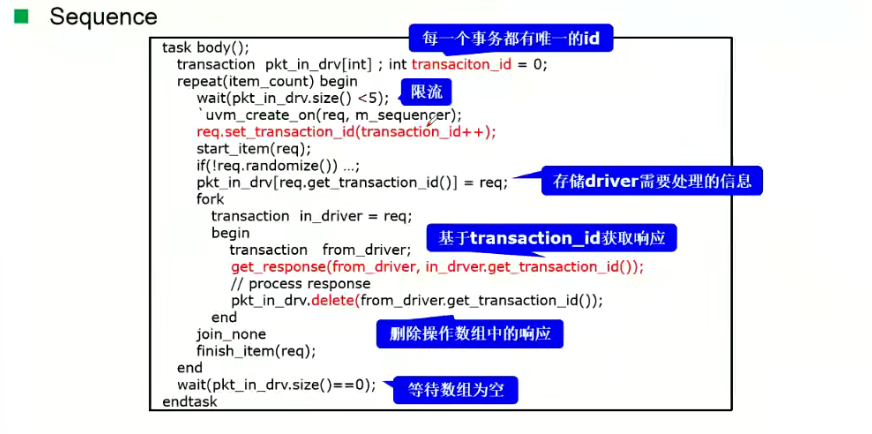

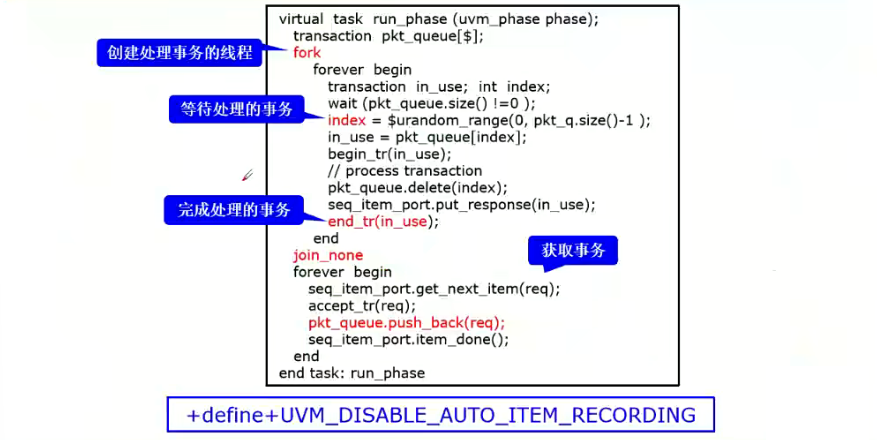

sequencer-driver 乱序端口

乱序Driver

- 一般来说一个test只调用一个sequence

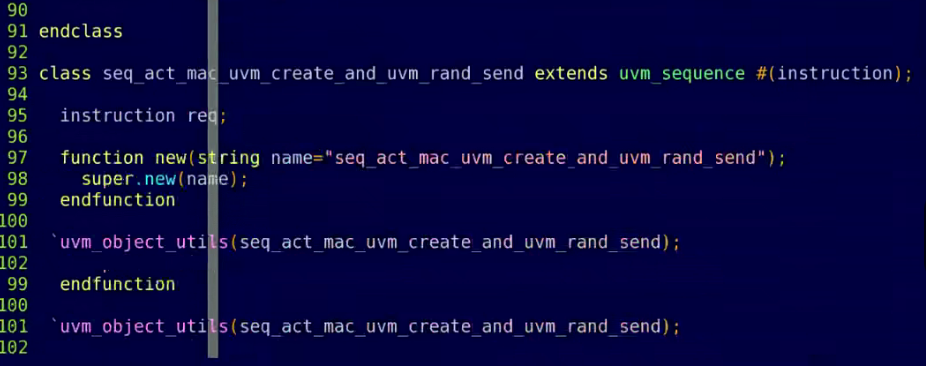

示例

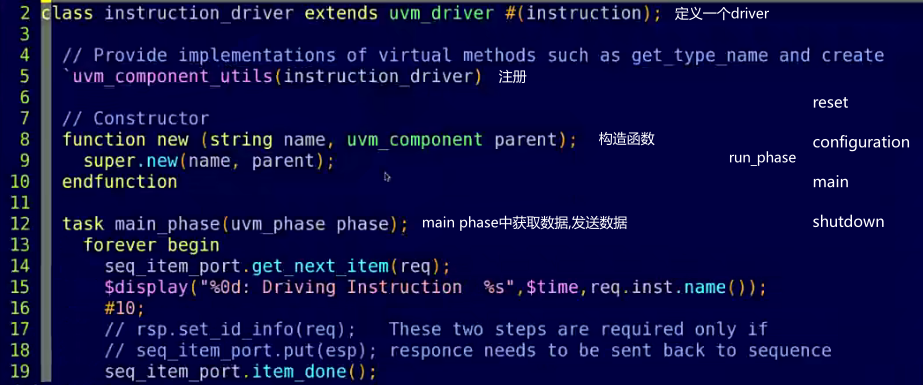

driver

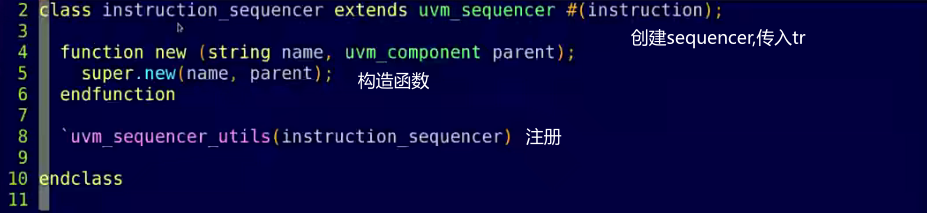

squencer

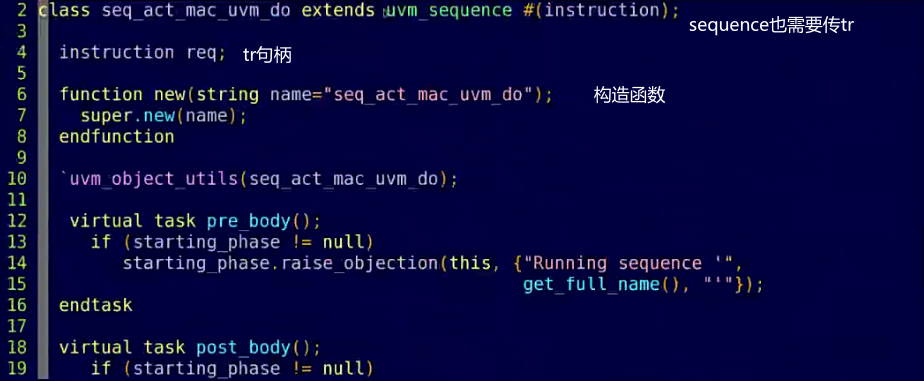

sequence

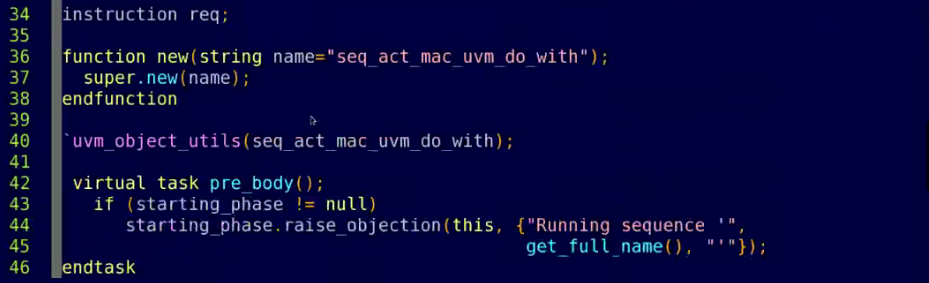

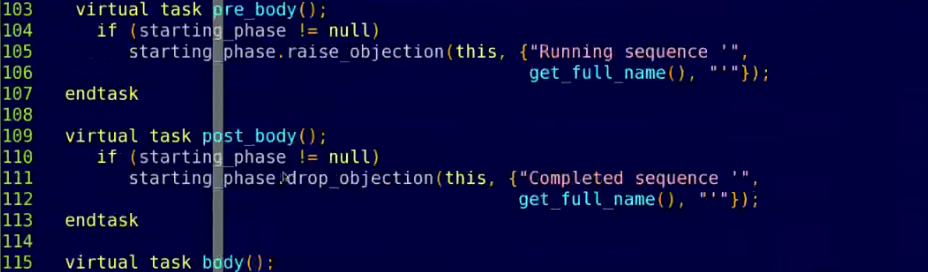

- raise_objection和drop_objection分别在uvm_do之前和之后就可以

- pre_start() --> pre_body() --> body() --> post_body --> post_start

// 方式1

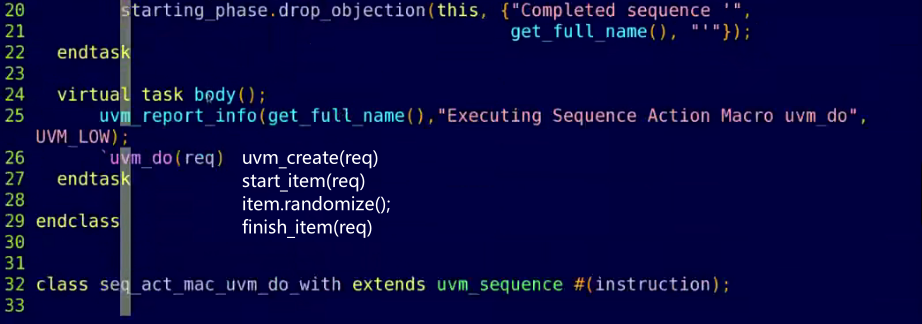

`uvm_do(req)

// 方式2

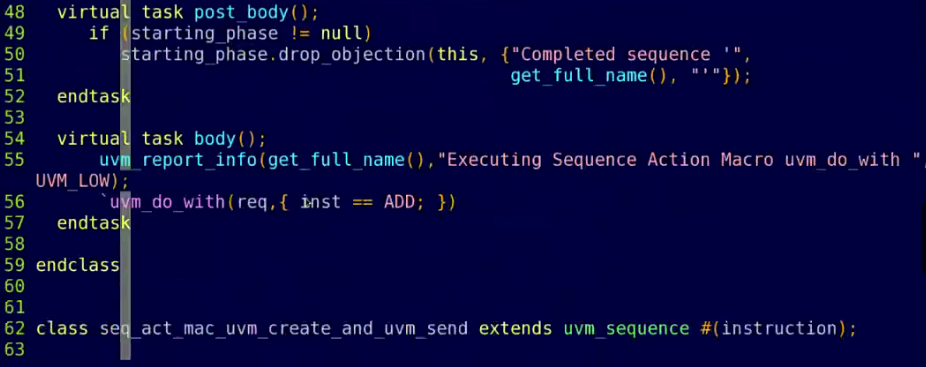

`uvm_do_with(req,{constraint})

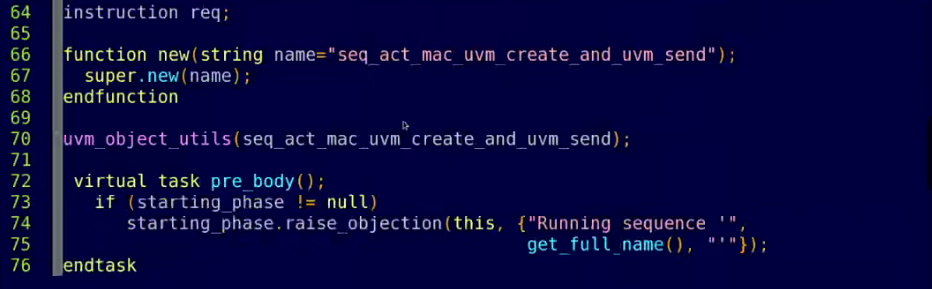

// 方式3

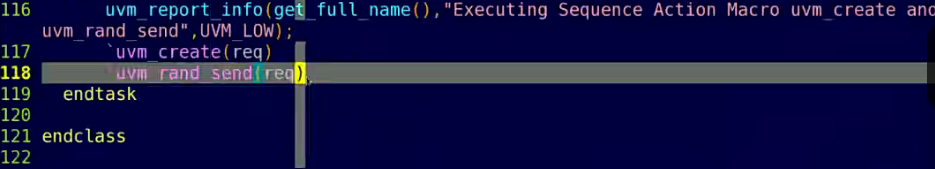

`uvm_create(req)

`uvm_rand_send(req)

// 方式4

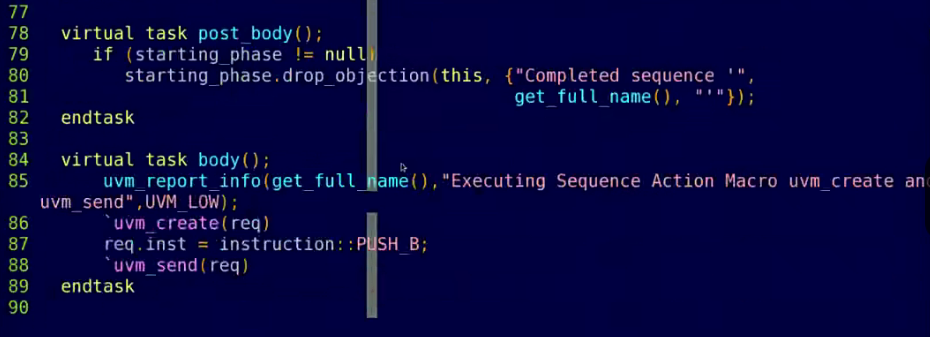

`uvm_create(req)

req.inst = tr::push B;

`uvm_send(req);

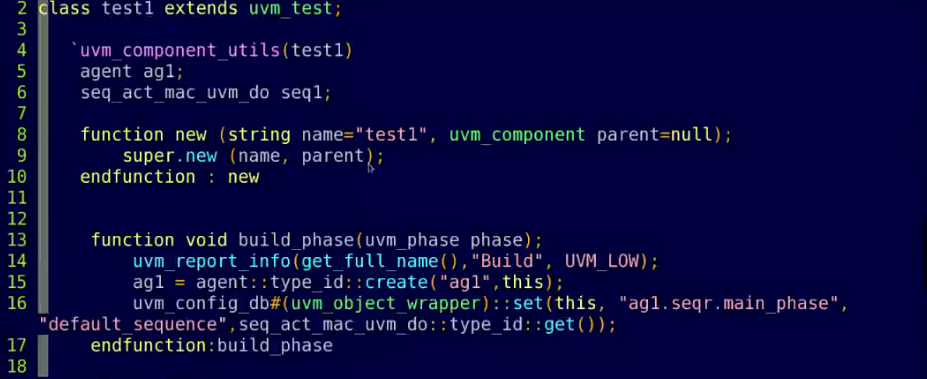

test1

- 使用uvm_config_db设置default sequence

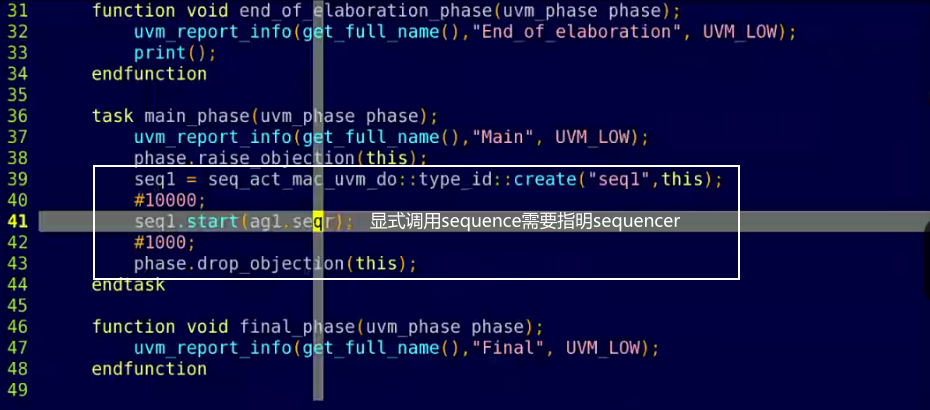

test2

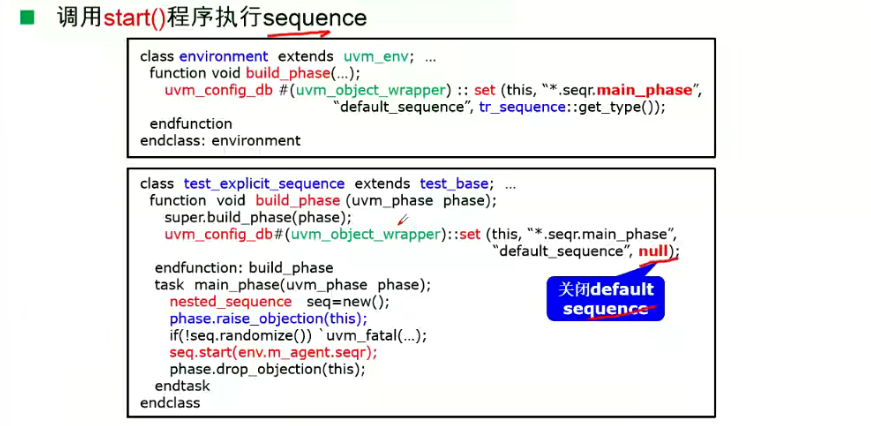

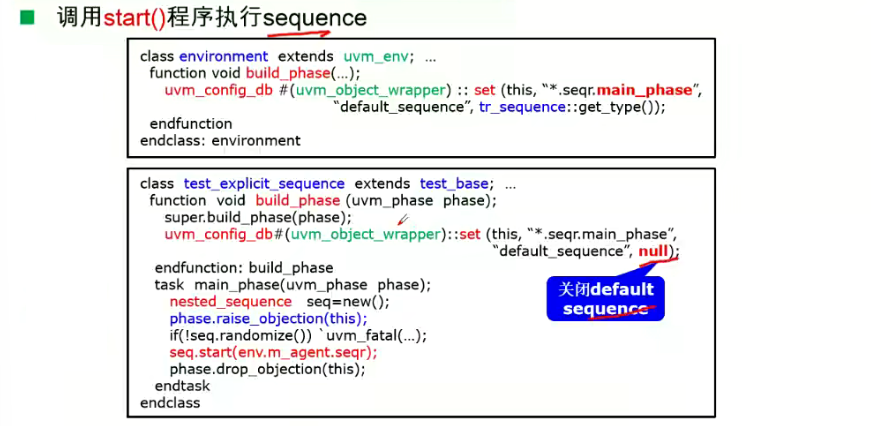

- 显式调用sequence的start函数

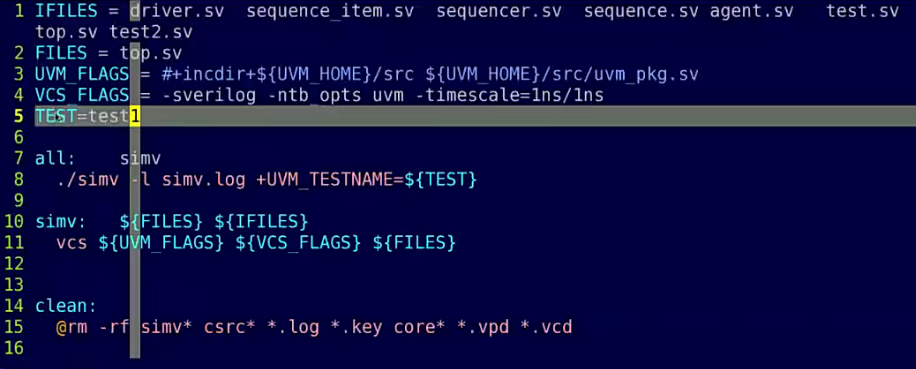

Makefile