异步FIFO设计

同步FIFO REVIEW

- 方法1:使用计数器判断空满

- 方法2:使用扩展一位的地址指示空满,读写指针最高位不同,剩余的位都相同,表示满了;读写指针相等,表示空

异步FIFO

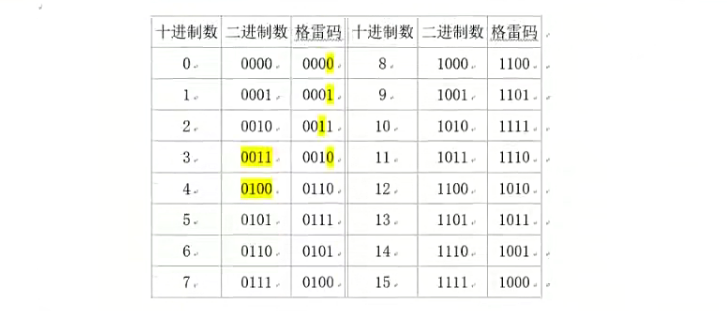

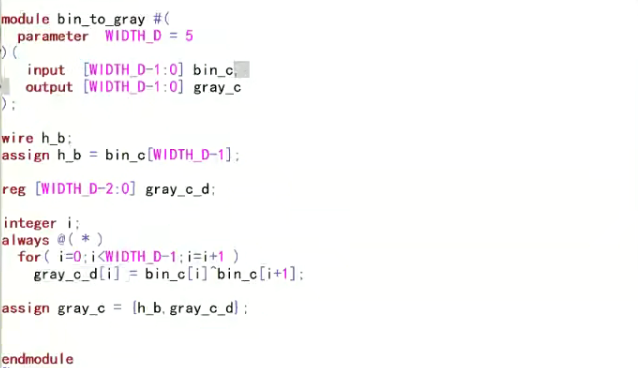

格雷码产生

- gray_code = data ^ (data >>1)

- 相邻两个数之间只有一个bit发生变化

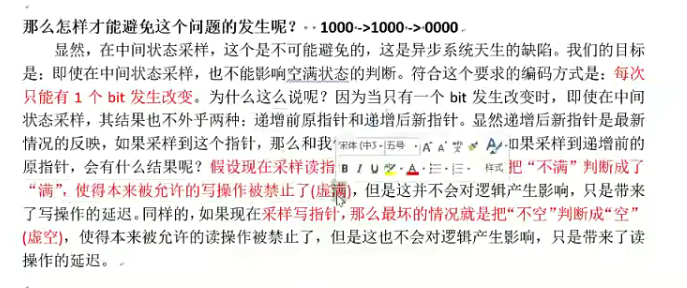

异步FIFO原理

- 读写时钟不一致

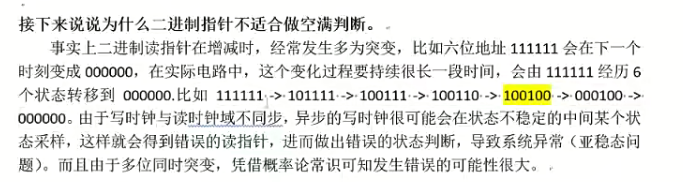

- 使用地址扩展的方式判断空满

- 两个时钟域,所以存在跨时钟域的问题,所以使用gray码,相邻两个数之间只有一个bit发生变化,发生跳转的时候只有1bit发生变化

- 产生空满信号,需要比较地址指针,指针存在不同的时钟域,所以需要进行跨时钟域的处理,先将地址指针转变为格雷码之后,进行打两拍进行同步

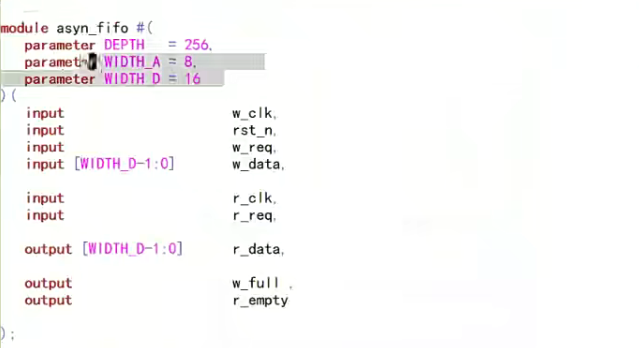

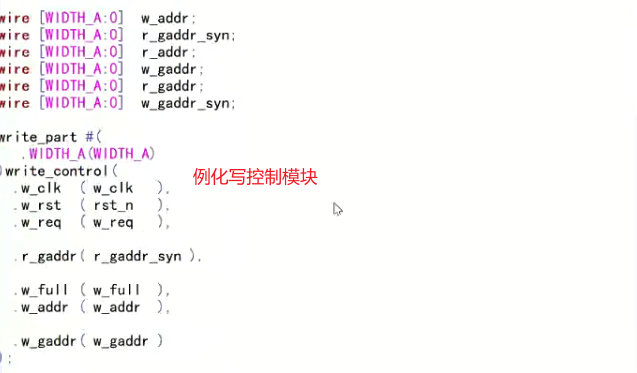

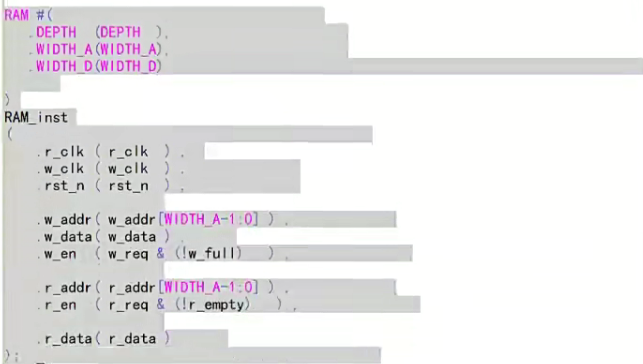

RTL

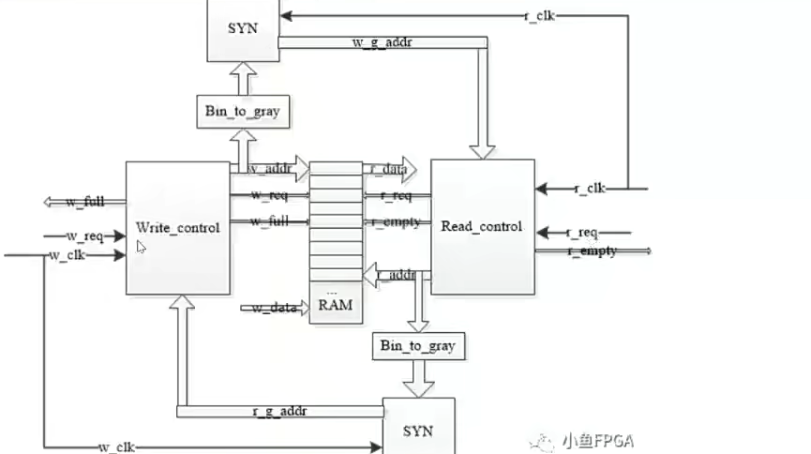

异步FIFO包含

- syn - 两级同步器

- bin_to_gray - 二进制数转gray码

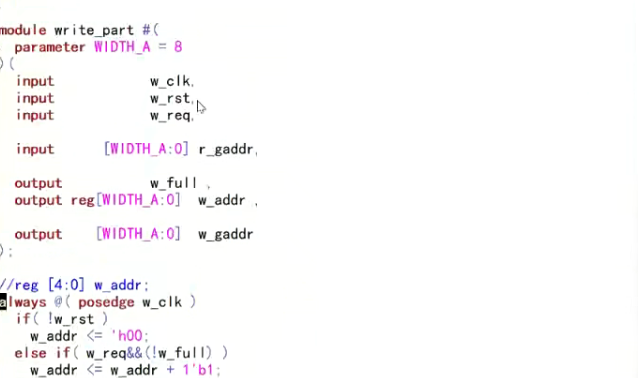

- write_ctrl - 写控制模块,产生满信号

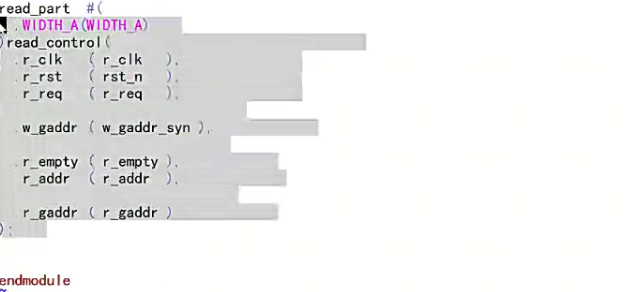

- read_ctrl - 读控制模块,产生空信号

- RAM

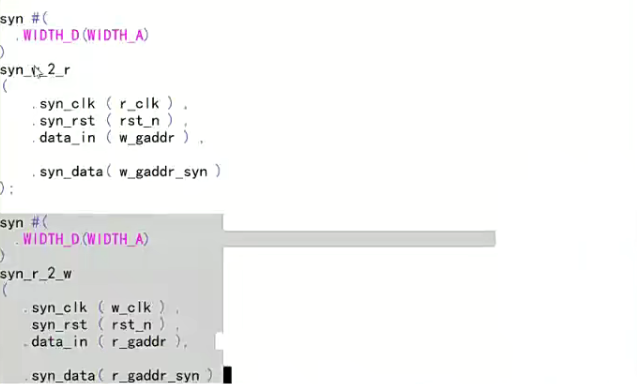

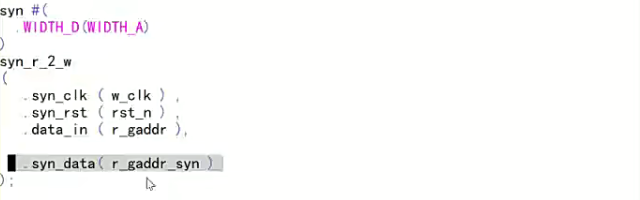

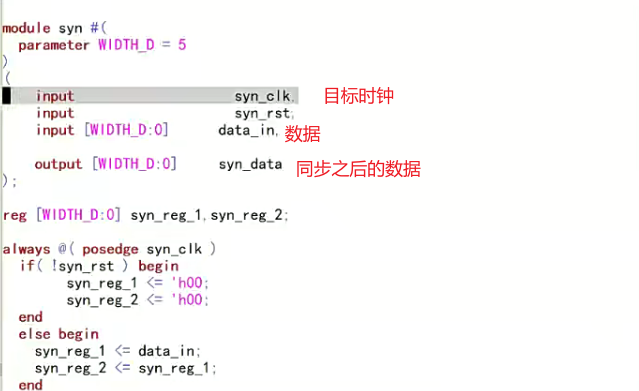

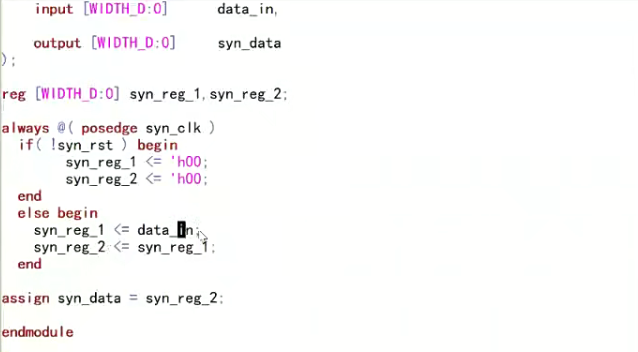

两级同步器

bin_to_gray

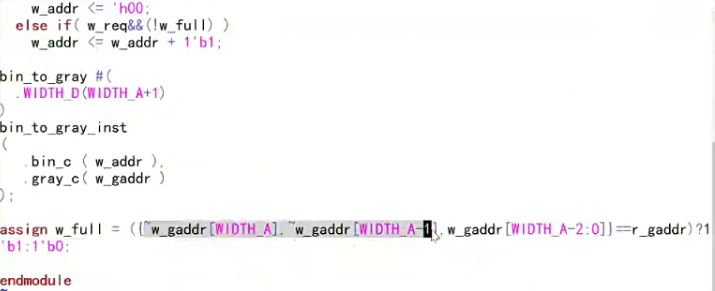

写控制

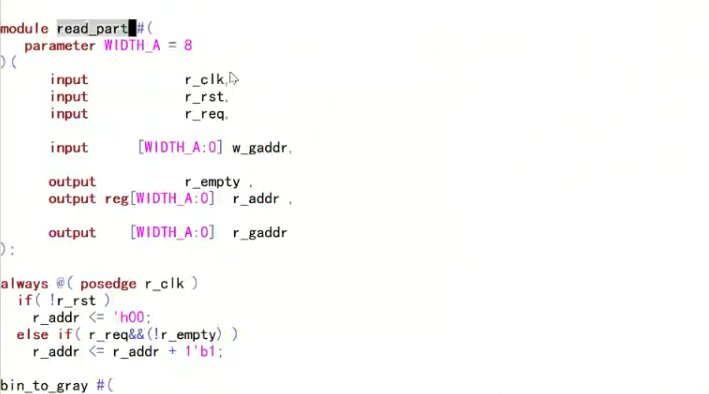

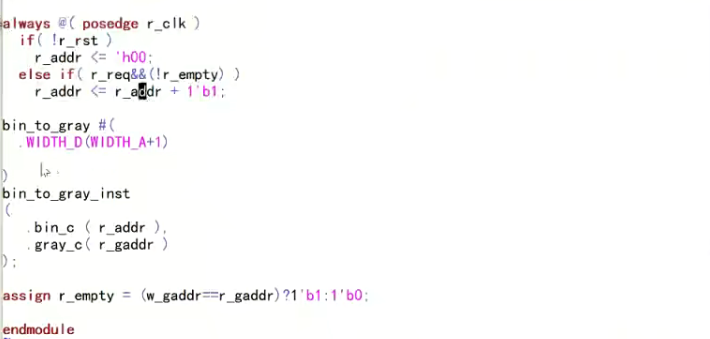

读控制端