数据类型

数据类型

内建数据类型

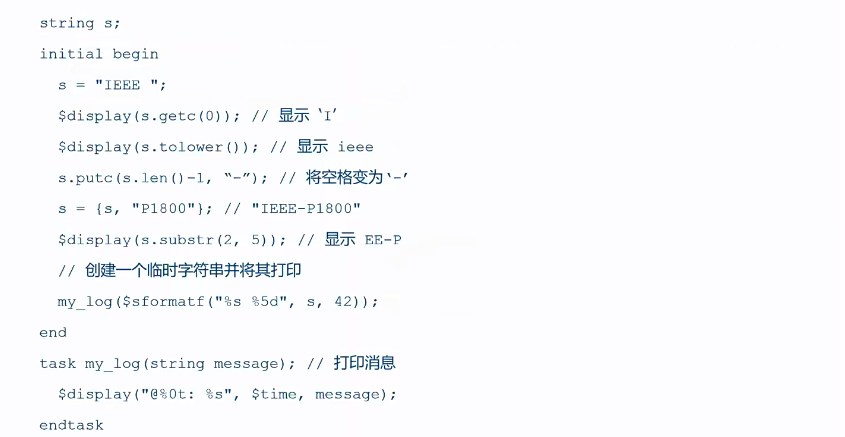

- reg - 是变量类型

- wire - 是线网类型

- system verilog - 是verilog的新版本

- system verilog文件都是.sv后缀的

- DFF/latch - 对于verilog而言都是使用的reg类型

- logic - 可以替代reg/wire

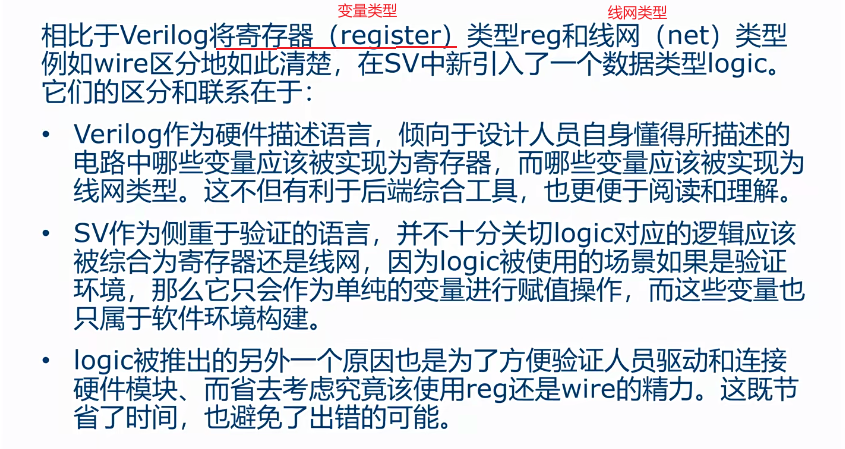

- logic是四值逻辑,bit是二值逻辑

- 验证环境中多为2值逻辑,设计环境中多为4值逻辑

- int - 二值逻辑

- integer - 四值逻辑

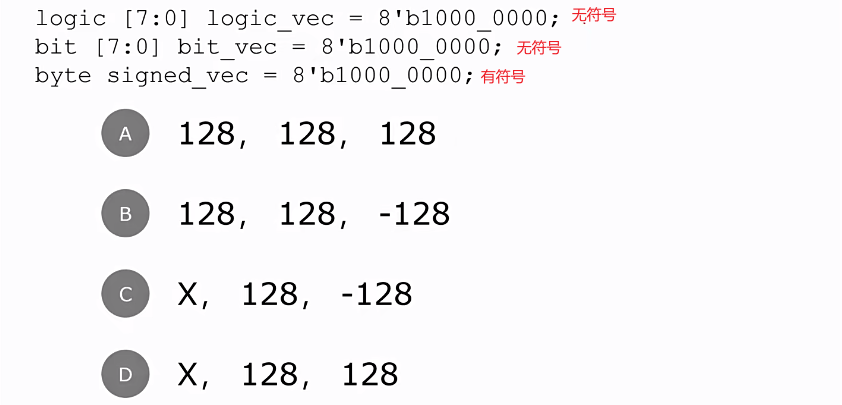

例题1

- B

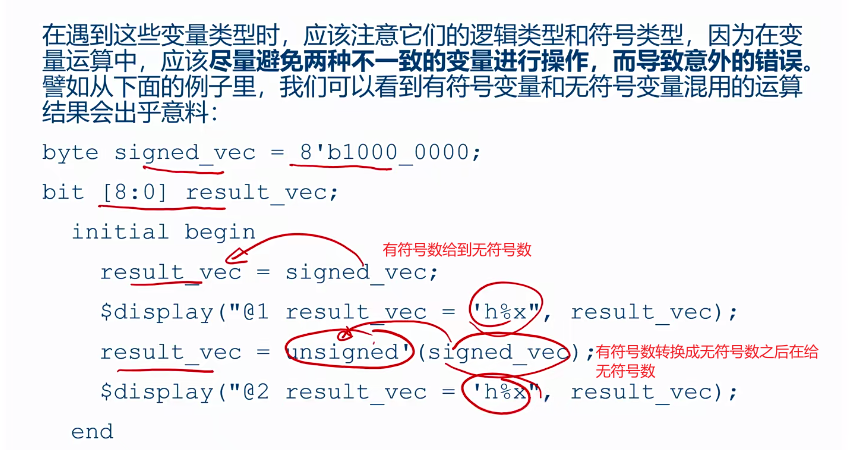

例题2

- 有符号数赋值给为无符号数,位宽不够会扩展符号位

- 有符号数转变为无符号数,位宽不够会高位补0

byte signed_vec = 8'b1000_0000;

bit [8:0] result_vec;

initial begin

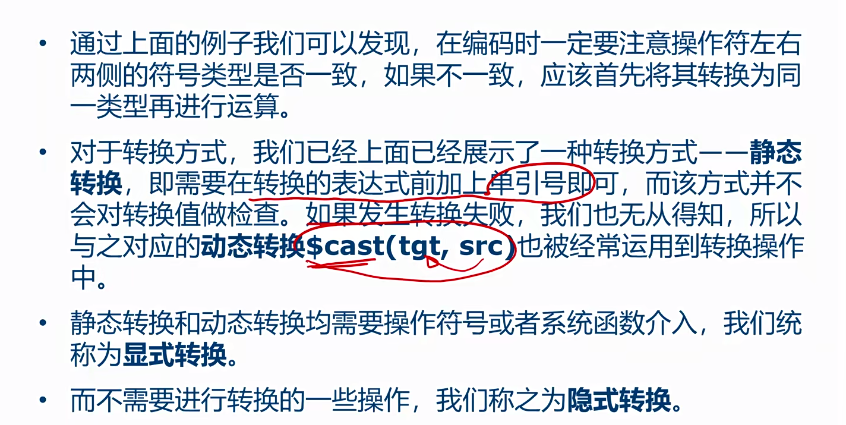

// 静态转换方式,目标类型+单引号

// 在编译的时候就会完成检查

result_vec = unsigned'(signed_vec);

end

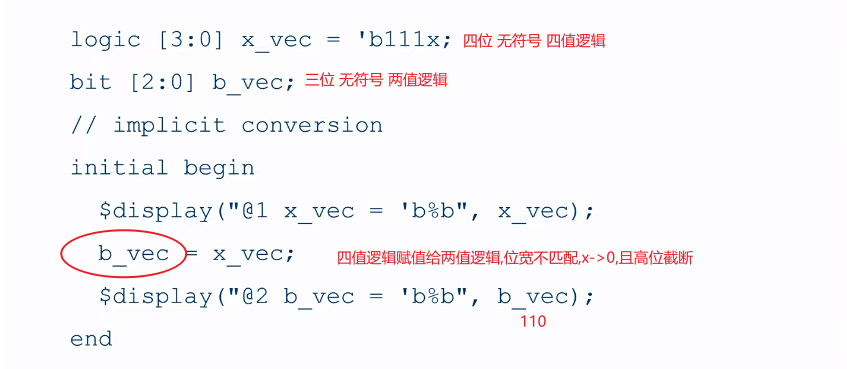

例题

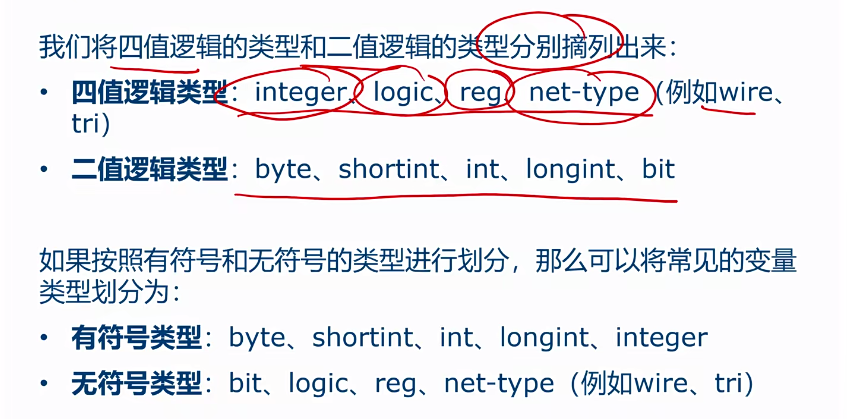

- 四值逻辑的x或者z转到二值逻辑的时候变为0

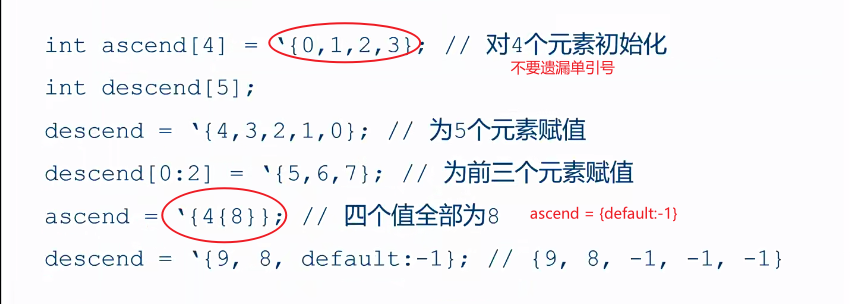

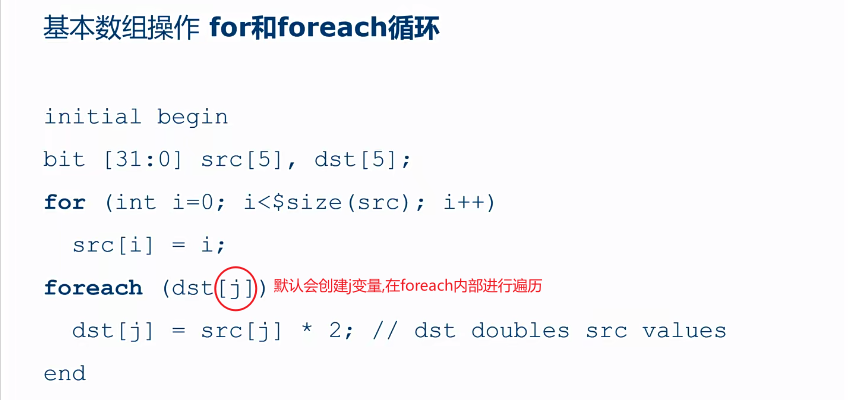

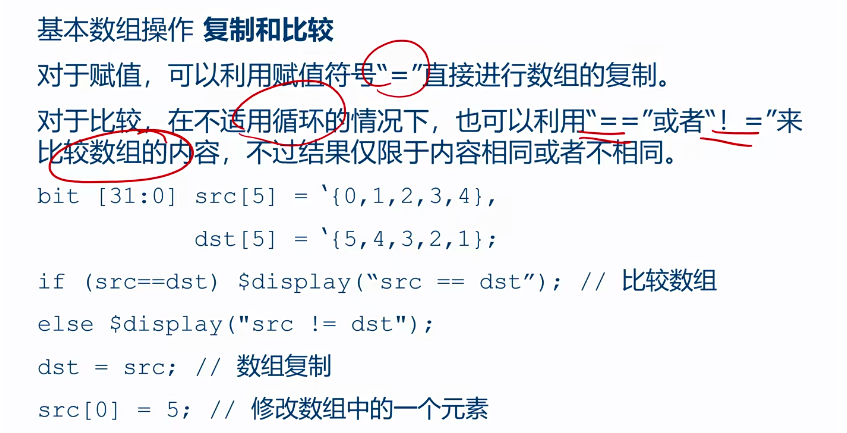

定宽数组

- 数组维度放在数组名右侧和左侧是有区别的

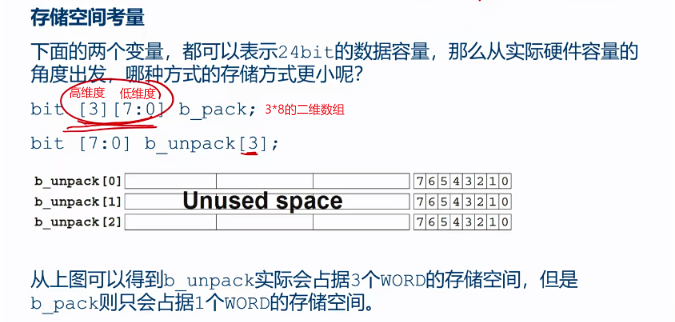

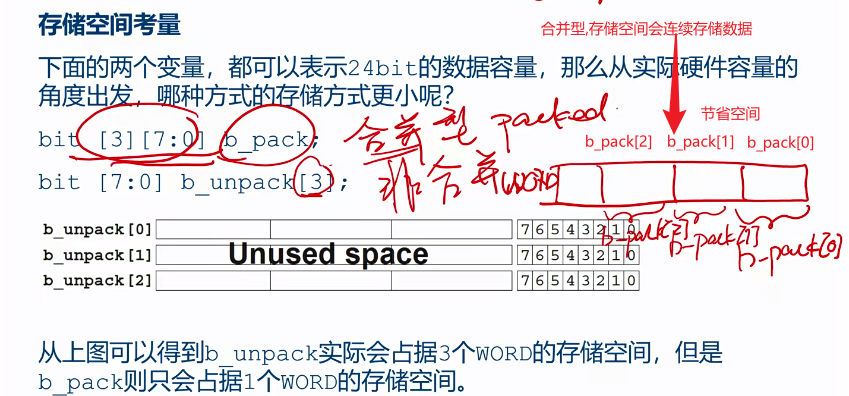

- 数组维度写在数组名左边 - 合并型(pack),数组维度有写在数组名右边 - 非合并型(unpack)

- 数组维度分别写在数组名两侧,右侧为高维度,左侧为低维度

- logic是四值逻辑,在软件上要用两位进行存储,l_pack需要48bit进行存储,需要两个word

- unpack形式 - 低维度连续存储,高维度分开,所以需要3个word

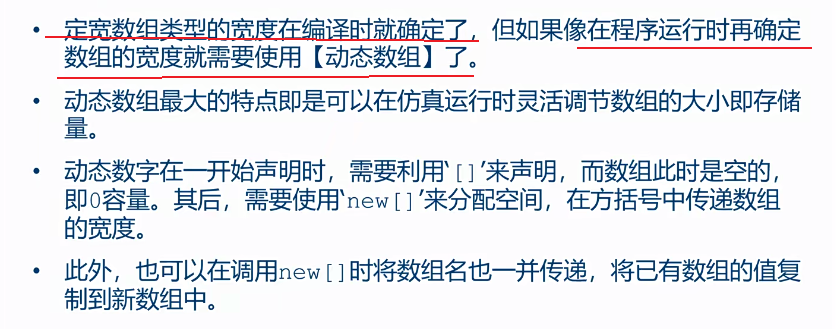

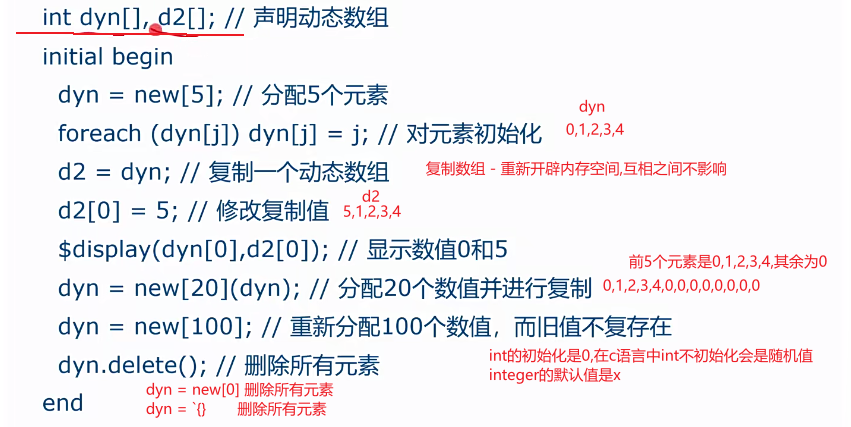

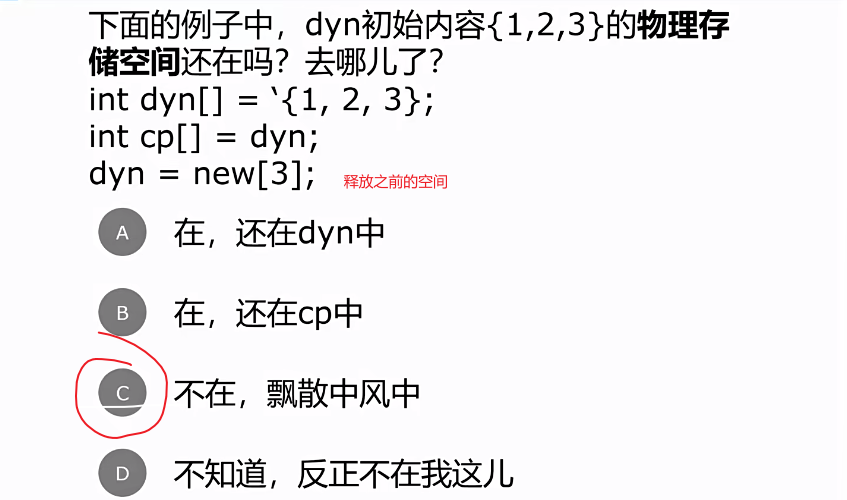

动态数组

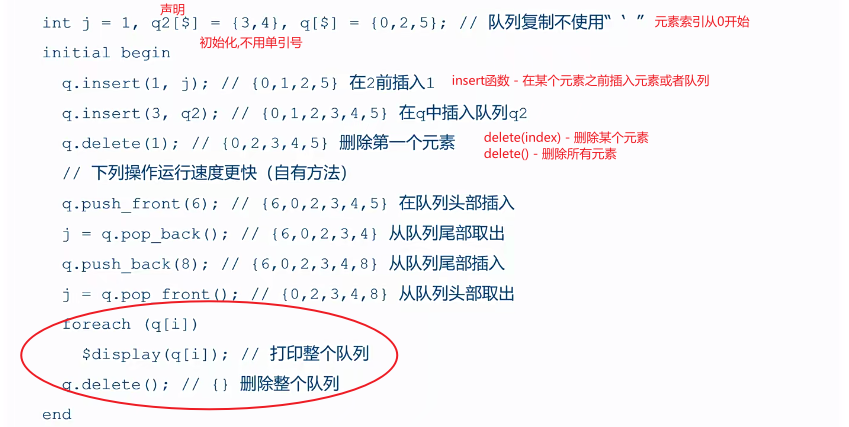

队列

- push_back() - 从后向前写数据

- pop_front() - 从前面删除

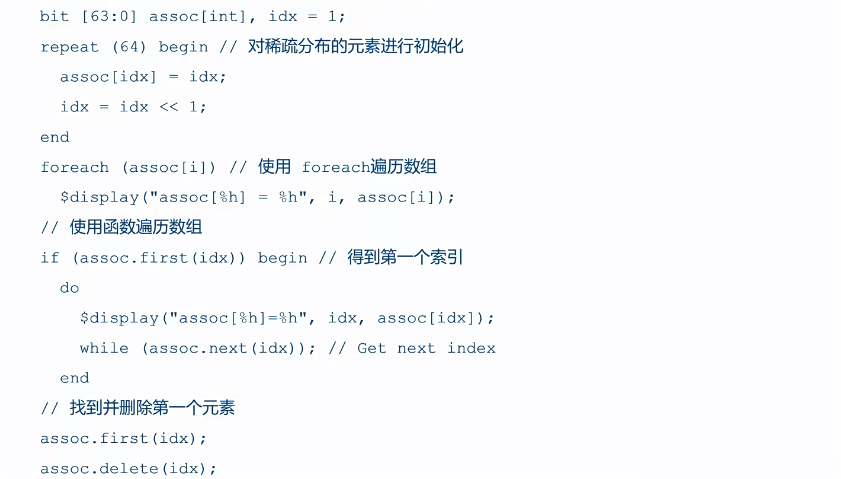

关联数组

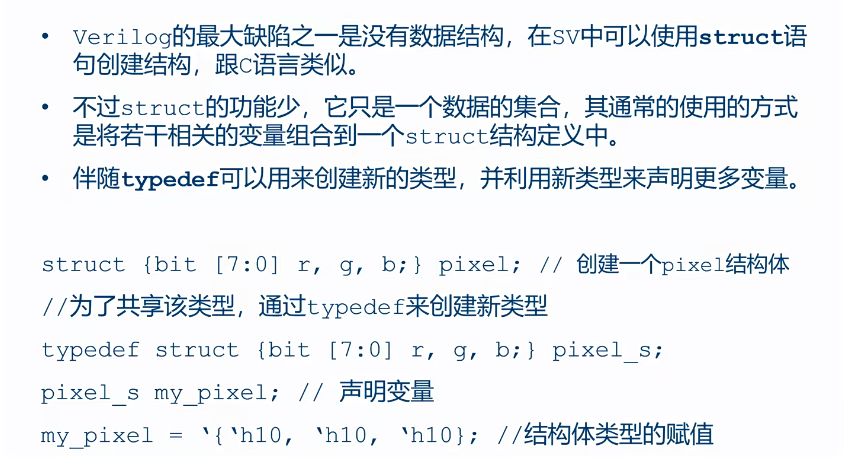

结构体

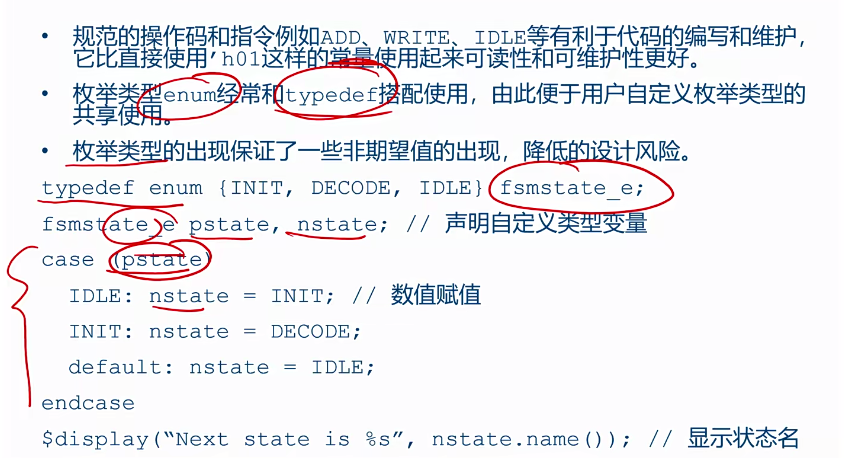

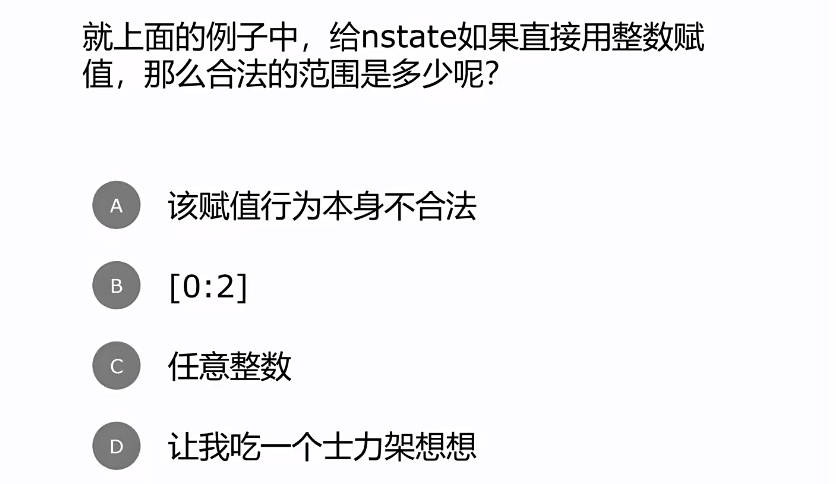

枚举类型

- 枚举类型可以赋值给整型变量,整型不能直接赋值给枚举类型

- 整型赋值给枚举类型需要进行类型转换

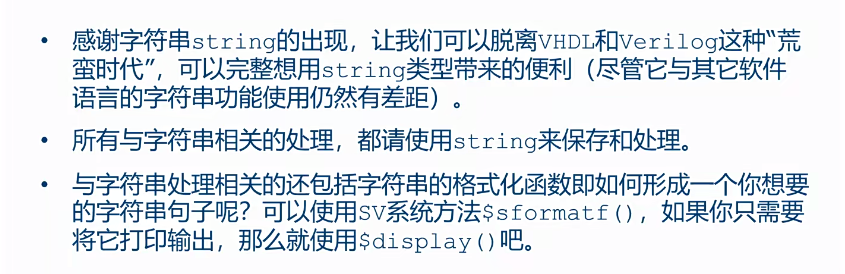

字符串