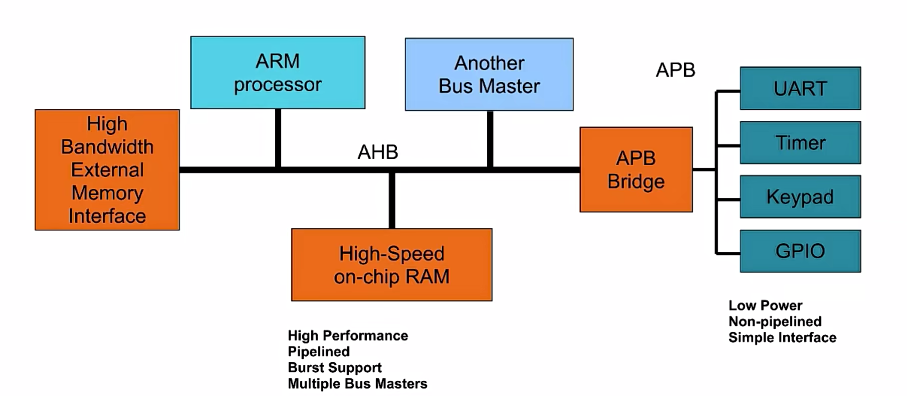

AHB协议

AHB System

- 外部的memory比如SD card或者是DDR,需要在总线线上挂载相应的接口进行访问

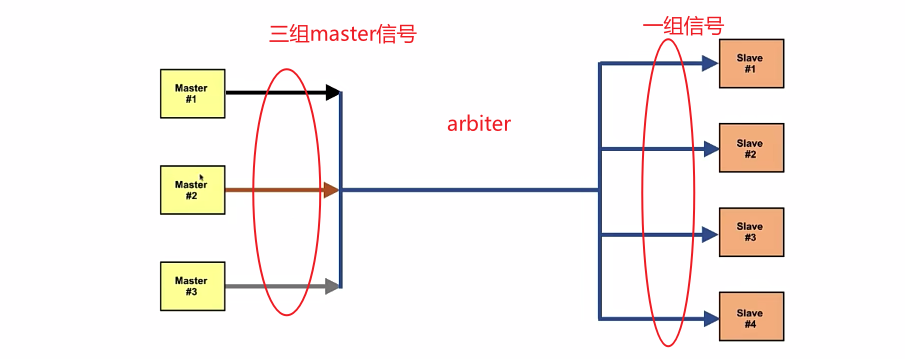

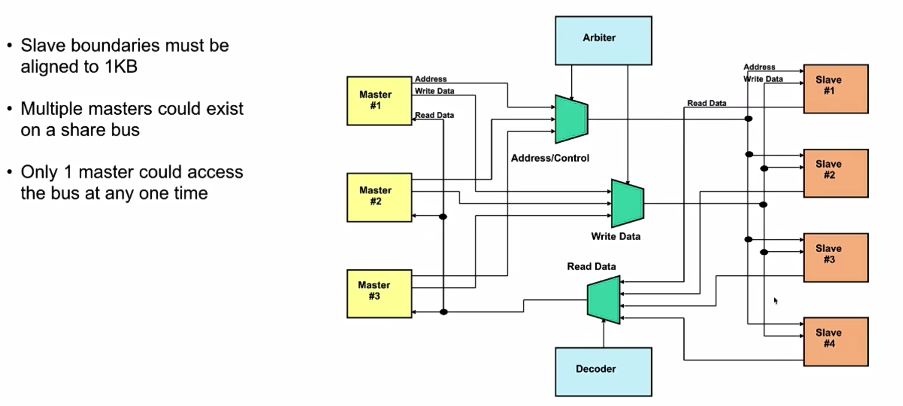

AHB2

- AHB2可以有多个master,每个master都会发出相应的控制信号,三个master会发出三组总线信号,对于slave而言,会share一组总线,所以只有一组master的控制信号可以给到slave,需要一个仲裁器,仲裁哪个master可以控制总线

- slave地址空间最最小是1KB,slave地址空间是以1KB为单位的,所以在传输过程中不能跨越1KB的地址边界

- 仲裁的方式:可以采用轮询的方式进行仲裁还可以根据master的优先级进行仲裁

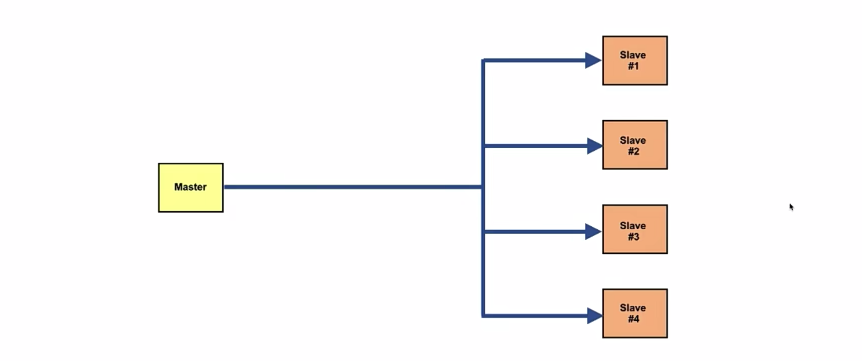

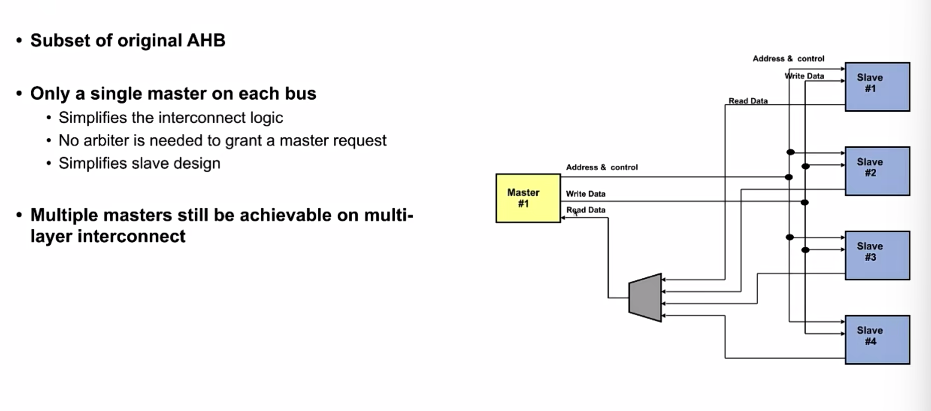

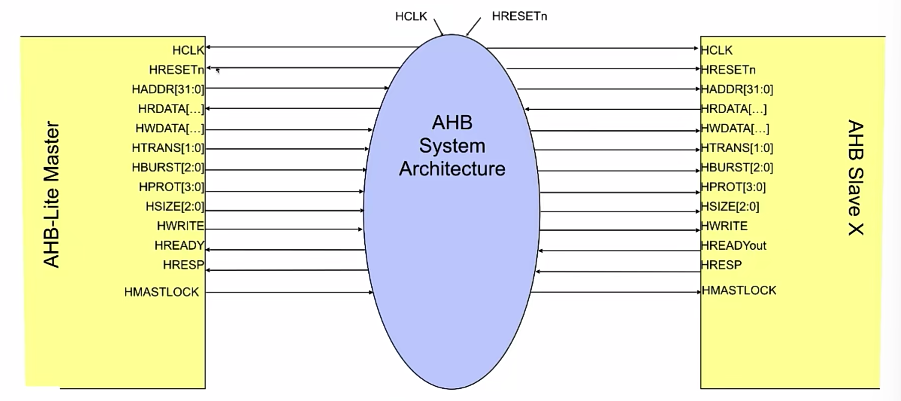

AHB-Lite

- 只有一组总线,针对于单个master设计的BUS

- 系统也是可以支持多个master

- 不需要进行仲裁,简化设计

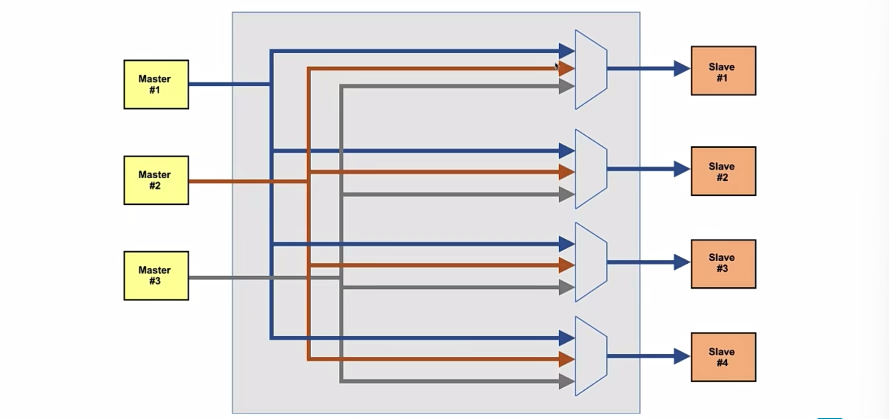

AHB-Lite Strcture 1

- 多个master发送控制信号和数据,需要进行选择

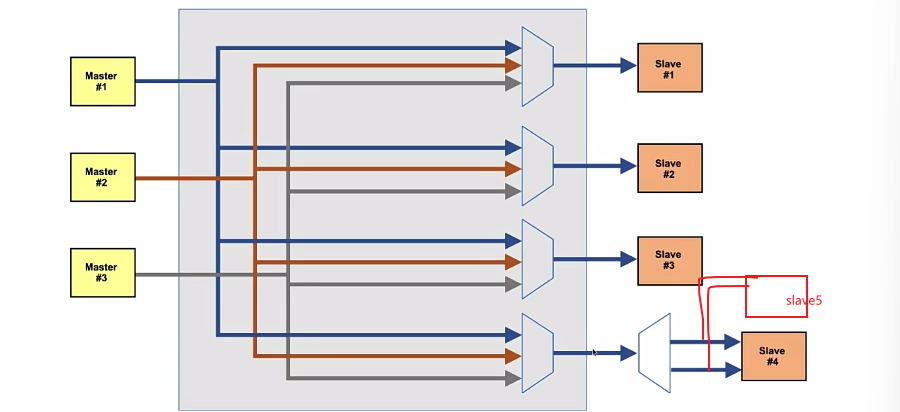

AHB-Lite Strcture 2

- master3有私有的slave4,master3访问slave4可以不经过选择,所以访问私有slave的速度快

AHB-Lite Structure 3

- 多个slave可以共享一组接口

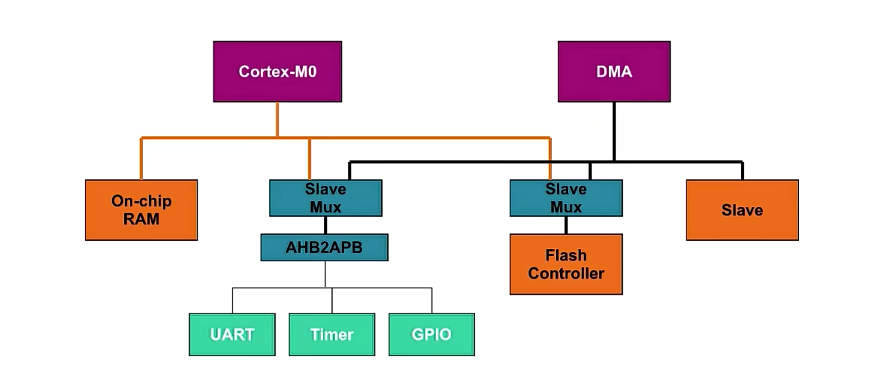

Typical Multi-layer example

AHB操作

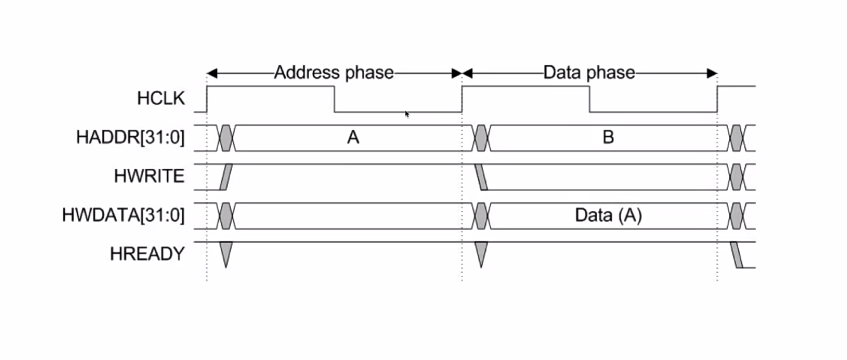

AHB Write

AHB Read

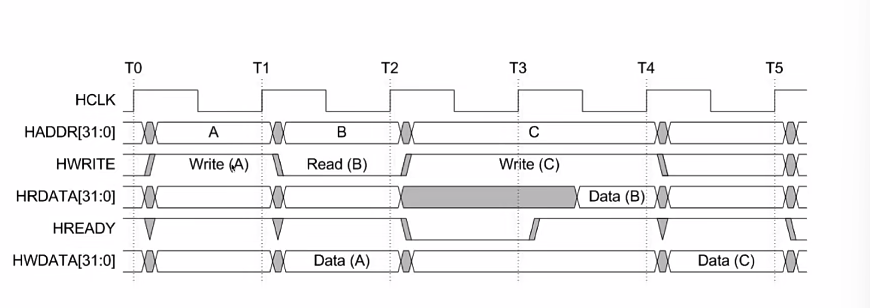

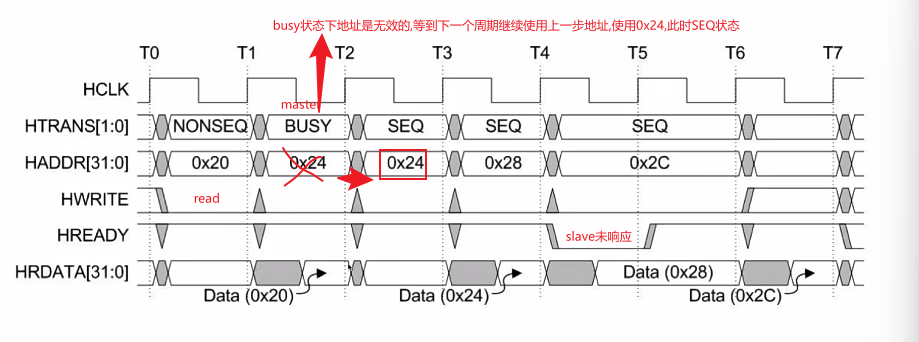

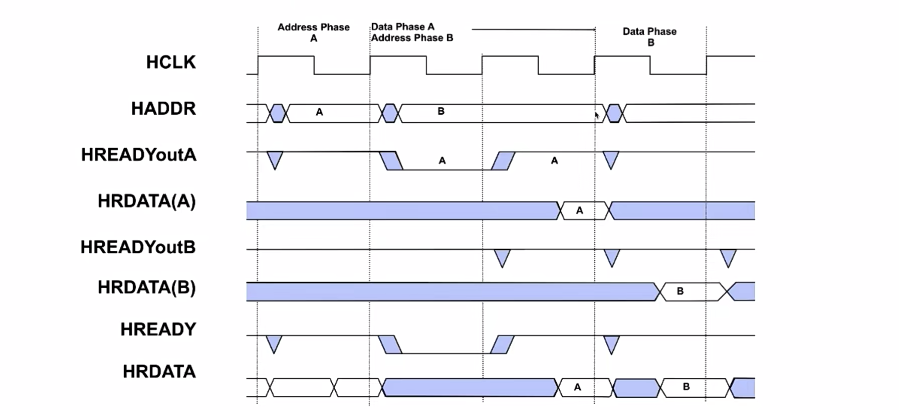

Multiple Transfer

- 支持pipeline操作

- hready拉低表示slave不能及时进行响应

AHB-Lite Interconnection

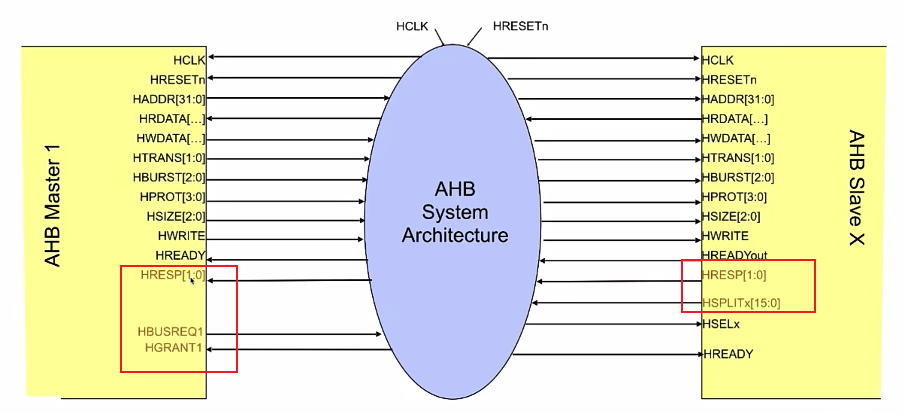

AHB2 Interconnection

- HBUSREQ和HGRANT - 一组握手信号

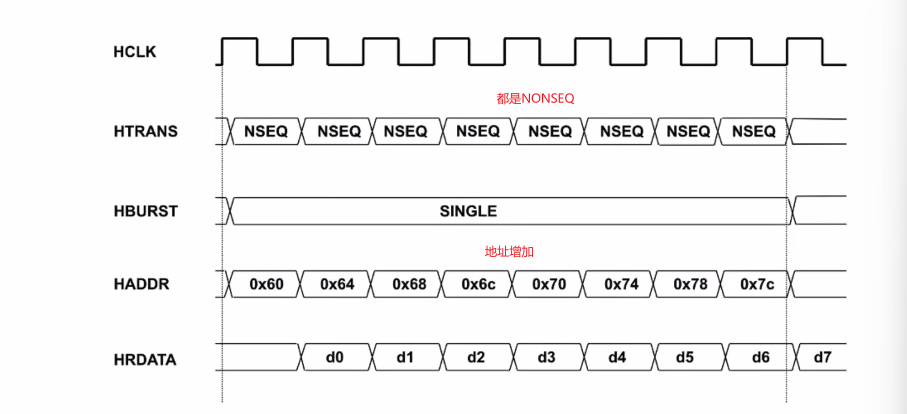

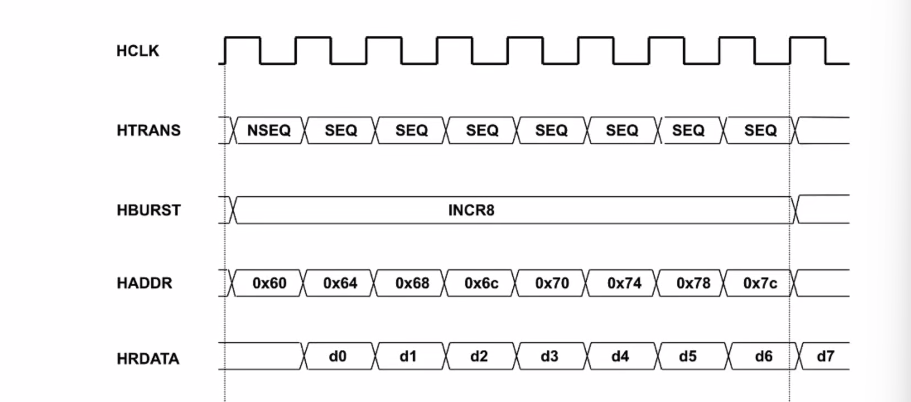

Htrans Transfer Type

- NONSEQ - 发送一笔数据或者是burst传输的第一笔传输

- SEQ - burst传输的除第一笔数据之外的访问

Transfer Type Example

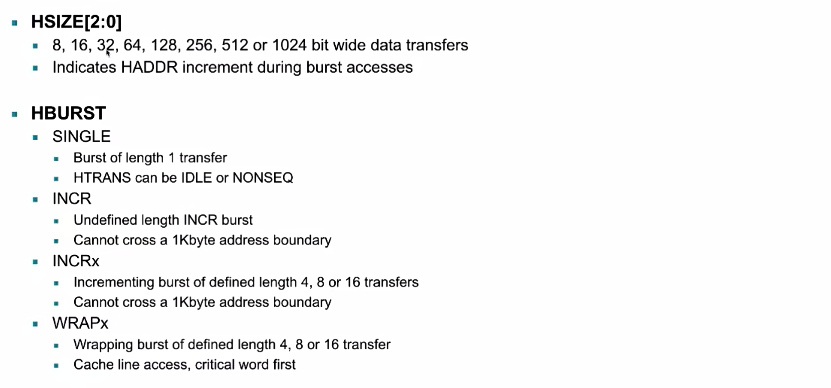

Hsize and Hburst

- hsize - 表示每笔传输的位宽

- hburst - 表示传输类型single/busrt传输

- burst传输又分为:INCR传输\WRAP传输

- burst传输的时候不能跨越1KB地址边界

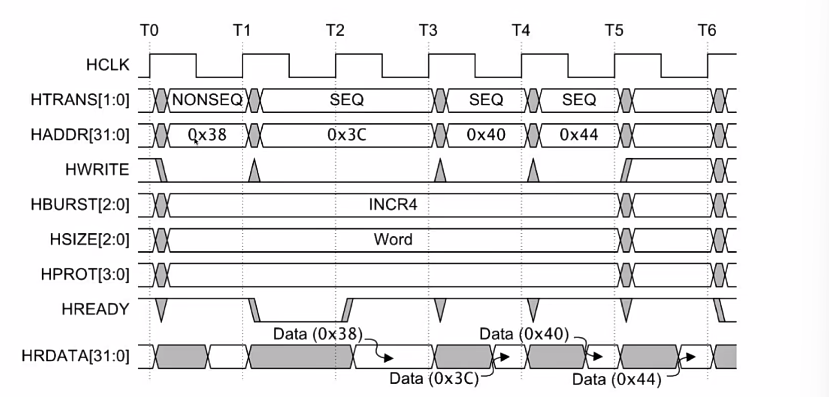

INCR4

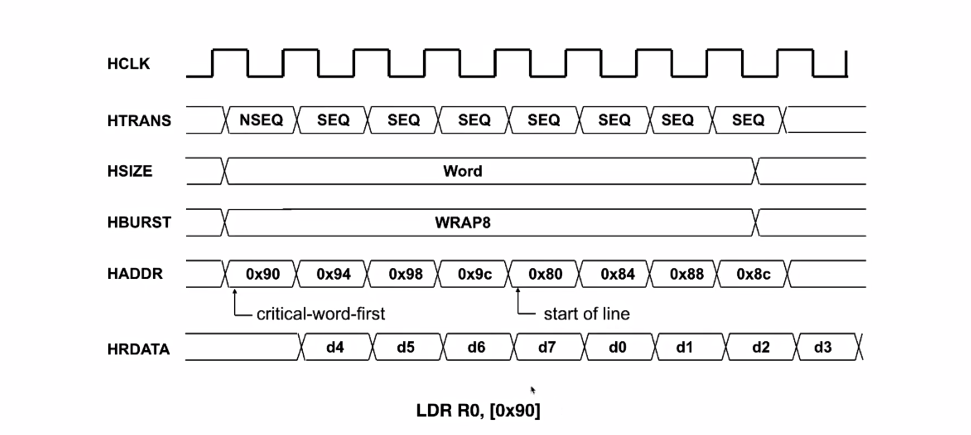

WRAP8

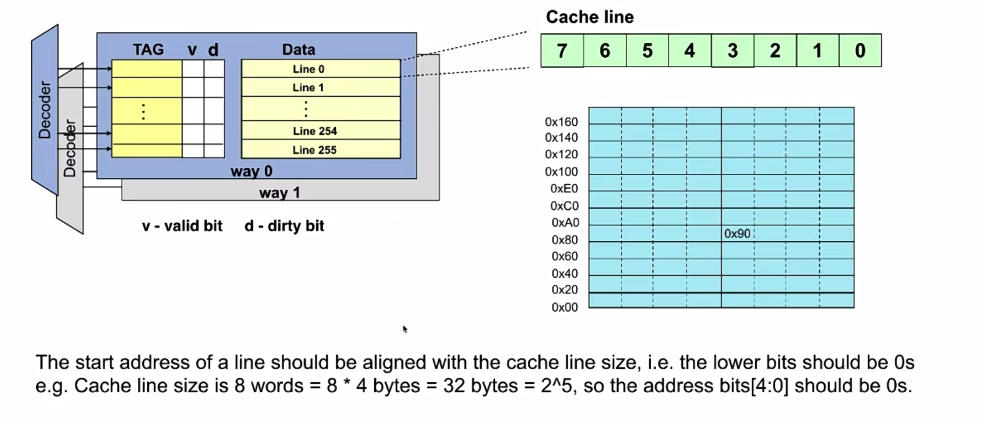

How to caculate the start address of a line

Single vs Burst

Single

Burst

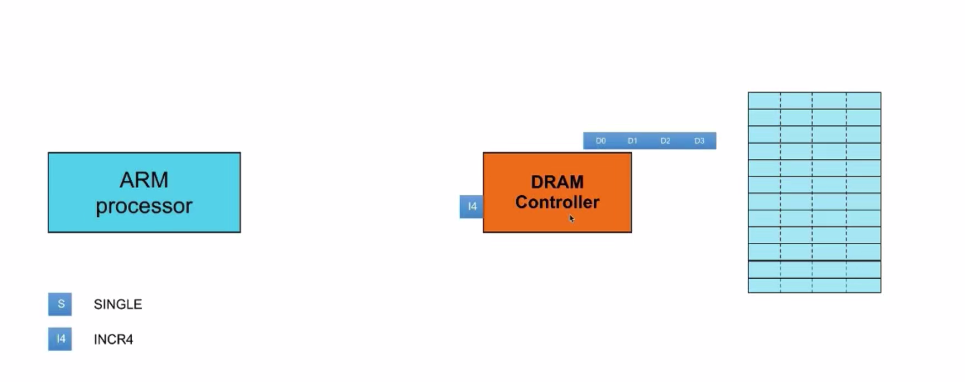

case

- CPU发送4beat single access,single传输,DRAMC不知道下一个地址是多少,所以CPU再发送一个single access,DRAMC再执行一次

- CPU发送INC4传输,DRAMC知道起始地址,就可以知道四个数据的地址和数据大小,DRAMC可以直接读取四个数据存放再缓存中,然后给到CPU

- 使用Burst传输能够提高效率,减少对于memory的访问次数

Hresp slave response of AHB-Lite

- 0表示ok,1表示error

- 如果是ERROR需要持续两个周期,用于给到master进行处理,master发现transfer错误,是继续传输还是取消burst传输

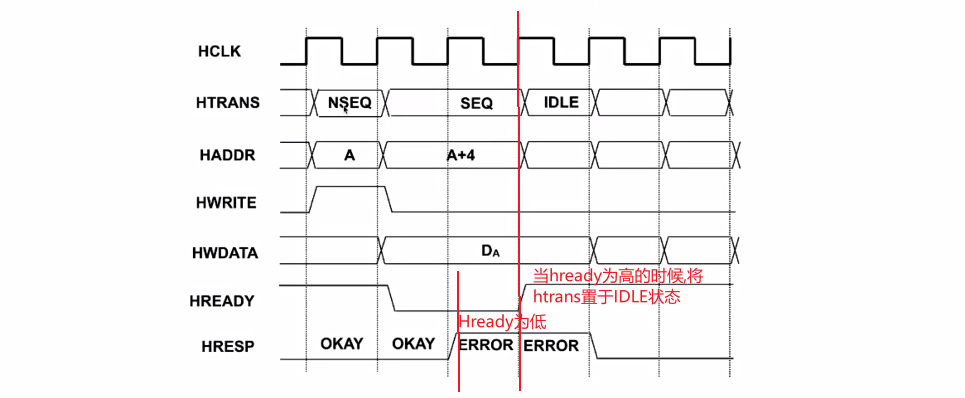

Master Terminates Current Burst

- hready拉高的时候,将htrans置于IDLE状态,就会停止A+4的busrt传输

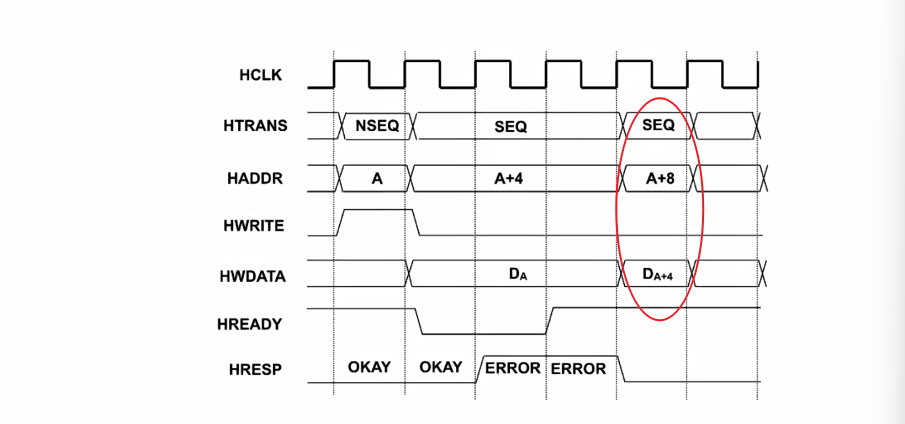

Master Continue Current Burst

Hresp slave response of AHB2

- slave返回给到RETRY信号,此时arbiter会查询其他master的优先级,优先级高的master可以获得总线的控制权

- slave返回split信号,根据轮询队列获得总线控制权,即使master优先级低,也可以得到总线的控制权

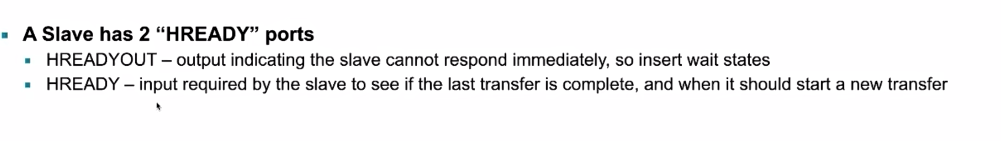

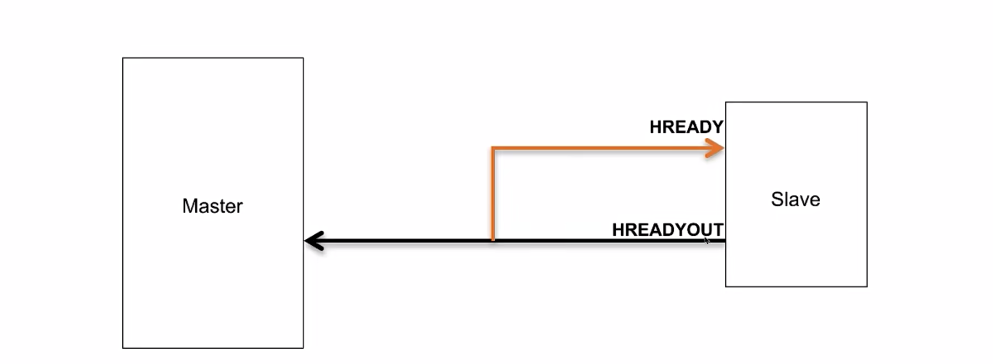

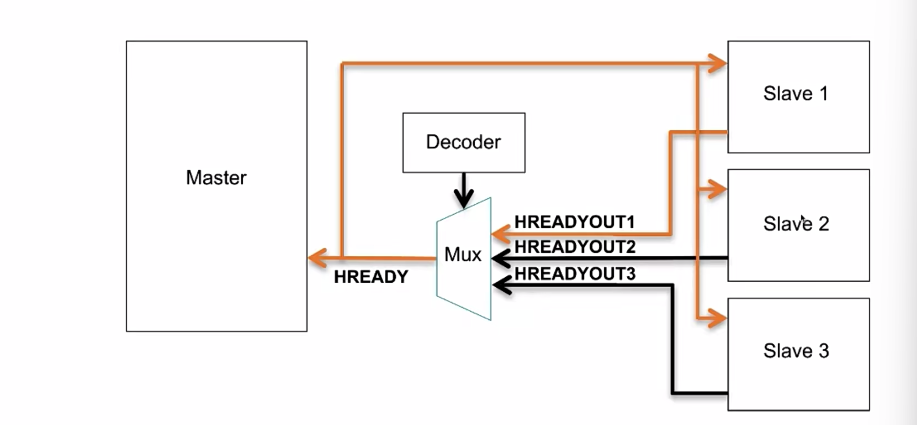

Two hready signals

Hready Connection

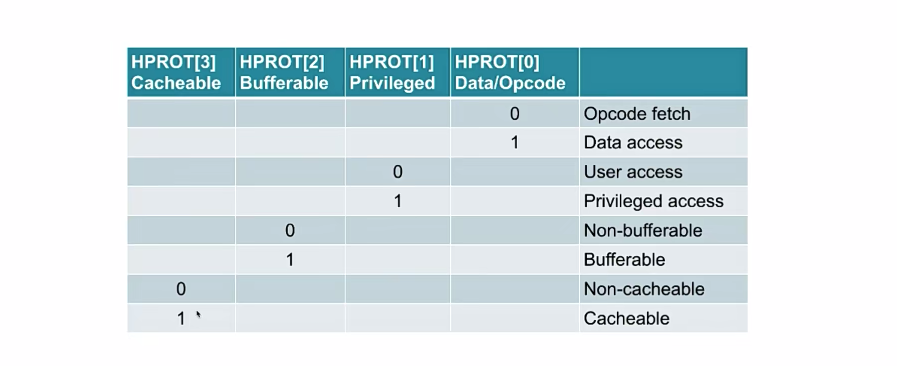

HPORT

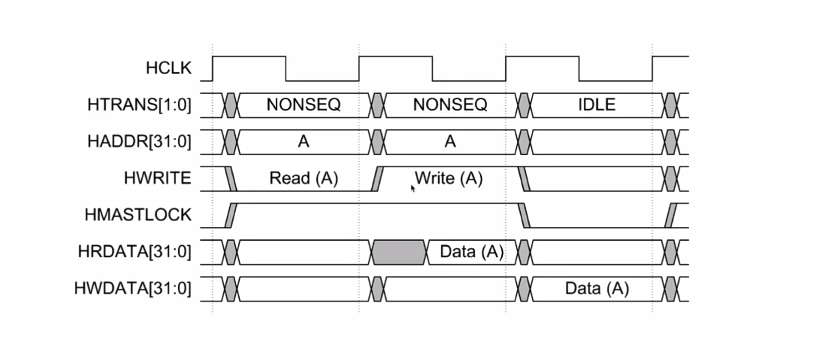

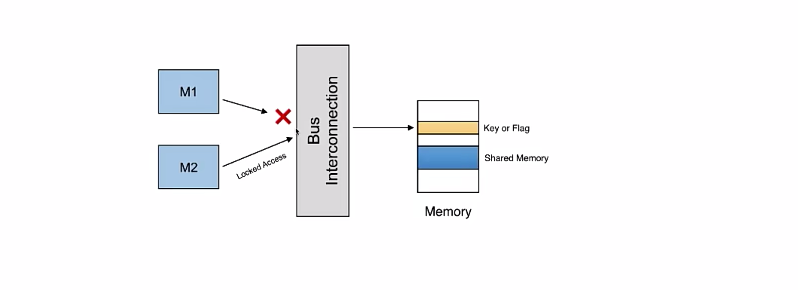

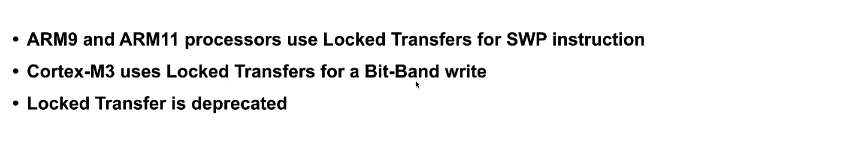

Locked Transfer

- 保证原子操作,一次操作过程中只能是读或者是写操作,不能同时进行

Locked Transfer & ARM Processor

AHB5

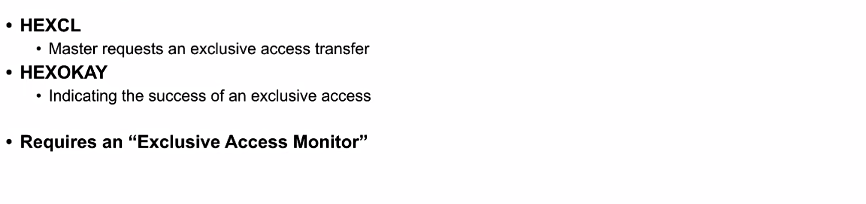

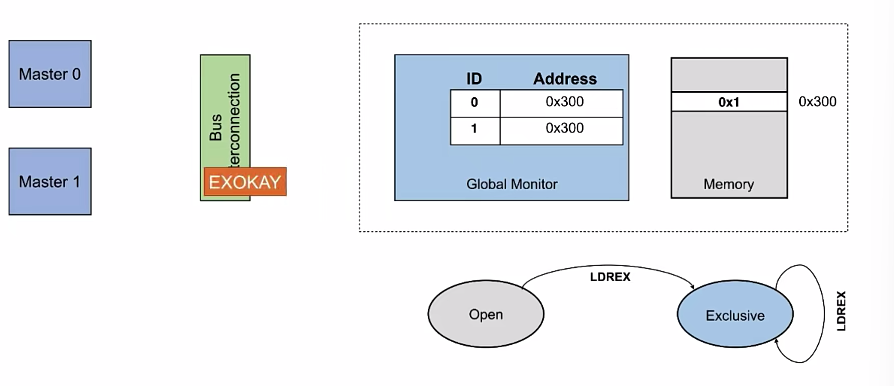

Exclusive Transfer

- HEXCL - 表示exclusive access

- HEXOKAY - 表示exclusive access操作成功

- exclusive transfer主要用于实现软件的semaphore,所以需要Exclusive Access Monitor记录access address

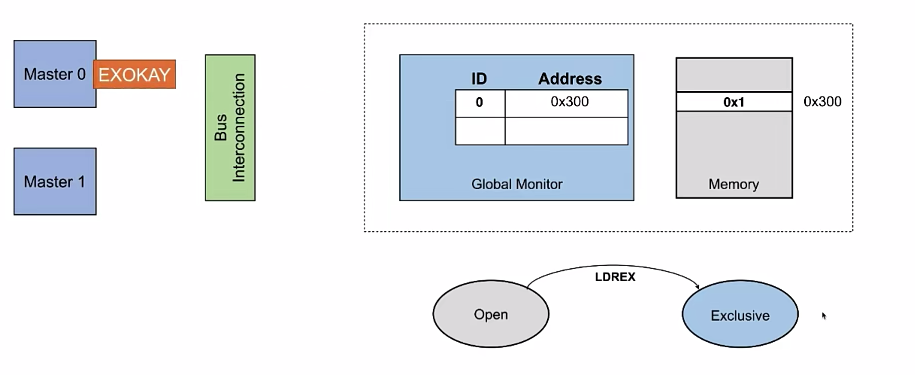

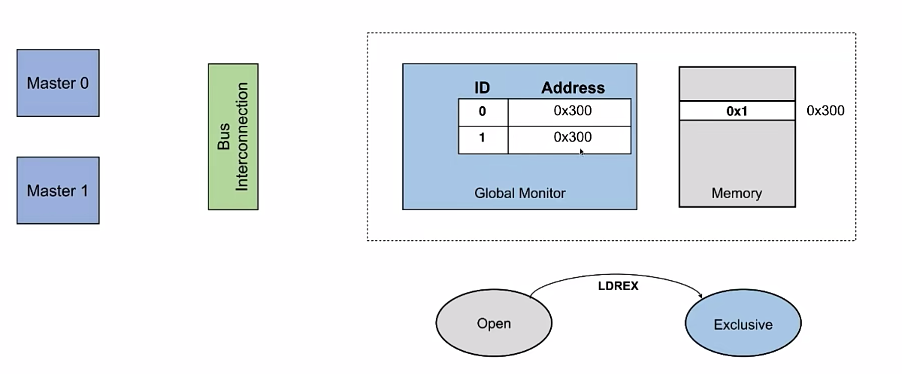

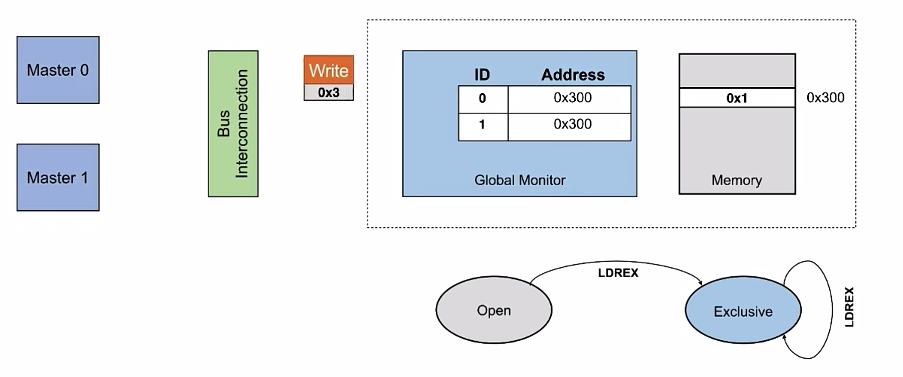

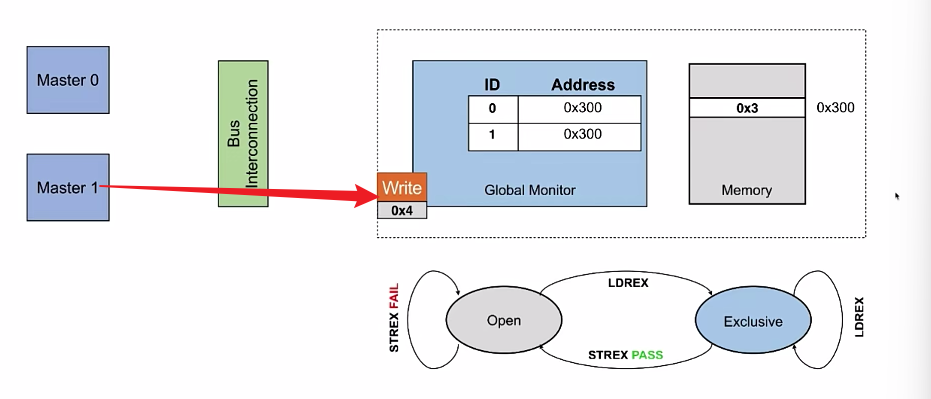

Exclusive Flow

- Master0对地址进行读操作,对于Exclusive Access,会有一个额外增加的Global Exclusive Monitor,Monitor会存储两个状态,一个是open状态,一个是Exclusive状态

- 当发起LDREX之后,Monitor会转到Exclusive状态,Monitor会返回EXOKAY给到Master0

- Master1再去访问该地址的时候,Monitor还会记录该地址的Exclusive状态

- Master0发起一个写操作,可以将数据写到地址对应的mem中,Monitor将该地址状态切换为open状态

- Master1发送一个write操作,因为Monitor处于open状态,write操作会失败,不会更新地址的值

Exclusive读和写往往是成对出现的,只有再该地址处于Exclusive状态,才能进行读和写,所以Exclusive写之前需要用LDREX命令,将地址转换到Exclusive状态,再对其进行写

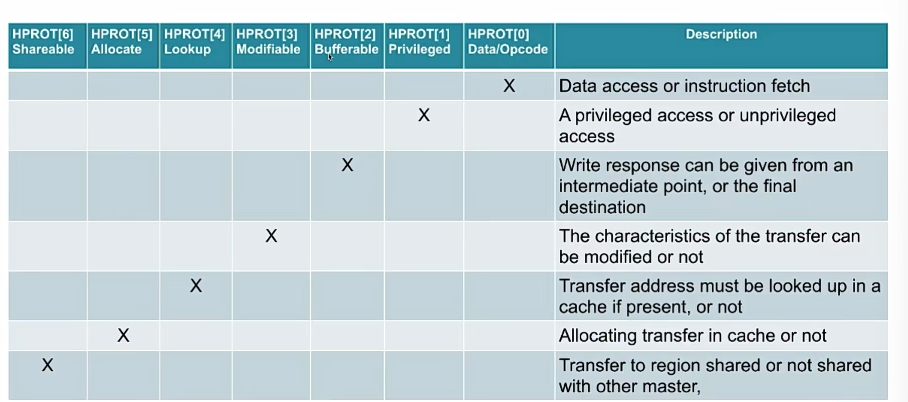

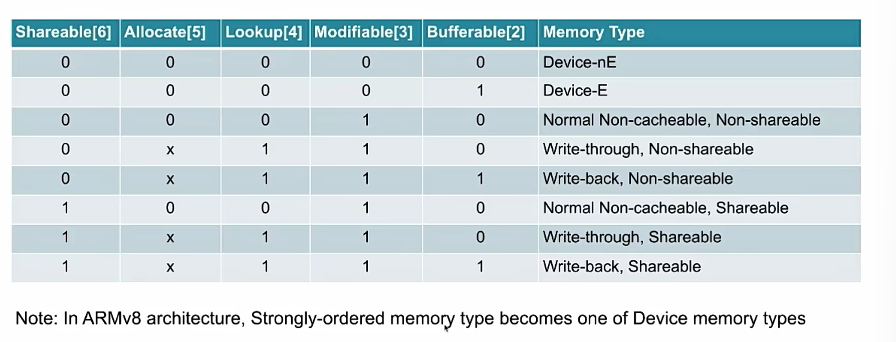

HPORT

- modified - 表示可以更改传输属性,两个INCR4传输,可以合并成一个INCR8

- look up - 表示能否再cache中进行查找,可以再cache中查找的话,如果cache中有对应的数据,就从cache中取值

- allocate - 发生cache miss的时候能否分配cache line

- shared - 表示是master共有的还是独有的

- memory属性:normal memory\device memory\strongly-ordered memory

- nE - 必须将数据直接更新到目标地址空间

- E - 可以将写的数据存储到buffer中,立即给cpu response,不用立即将数据更新到目标地址空间

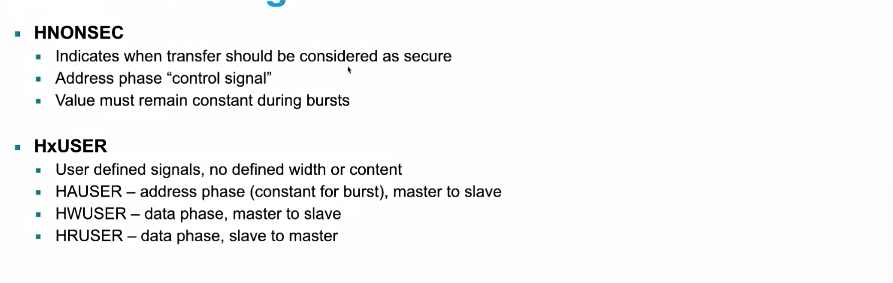

Other AHB5 signals

- HxUSER - 用户信号

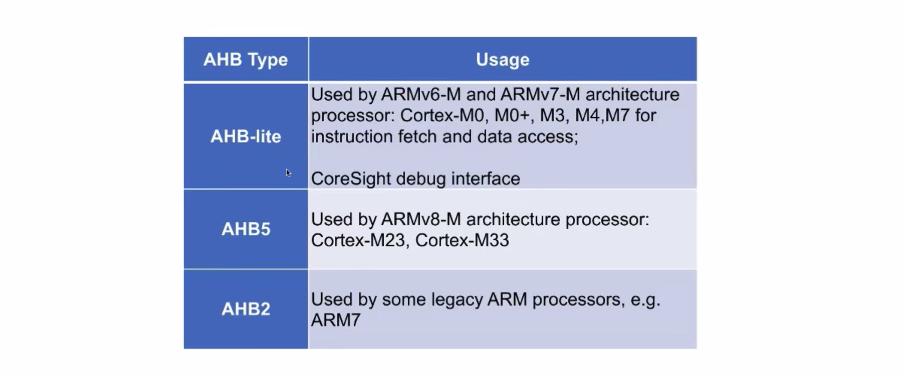

AHB in ARM Processors

AHB behavior of Specific ARM processors

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· .NET Core 中如何实现缓存的预热?

· 三行代码完成国际化适配,妙~啊~

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

2023-01-09 02-RTL代码分析思路

2023-01-09 01-Verilog基础_1