Scan Synthesis Practice

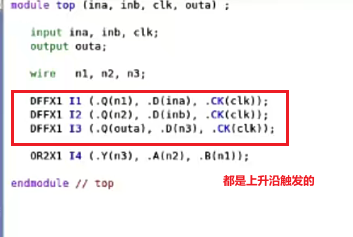

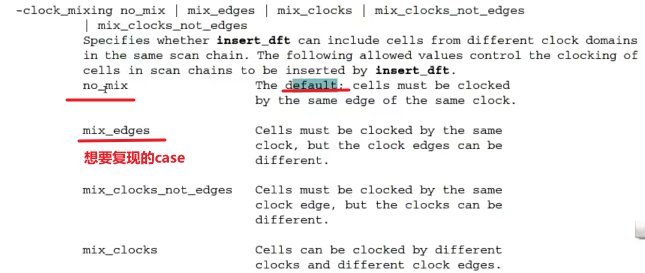

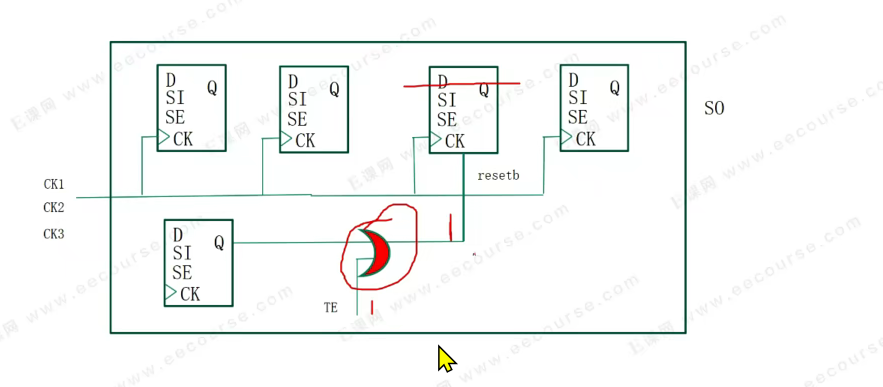

不同上升沿触发器如何进行scan chain

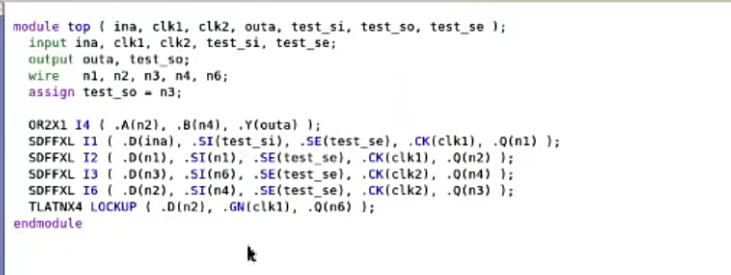

DFT实例

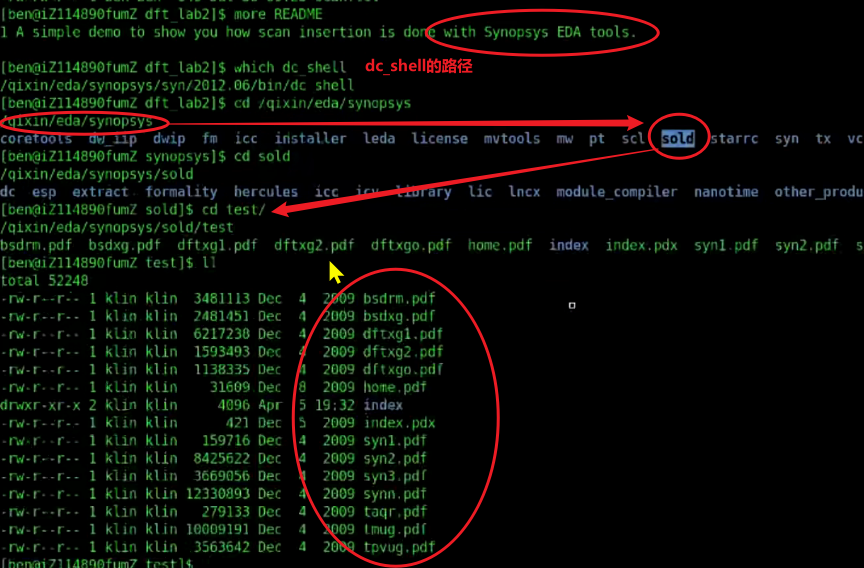

Synopsys 工具文档

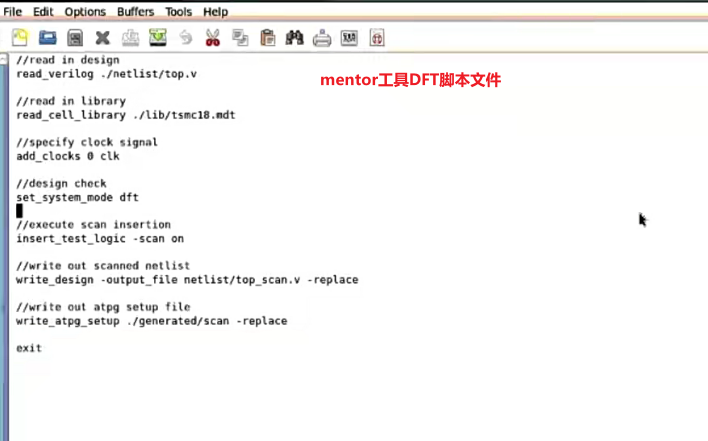

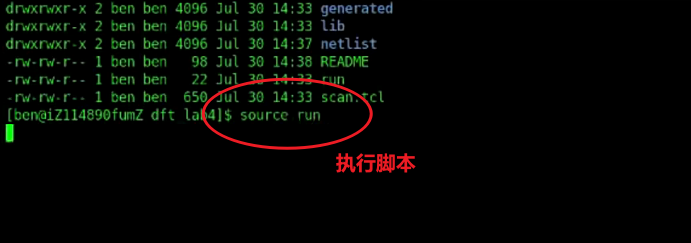

Mentor DFT脚本

- add_clocks 0 clk - 0表示上升沿

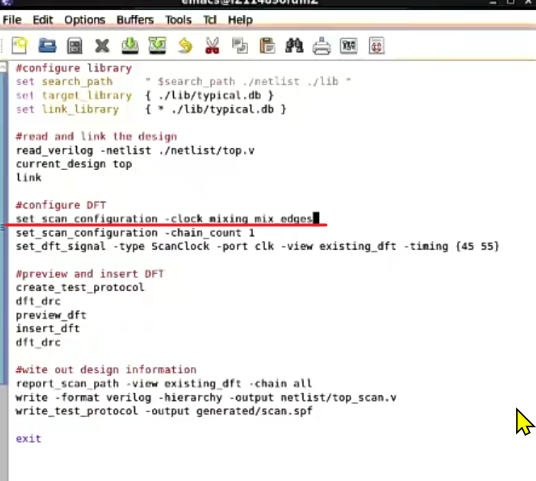

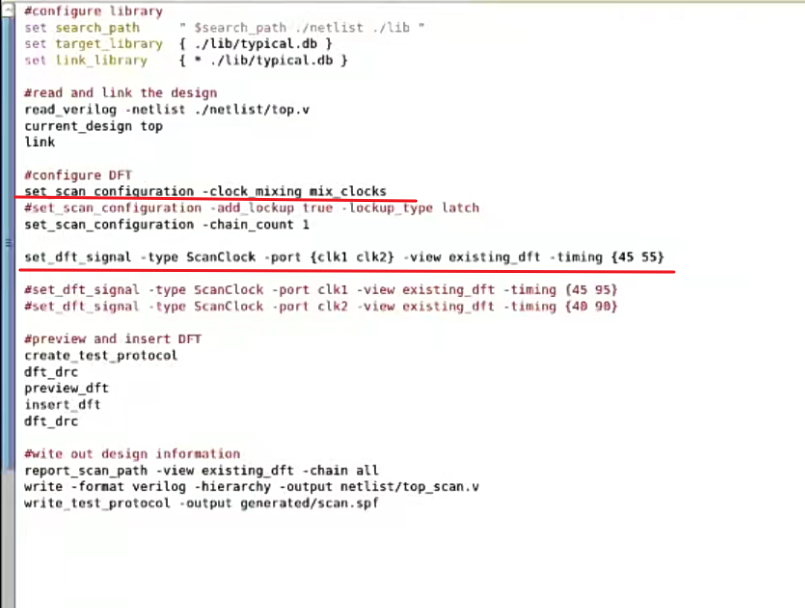

Synopsys DFT脚本

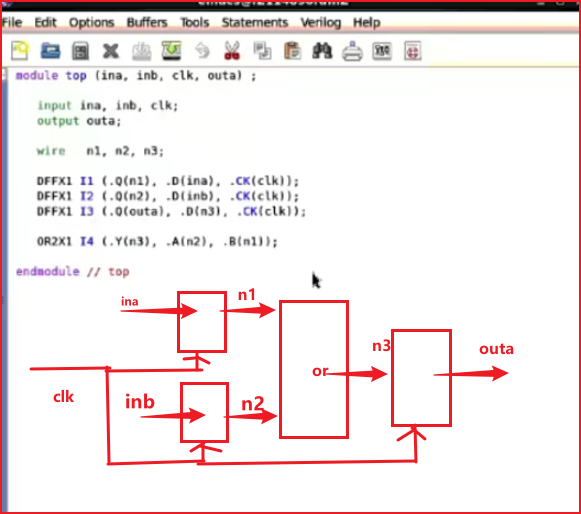

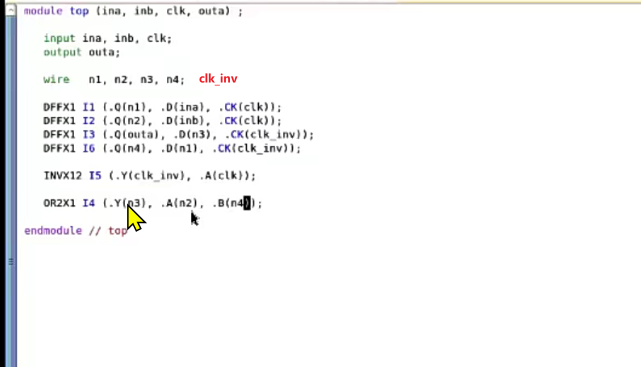

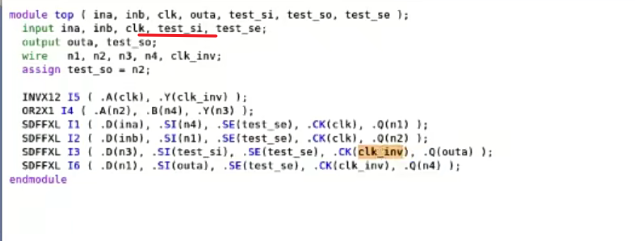

更改netlist

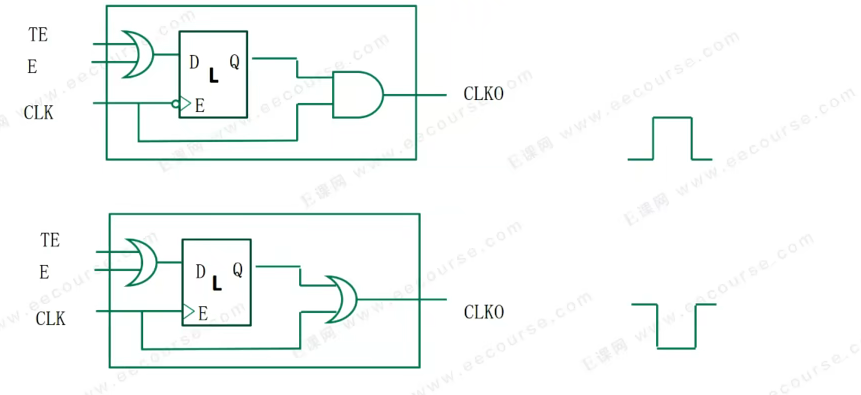

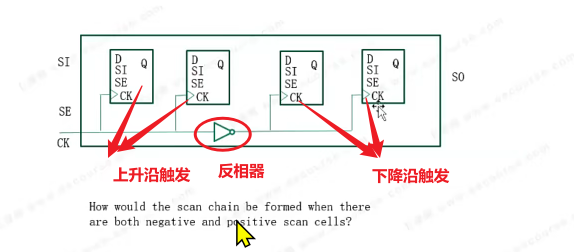

- 需要反相器,实现设计中既有上升沿触发的期间和下降沿触发的

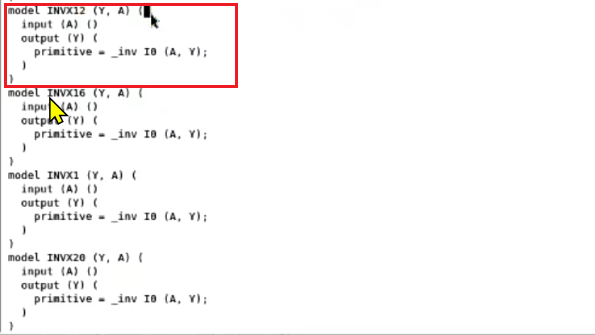

- sysnopsys的库文件是.db文件,是二进制文件,是不可读的

- mentor的库文件是.mdt的文件,是可读的,可以从其中找一个反相器

- Netlist更改完成

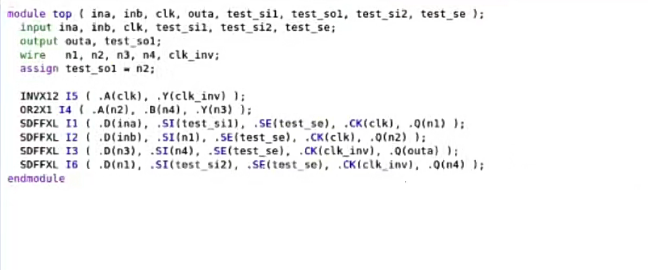

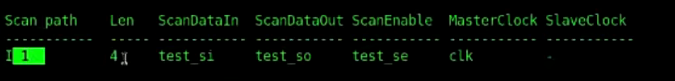

输出的Netlist

- 工具默认的行为是将上升沿和下降沿的cell分别串成scan chain

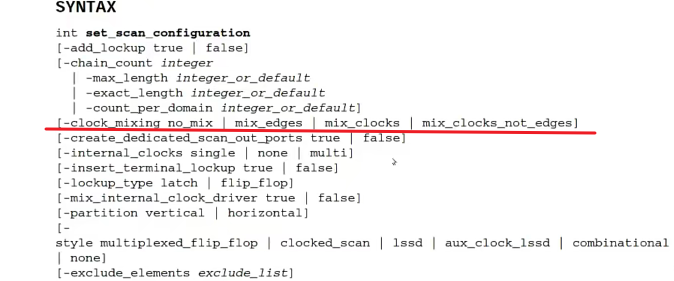

set_scan_configuration

修改脚本

- 会将上升沿和下降沿的寄存器串成一个chain

- 一个test_si,先连到I3,I3是下降沿触发的,所以有上升沿和下降沿的寄存器,scan chain是先串下降沿再串上升沿

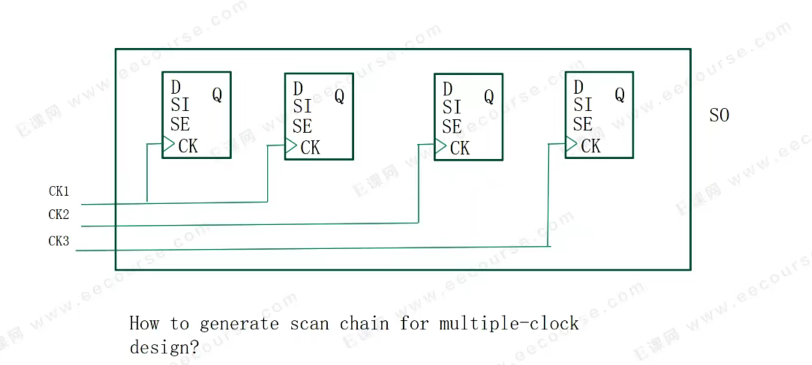

Multiple clock domain

- 默认会将不同的clock domain看成异步的关系,串成不同的scan chain,但是有时候会将多个时钟域串成一条scan chain,如何实现?

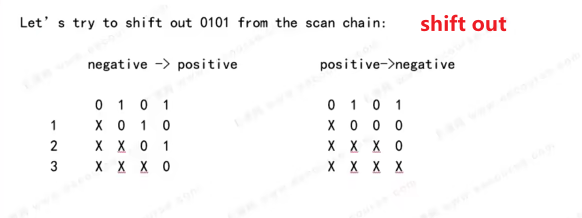

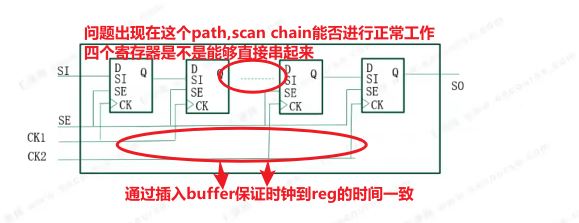

- 在一个时钟周期内,capture值越晚的,在scan chain中越向前

- 下降沿触发reg在上升沿触发器reg之前

- clock skew,clk上升沿晚到的clk,在scan chain中在前

- 不满足上述条件容易出现的问题:shift in的时候容易出现连着两个cell的值是一样的,shift out的时候,会丢失scan chain的值

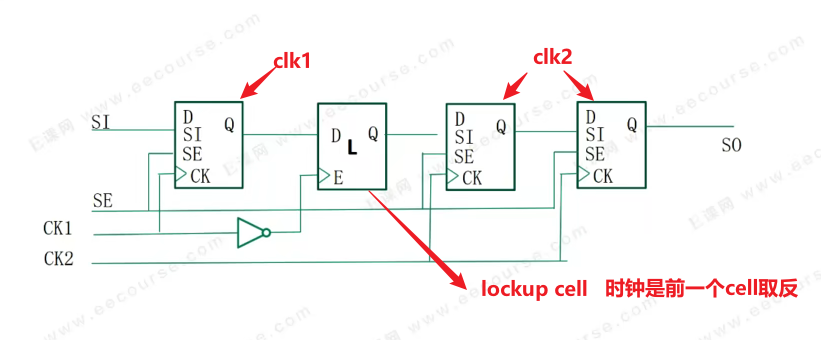

- lockup cell是为了解决两个clock domain之间串scan chain的问题,不是为了解决register在scan chain上前后的顺序问题

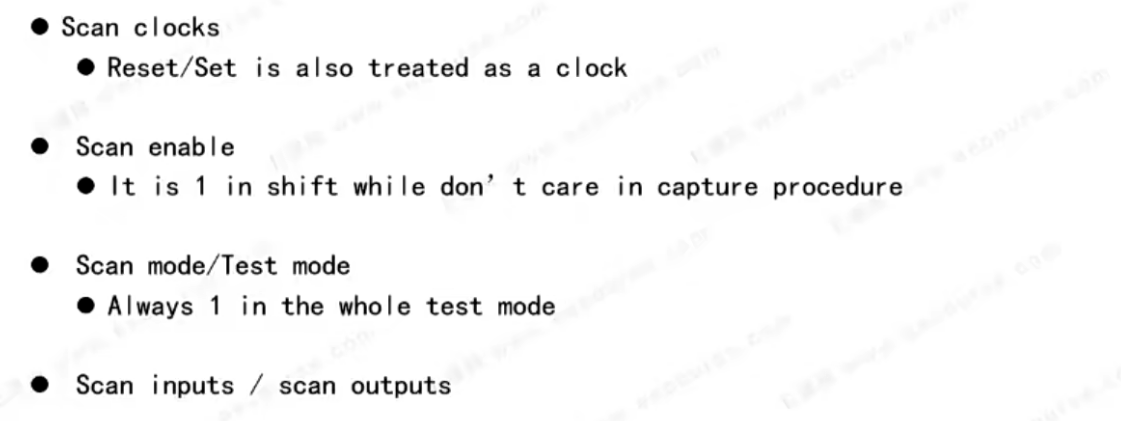

Scan related signal

Scan Design rules - Clock

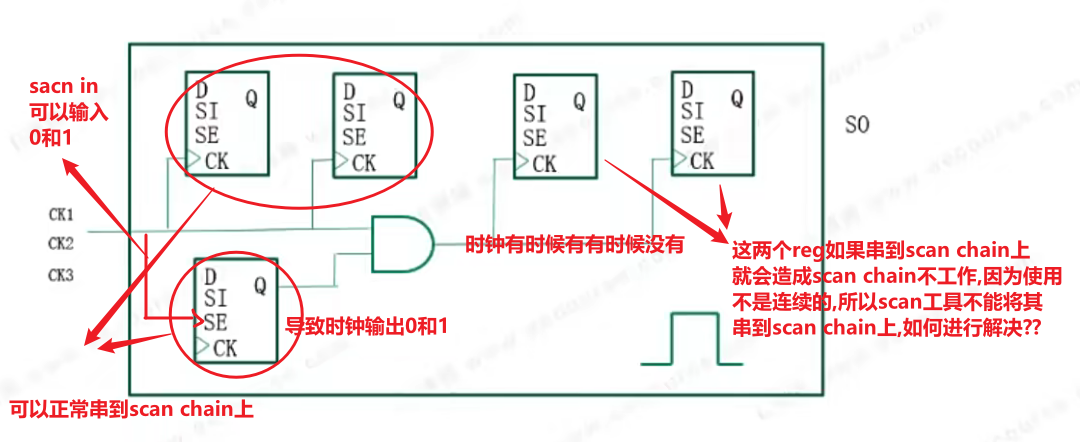

- 判断cell是不是能够串到scan chain上去,看cell串到scan chain上之后,scan chain是不是能正常的shift in和shift out

- 更改设计,function mode下的design保持不变,在df mode下将时钟打通,就可以将后面两个reg串到scan chain上

- 为什么时钟上要加与门?原因是为了低功耗设计,添加clock gating

- 时钟切换(clock toggle)导致晶体管的反转,功耗比较大

- 更改设计的方式:将逻辑更改,放到RTL中,综合之后可以考虑其中的时序;直接在netlist上使用工具进行auto fixed

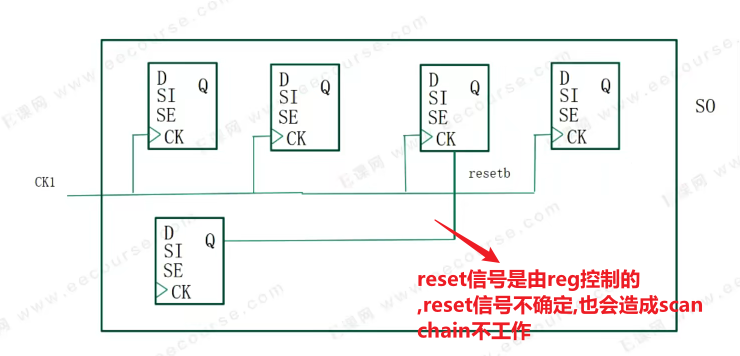

Scan Design rules - Set/Reset

- reset信号是由DFF控制的,可能为0,可能为1,如果串到scan chain上去,导致scan chain不能正常shift in,shift out

Clocking Gating Cell