Verilog仿真实践

- Verilog必须掌握

- 逻辑仿真工具(VCS)和逻辑综合工具(DC)

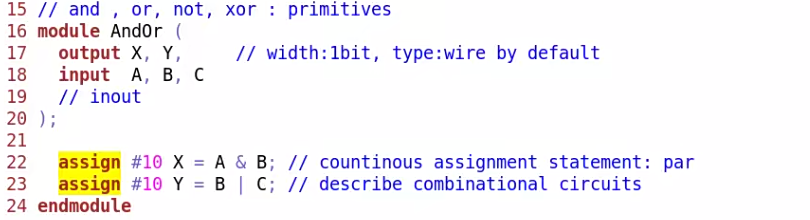

AndOR

module AndOr(

output X,Y,

input A,B,C

);

// A B进行按位与运算

assign #10 X = A & B;

// B C按位进行或运算

assign #10 Y = B | C;

endmodule

- #表示延时10个仿真单位

`timescale 1ns/1ps

- assign语句时并发执行的

- coding style - 在coding中不添加#延时

-

延时信息时不可综合的

- 使用RTL级写法

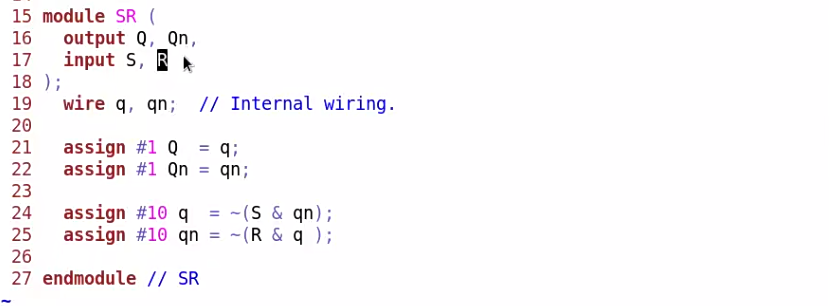

SR(latch)

- Coding之前,需要先写Design Spec

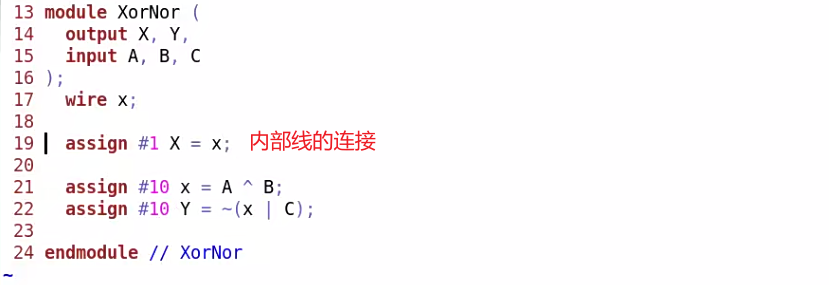

XorNor

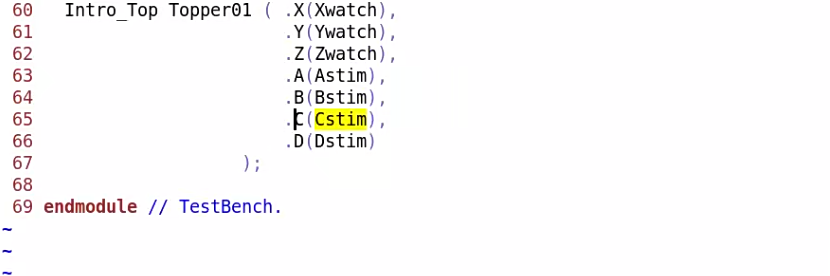

顶层

- 例化子模块,连接子模块

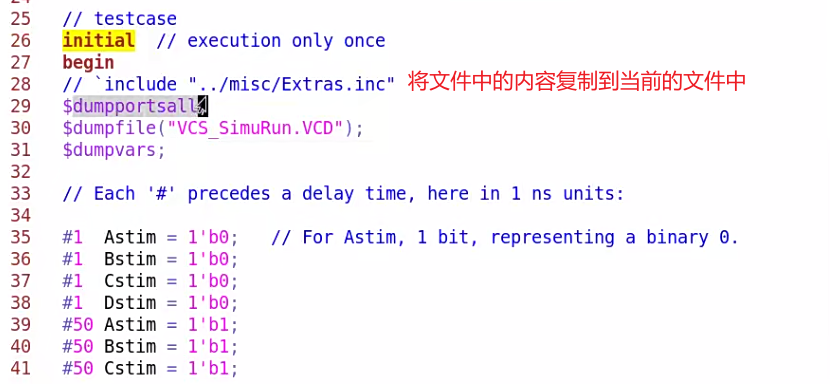

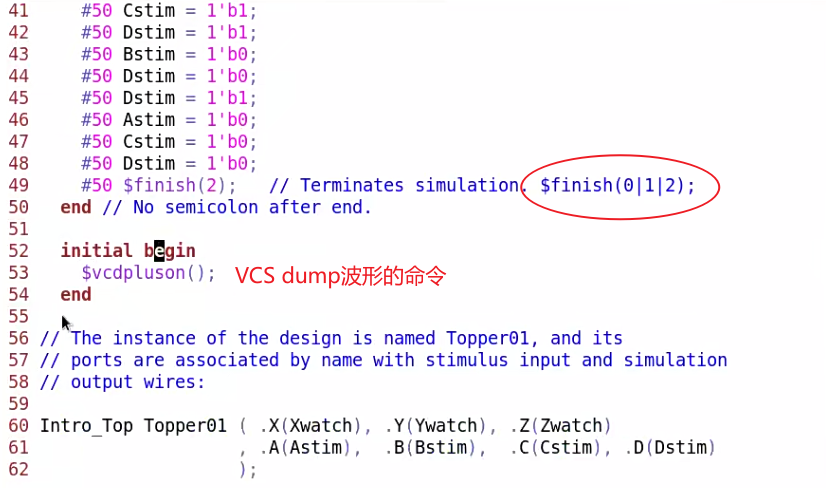

Testbench

- initial begin中左侧的变量使用reg类型

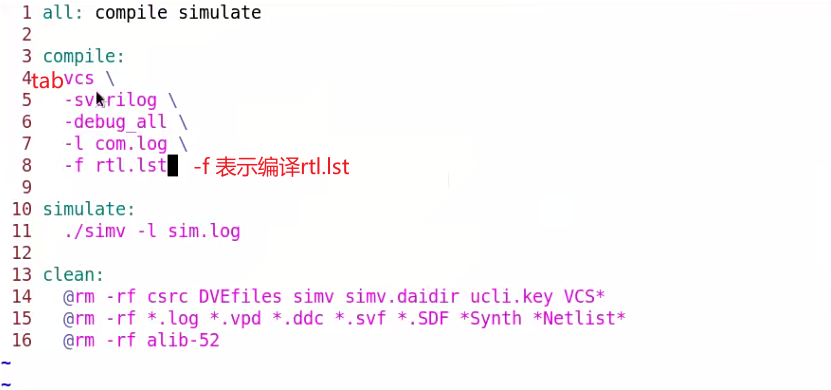

Makefile

timesacle

- 可以将timescale单独写一个.v文件,然后包含在filelist.lst中

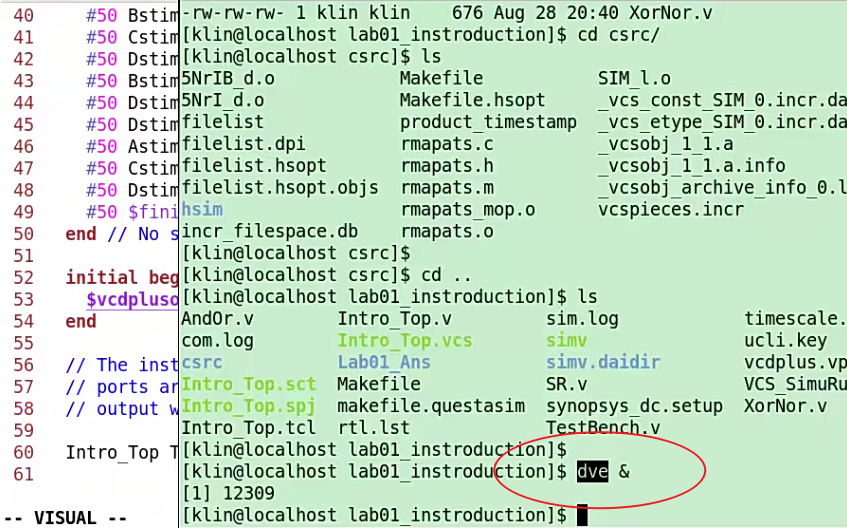

执行仿真

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)