Scan Synthesis Review

Review

- scan replacement - 将normal DFF替换为mux gate DFF

- scan stitching - 将DFF连接起来

- scan的作用:将测试困难的时序逻辑转变为易于测试的组合逻辑

- scanc测试过程:包含对于组合逻辑测试和时序逻辑测试两个过程,对于时序逻辑进行测试就是对于scan chain进行测试

时序逻辑测试

1.切换到scan mode(scan enable拉高)

2.scan input输入固定的pattern,一拍一拍进行输入

3.scan output接收pattern,一拍一拍接收

组合逻辑测试

1.切换到scan mode

2.输入test pattern(PPIs)

3.切换到function mode,输入(PIs)

4.测试POs

5.捕获组合逻辑的响应进行锁存

6.切换到scan mode

7.scan out

How to design scan clock structure

- 设计多为同步设计,同步设计都是通过时钟进行驱动的

- function design - 对于不同的clock domain进行单独的check,不同clock domain之间的关系是不check的

- 不同时钟域的DFF,在插入scan chain的时候如何考虑?

- 如果Design只有一个clock,做scan的时候可以使用function mode下的clock

- 一般在一个芯片中会有几十个或者是上百个clock domain,对于function clk,保证各个clk之间相互没有关系即可

- 对于scan clk而言,io数量是非常有限的(几百个或者几十个),例如一个芯片中有50个clk domain,其中一种方法可以将50个function clk拉出来进行测试,但是实际上在进行scan的时候是不会给那么多clk port,剩下的进行scan channel的数量就很少

- 在考虑scan clk的时候,为了节约IO数量,进行clk merge或者clk group

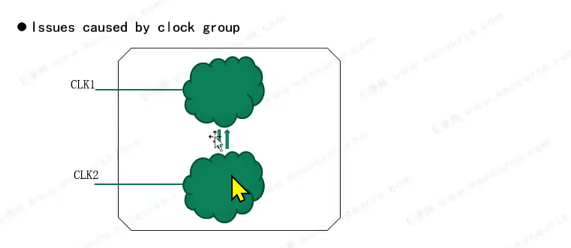

- 进行时序分析的时候认为clk1和clk2是异步的,进行timing check的时候都是分开考虑的

- 两个逻辑之间的数据交互通过设计方面进行解决:比如使用异步FiFo,实现两个时钟域进行信息交互或者使用两级或者三级同步器进行保证跨时钟域方式进行处理,通过同步设计的方法进行解决不是通过STA的方式进行解决

- 如果将这两个时钟进行merge,在timing check的时候,在进行STA的时候,不同的mode都需要进行check,但是不同的mode,使用的clk是不同的,如果时钟进行时钟的merge之后,就容易出现问题

- clk merge可能会增加额外的STA timing check和PR fixed timing violation

- 将没有交互的clk可以合并到一个clk,将交互比较少的clk进行merge,相近的频率的时钟可以merge在一起