DFT Architecture

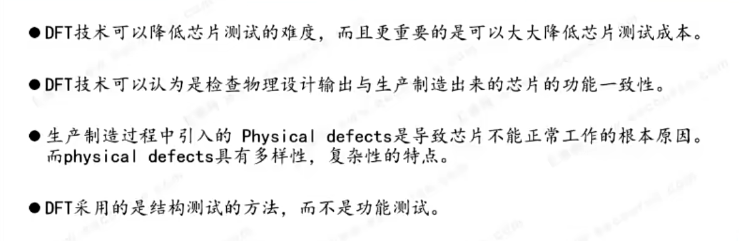

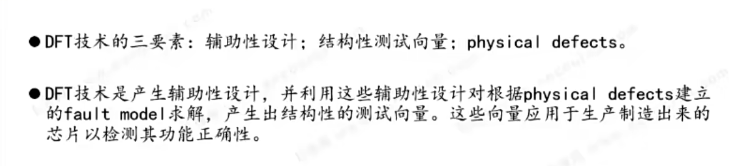

Design For Test

- 在实际生产过程中产生的physical defect是导致芯片功能出错的根本原因

- 如何根据结构产生测试向量呢?主要考虑physical defect

- physical defect有多种,针对不同的physical defect有不同的处理方式

- Design - 是为了产生结构性测试向量,利用设计对于fault model数学模型进行求解,求解之后产生结构性的测试向量

- physical defect具有复杂性和多样相,直接对于fault model进行求解,模型会非常大

- DFT - 首先将physical defect进行分解,建立不同的fault model,针对这些fault model(故障模型)进行求解

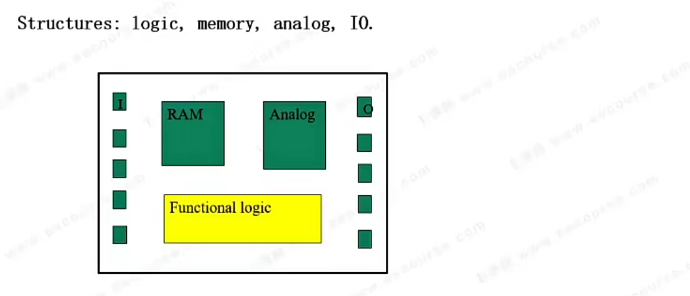

DFT Structure Test

- 主要介绍function logic进行讲解

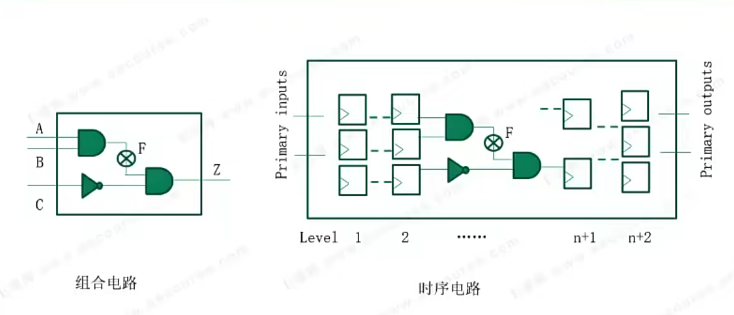

时序电路和组合逻辑电路

- 对于组合电路而言,如果中间出现故障,可以在input pin上输入激励,在output pin上接受结果进行测试

- 对于时序电路,如果要对某个模型进行求解,输入需要经过多级logic进行输入,输出也需要经过多级logic进行输出,因为中间的延时或者其他因素,导致可能检测不出其中的问题

- 时序逻辑电路测试 - 时间更长,难度更大

- 能否将时序逻辑电路转变为组合逻辑电路的方式进行测试?

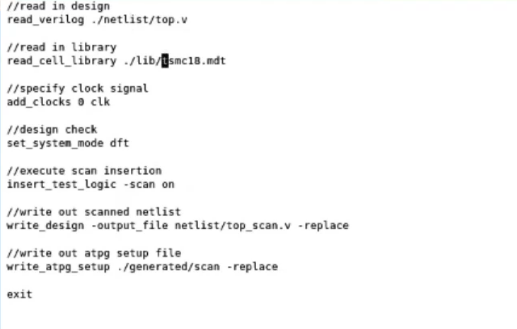

Scan Synthesis

针对function logic需要做的辅助性设计

- scan replacement - 替换操作

- scan stitching - 连接操作

- scan synthesis不是在RTL级别进行的,scan synthesis是作用在综合之后的网表上的,在综合完成之后,进行插入scan的操作

- scan synthesis插入的方式:可以综合之后,独立进行,或者是包含在逻辑综合过程之中

- scan synthesis作用:将难测试的时序电路转变为一个易于测试的时序逻辑电路

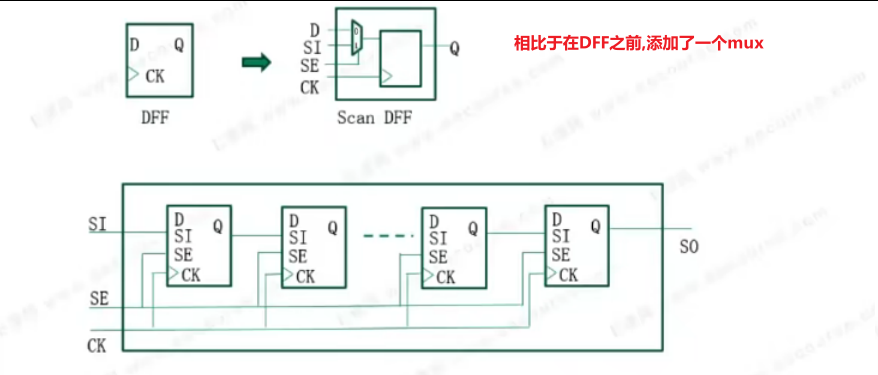

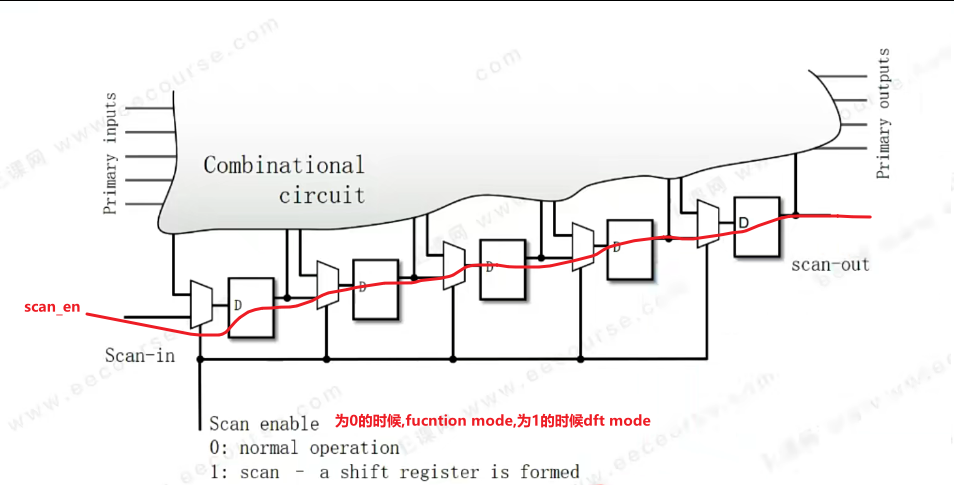

scan replacement & scan stitching

- 在数据输入端添加mux,增加SI,SE pin,当SE为低电平的时候,输出为D,和原来的DFF一致,SE为低的时候,实现function功能

- scan插入不能破坏原来的function logic

- 替换之后SE和SI是floating,scan stitching就是将SI和SE连接出来

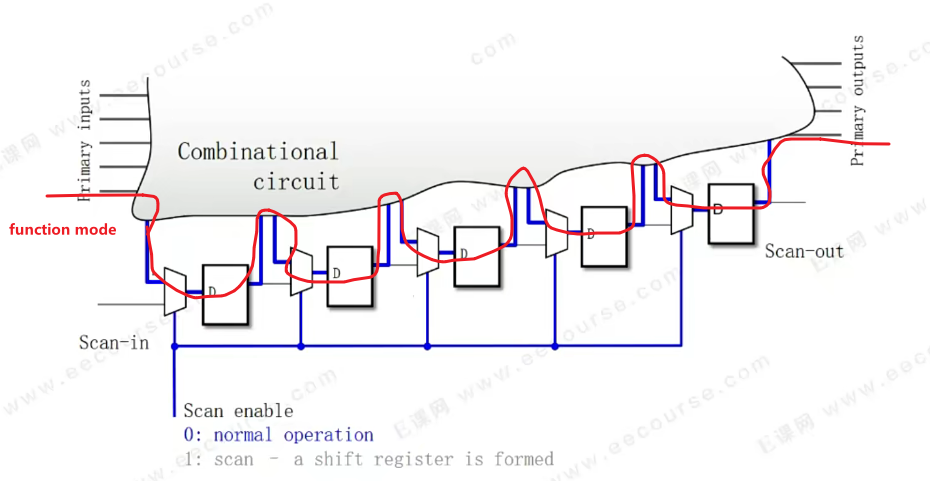

- SE连接:在芯片输入端添加一个sacn_en port,这个port会驱动所有替换之后cell的SE pin,当这个port为0的时候,design工作在function mode下

- SI连接:替换之后的DFF,SI将Q端进行连接,形成chain,连接SI和SO

- 辅助性设计完成,需要产生结构性测试向量?如何实现将时序电路的测试转变为组合逻辑电路

Scan Operation

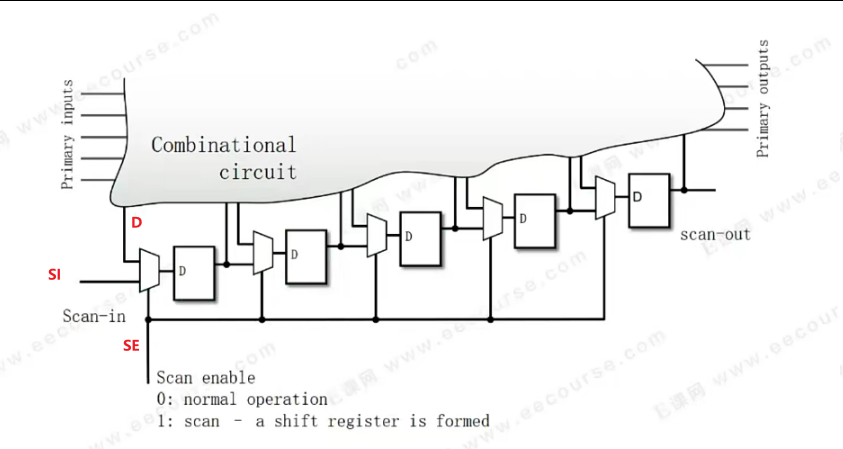

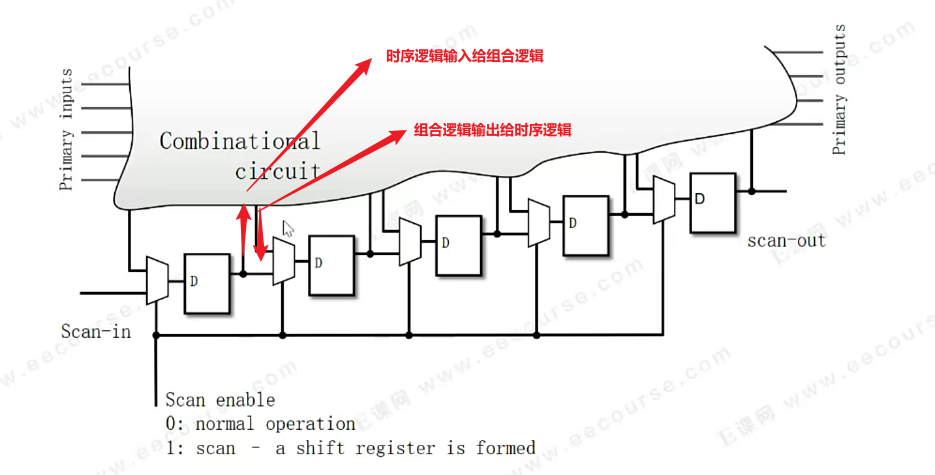

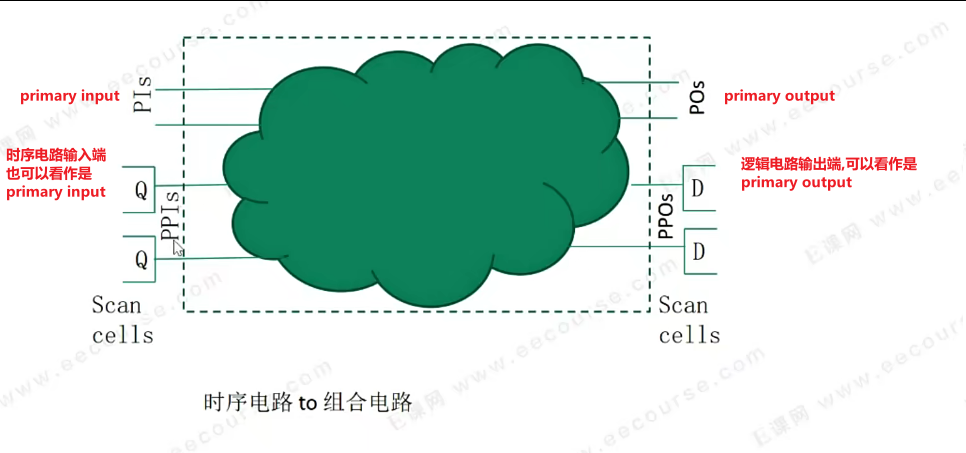

Circuit Transition

- 将时序逻辑转变为组合逻辑模型,进行求解结构性测试向量

- PIs - 直接通过pin输入,POs通过输出pin观察稳定的值

- PPIs和PPOs如何进行输入和观察? PPIs和PPOs是假设的pin,用于转变时序逻辑为组合逻辑,PPIs有很多电路内部的结果,如何进行输入,通过辅助性设计实现SI和SO(输入PPIs和PPOs)

- scan synthesis进行可以在综合的过程中,综合过程是需要考虑时序和面积的,加入scan之后,会添加组合逻辑,在综合过程中可以考虑到scan replacement之后的的cell delay和timing优化

- PPOs观测过程:PIs和PPIs输入之后,经过一段时间,POs和PPOs的值都是稳定的,此时scan enbale为低的时候,function logic是被打通的,此时来一个clock pluse,组合逻辑输入到时序逻辑的值是可以被DFF锁存起来的;scan enable拉高,可以将锁存的值一拍一拍的拿到,可以观测SI

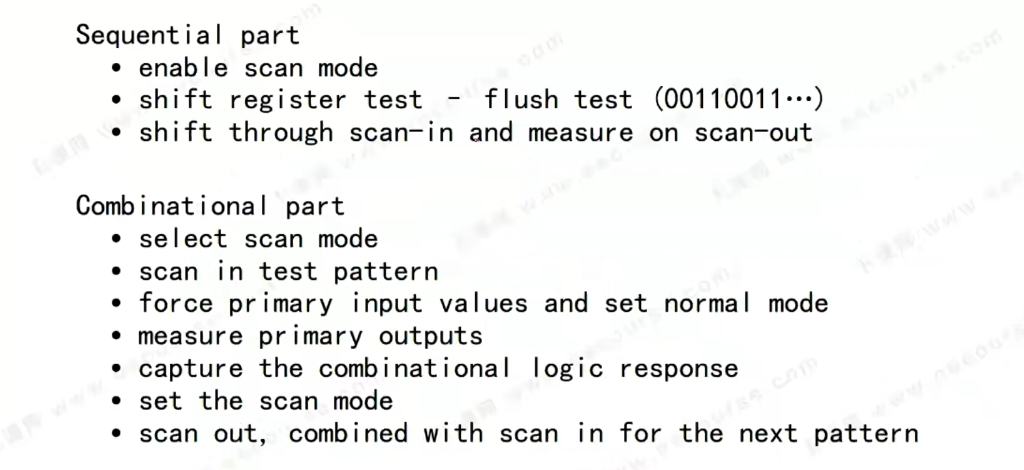

Test Procedure

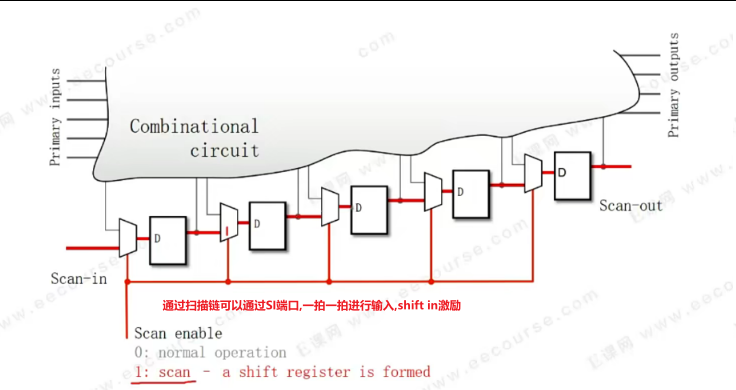

- 对于scan chain进行测试,在扫描链上是否能够正确的shift in和shift out,只有能正确的移入0和1的值,才能在PPO上添加正确的激励

- 对于scan chain进行测试,实际上也包含了对于时序逻辑的测试

- 时序逻辑测试过程:enable scan mode打通扫描链,shifter register test - 输入一组固定的pattern进行测试,通过scan input一拍一拍的输入pattern,通过scan out,一拍一拍向外取出值,看输入pattern的值是否被正确取出,正确取出表示scan chain没有问题

- 组合逻辑测试:scan enable拉高,选择scan mode;sacn in test pattern,是对PPI赋值的过程,如果有5个cell,经过5拍就可以将PPI的值赋好;对PIs进行赋值,通过chip io上进行赋值,赋值完成之后切换到function mode,等待一段时间之后,POs和PPOs都是稳定的;进行比较POs的值;在时钟边沿,捕获PPOs的值锁存到DFF中,然后切换到scan mode,通过scan out端口一拍一拍取出

- 前一条pattern shift out的时候,后一条pattern可以进行shift in,两个过程互不影响

Scan synthesis中经常遇到的问题

- Negative + Positive,一部分cell上升沿驱动,一部分下降沿驱动,连在一起需要考虑什么?

- Clock Domain Crossing

- Scan Design Rule Check(DRC),cell连接起来是不是能够形成scan chain

How to consider scan synthesis in project

- 从项目的角度考虑辅助设计

- scan chain测试时间主要在shift in

- 实际项目中会有很多条scan chain,对于IO数量有要求,在chip level上需要考虑有多少个IO,通常项目中,不会为scan test增加新的IO,通常会考虑IO复用,使用function mode的IO进行复用

- 考虑share IO需要使用Pin Mux

- 考虑减小scan chain的长度,减小时间成本

How many IOs are available for scan testing

- 使用ATE进行测试,需要考虑ATE的channel的数量

- 芯片IO数量会影响Package方式,通常按照最小pin数量的封装方式进行设计

- scan channels/scan enable/test mode/scan clock

Shared IO and Pin Mux

- pin mux io复用,列举出当前chip一共有多少个io,在不同的模式下(function mode/dft mode/bist test/cpu test等)选择不同的io

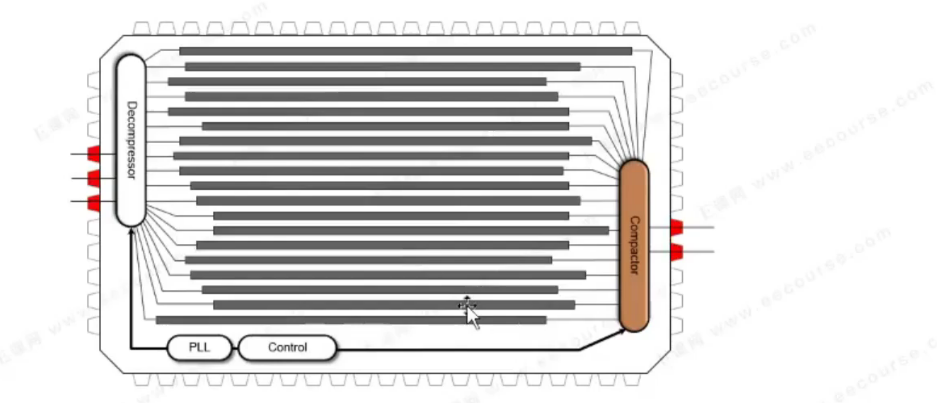

How to define compression ratio

- sacn chain越短,test成本越低

- scan chain越短,IO数量越多

- 通过解码和编码的方式,通过少的输入=,将少量的输入进行编码,得到多种不同的组合,然后通过解码输出,可以减少io pin的使用和减少scan chain length,从而减少成本

- 加入综合之后有100万个DFF,有100对pin,需要shift 10000个cycle才能讲PPI进行输入完成,时间比较长

How to form scan chains?

实例

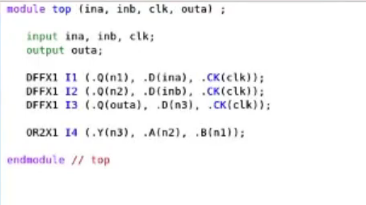

输入综合之后的网表

输入library

执行脚本