SV 接口中的clocking

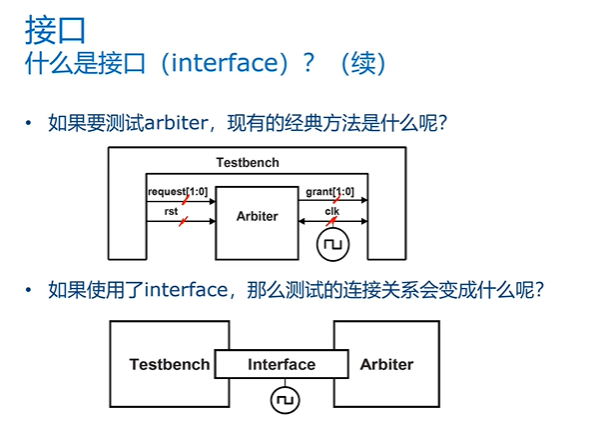

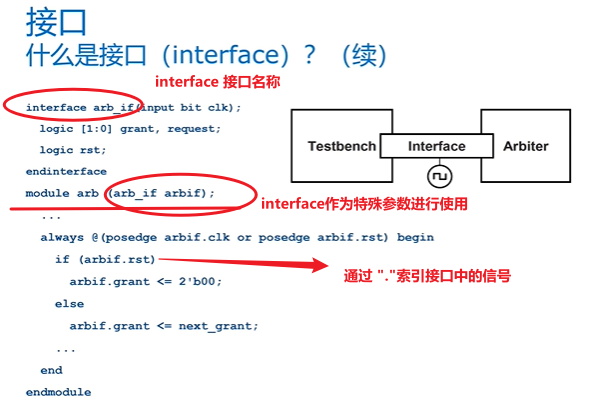

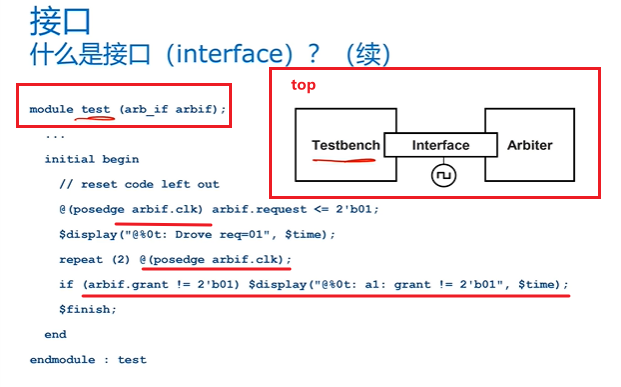

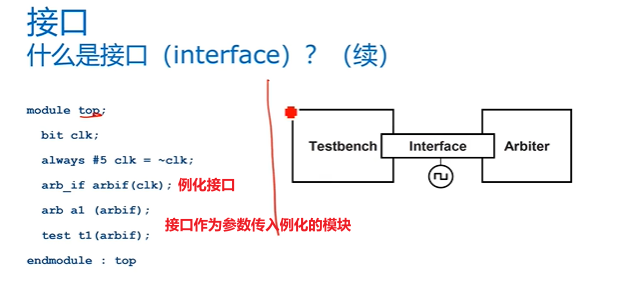

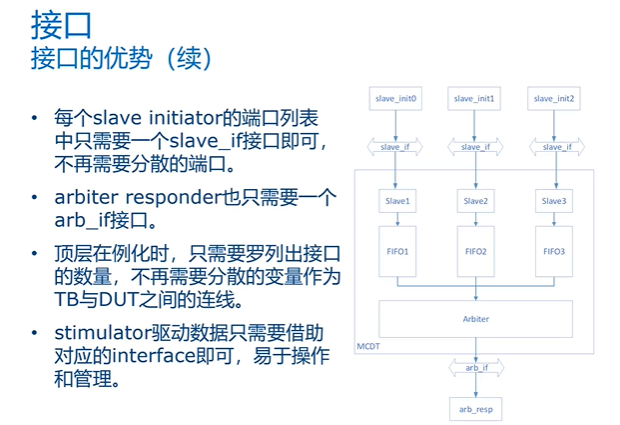

接口

- module可以例化模块,可以例化接口

- 接口不能例化模块

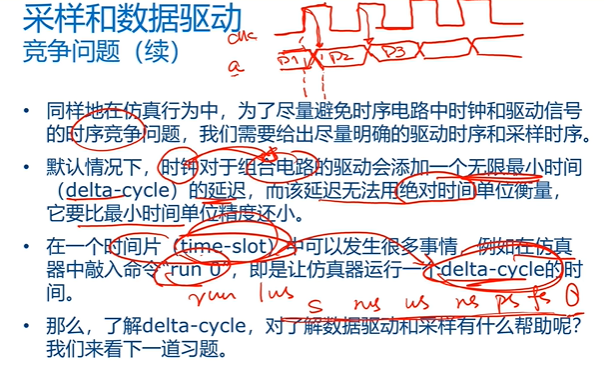

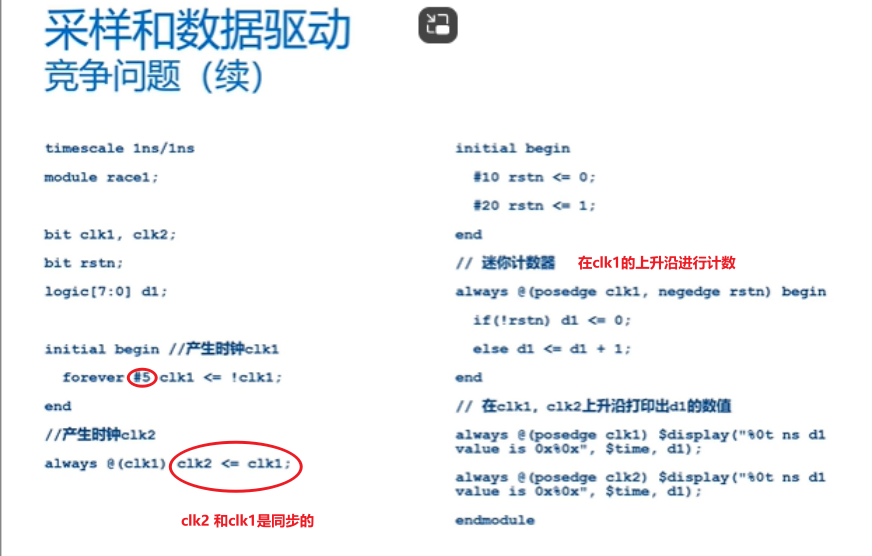

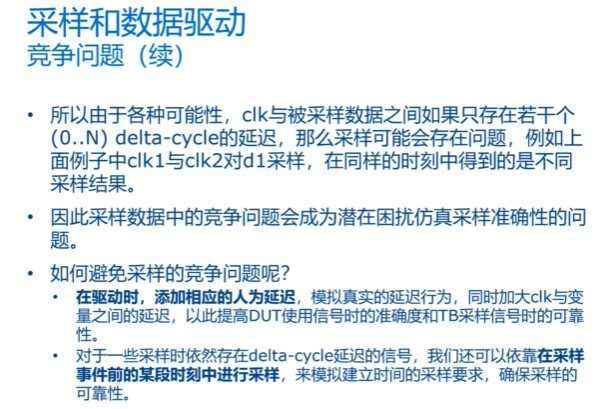

采样和数据驱动

- 时钟驱动数据,数据会有延迟,RTL仿真的时候,不会仿真出这个延时;RTL仿真的时候,不会仿真出寄存器的延时;只有在门级仿真的时候,才会表现出来

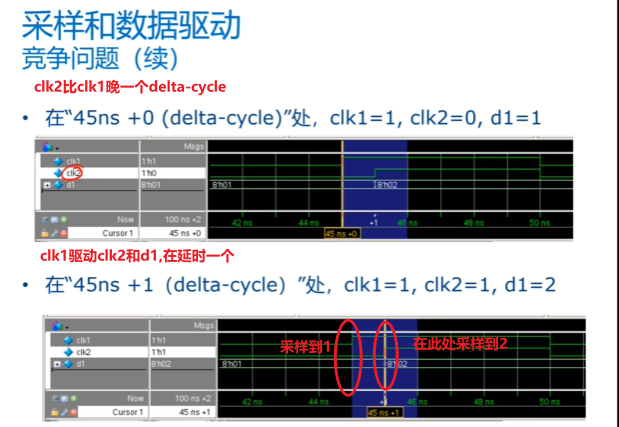

- 时钟对于组合电路的驱动会默认增加一个无限最小的时间的延时(delta-cycle),该延时无法用绝对时间单位衡量

- 在特定的光标处,展开delta-cycle

- 对于时钟进行分频或者是添加clock gating或者其他组合逻辑,就会增加delta-cycle

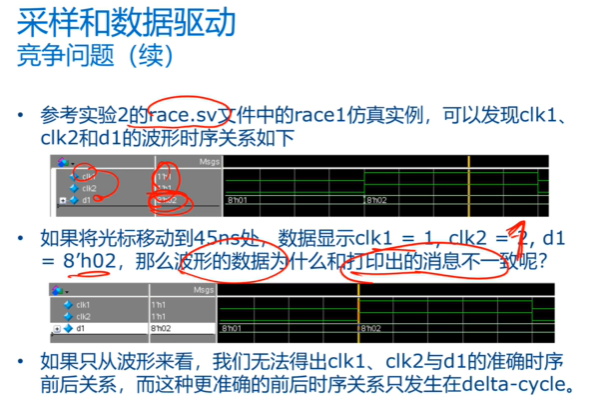

- 在45ns处,clk1采样到的值是1;clk2是由clk1进行驱动的,所以都会有delta-cycle的延时;d1得值也是clk1进行驱动的,也会有delta-cycle的延时,delta-cycle的延时具有不稳定性,当clk2进行采样的时候,d1可能没有变化,仍然采样到1,d1也可能发生了变化,采样到2

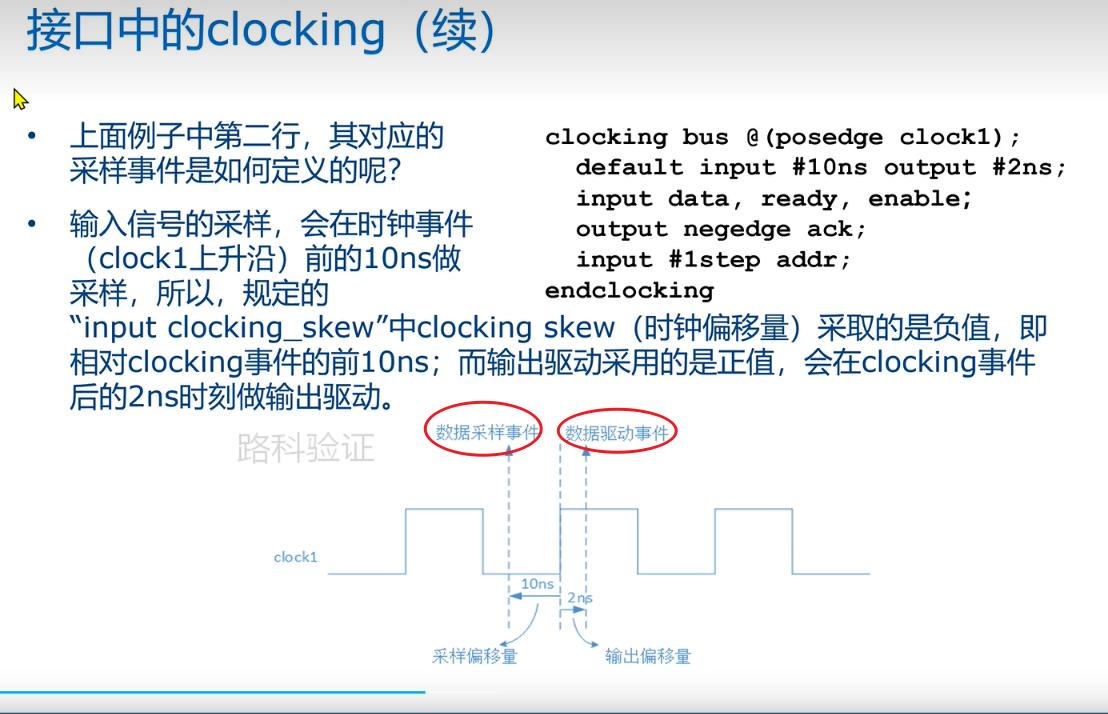

接口中的clking

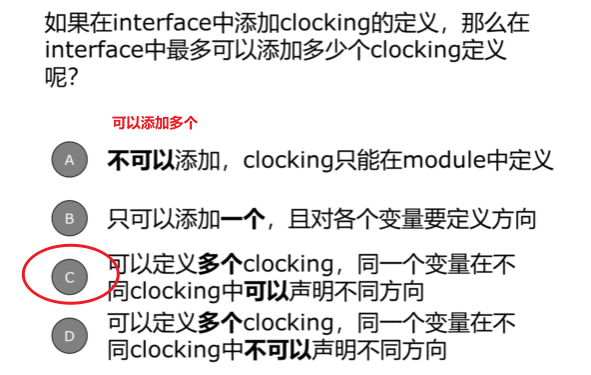

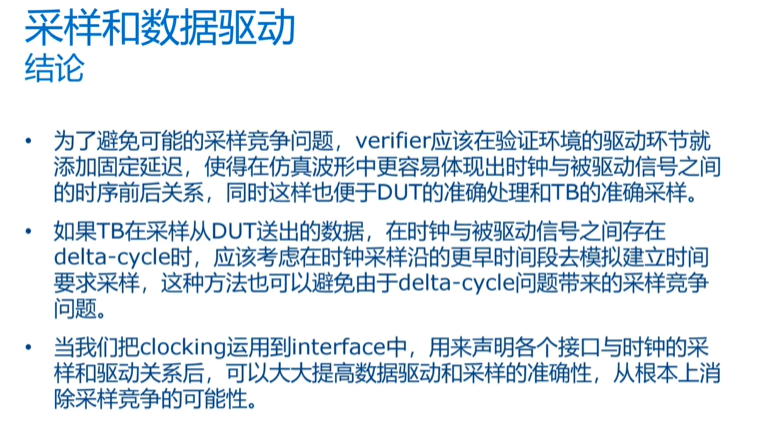

- clocking可以在module和interface中进行声明

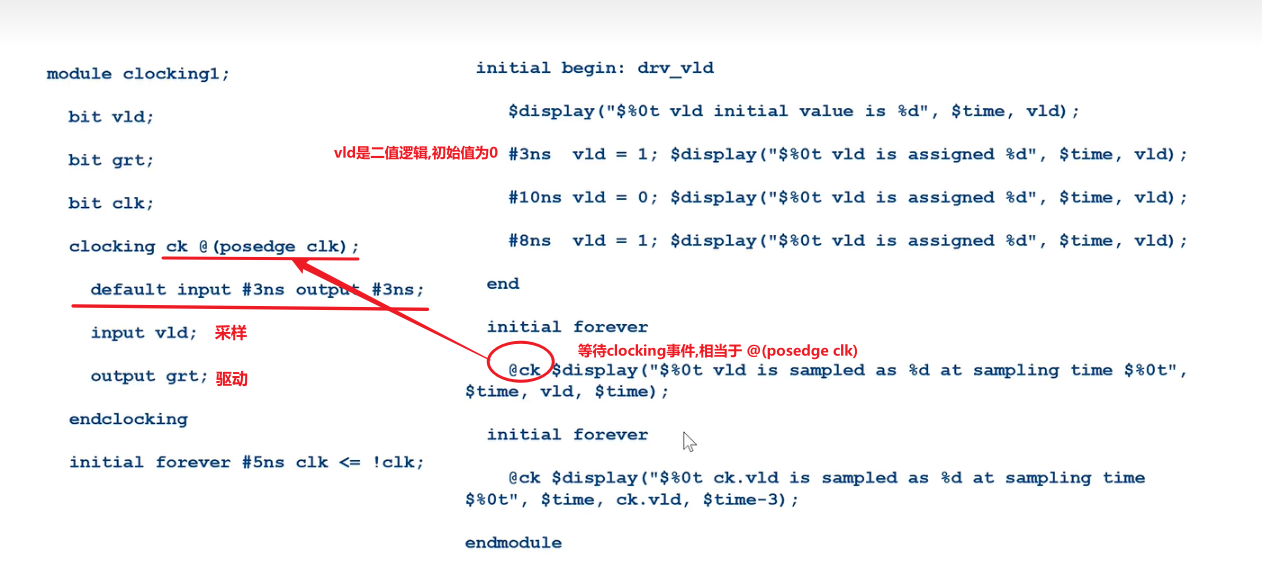

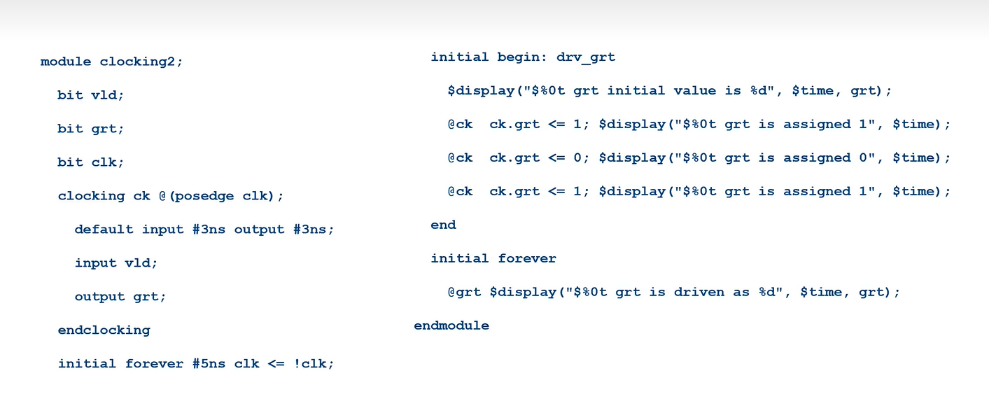

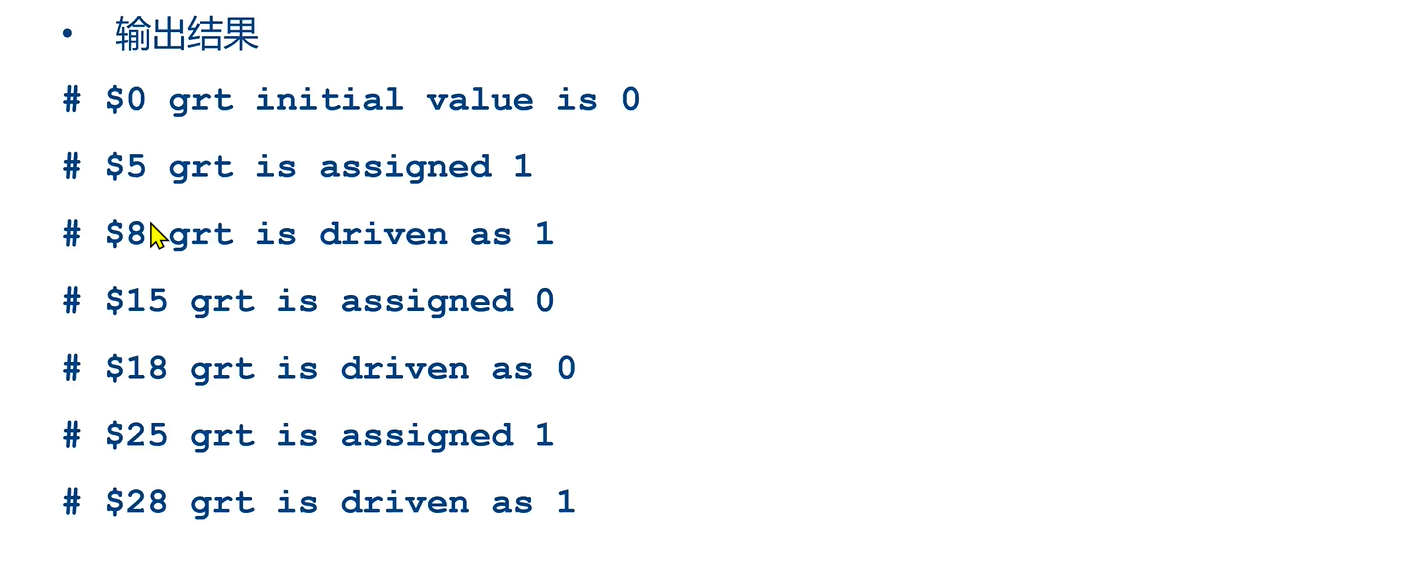

- 利用clocking对于信号进行驱动和采样

- 根据时钟进行采样和根据clocking模块中的约束进行采样的结果是不同的

- 在仿真过程中,时钟上升沿和vld信号是由时钟驱动,下行DUT会使用时钟上升沿采样vld信号;仿真的时候时钟和vld可能是没有延时的,但是在实际的时候会有delay,所以要通过人为插入delay来模拟时钟的延时

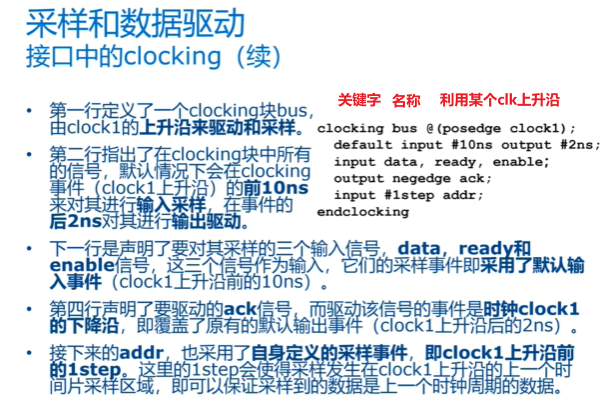

- input #1 - 在时钟上升沿之前1ns采样

- output #1 - 在时钟上升沿之后1ns进行采样

- RTL仿真是没有任何的物理信息的

- clocking中设置的延时是通过后端布局布线的时序信息