Prime Time - 介绍

Prime Time是对timing进行分析

Prime Time使用的是STA方法进行分析

- 工具会有更新,但是核心内容是不变的

Prime Time(intro to STA)

- 没有PT工具的时候,check timing需要对于门级电路进行仿真,耗时时间长

- PT用于静态时序分析的工具

- PT工作在门级电路上

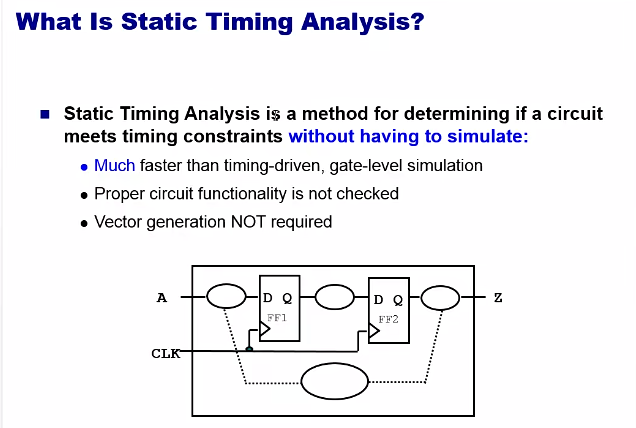

静态时序分析STA

静态时序分析简介

- 主要对于建立时间和保留时间进行检查

- STA是一种穷举的方法,需要将所有的timing path都找到

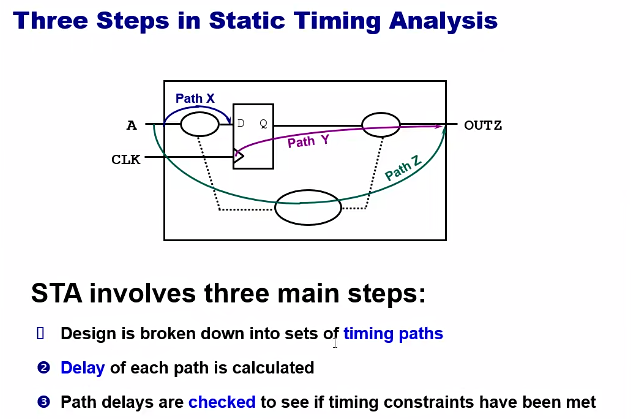

静态时序分析步骤

- 设置一些断点,比如input/output/DFF D端/DFF clk端

- 起始点:input/clk

- 结束点:DFF D端/output

- 计算每条path的delay

- 查看path是否满足timing constrain的要求

timing path类型

timing path有四种类型

- input - D端

- DFF1 D - DFF2 D端

- DFF D - output

- input - output

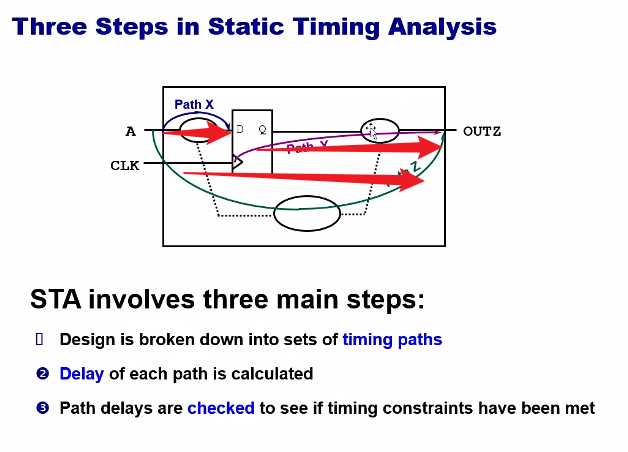

- 计算delay的时候,net和cell的delay需要更具一定的模型和经验进行估算

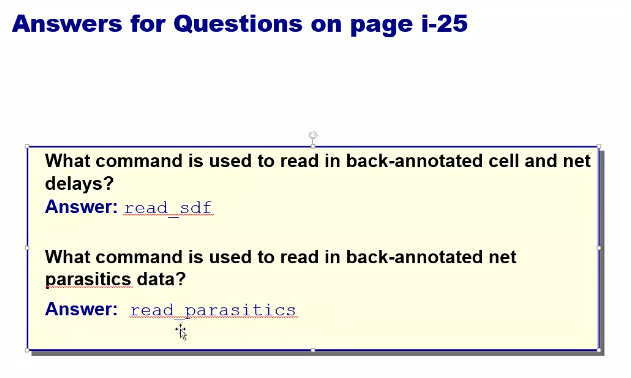

- Post-layout - 仿真的时候已经有线了,可以进行分析,SDF文件读入

- Pre-layout - 仿真的时候没有线,使用一些方法估算(实验值或者经验值)

- 计算完delay之后,需要比较是否满足条件,需要预先设定一些constrain

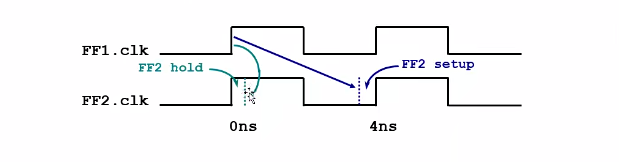

- setup time - 时钟上升沿到来之前,数据稳定一段时间

- hold time - 时钟上升沿之后,数据稳定的时间

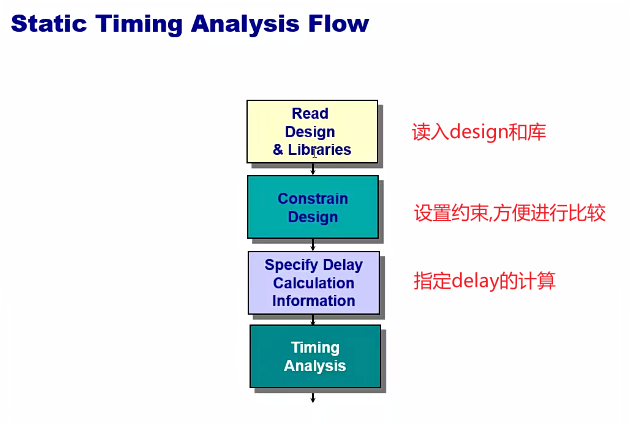

静态时序分析的流程

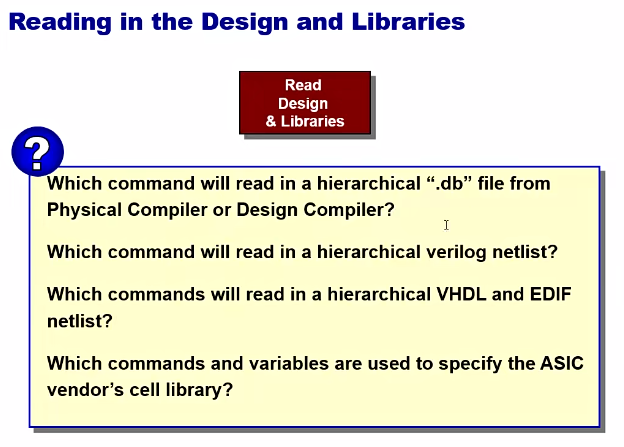

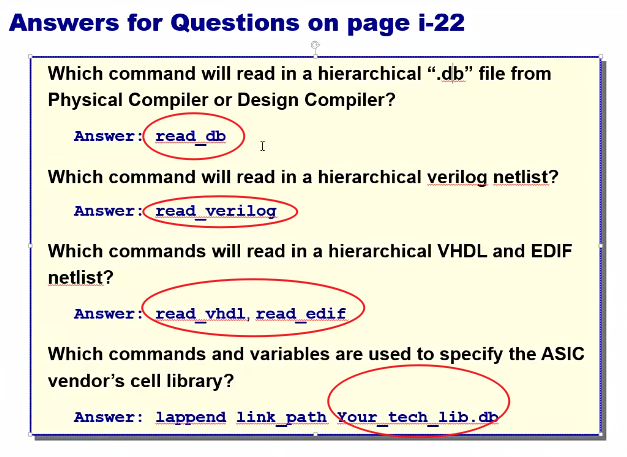

- .db - 工艺文件

- verilog

- cell library

- 整个design包含什么,input port存在delay,clk period需要知道,output port也存在delay,需要设置

- 需要进行设置,高速PT工具

- Pre-layout - 可以提前设定这些参数

- Post-layput - 可以通过工具产生sdf文件或者提取的rc的文件,然后读入这些文件

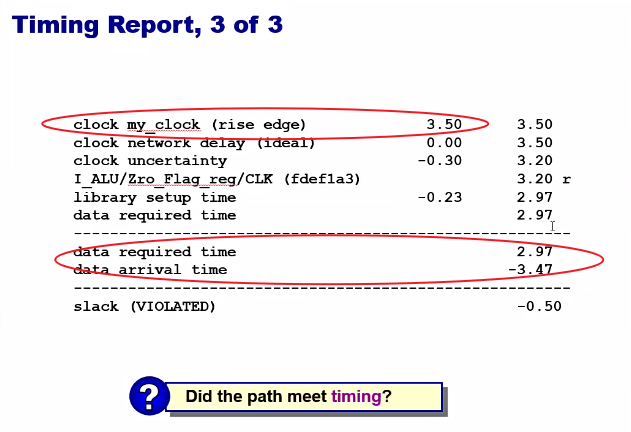

Timing Report

- 计算timing path

- 计算clk path

- data arrive time 要小于data required time,在时钟之前数据到来

- data required time - data arrive time < 0.表示不满足时序要求

- snake path:绕线的path,希望线尽可能的值,delay小