目录

Cortex Vendor - ARM介绍

- ARM主要提供指令集,需要授权

- ARM使用的RSIC结构,功耗比较低

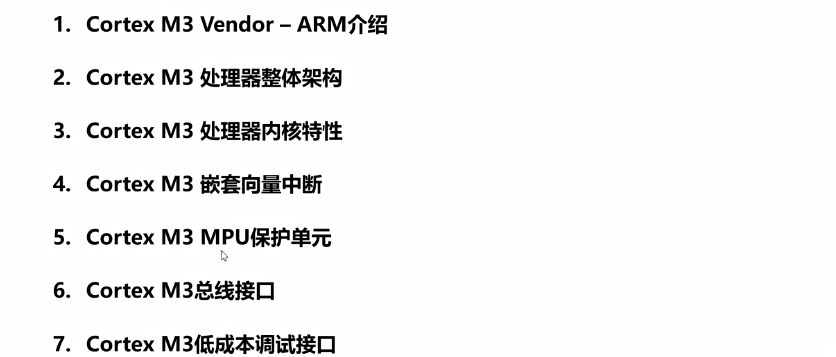

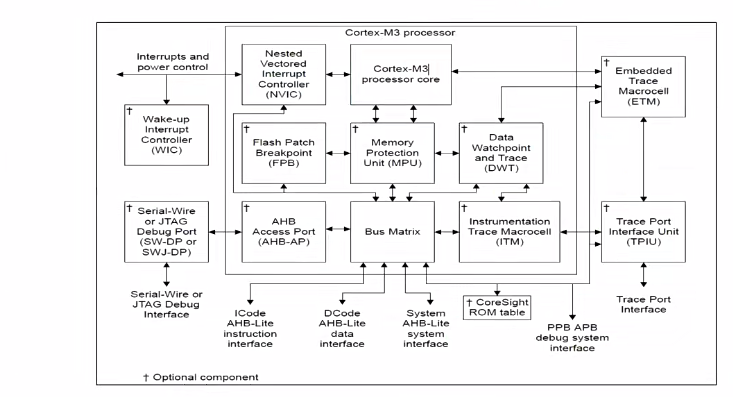

Cortex M3整体架构

- 核心是Processor Core - 包含寄存器和累加单元,指令的取指,译码,执行单元

- Nested Vectored Interrupt Controller(向量中断控制) - 外部中断进来,可以直接上报,不需要查中断号及服务程序;

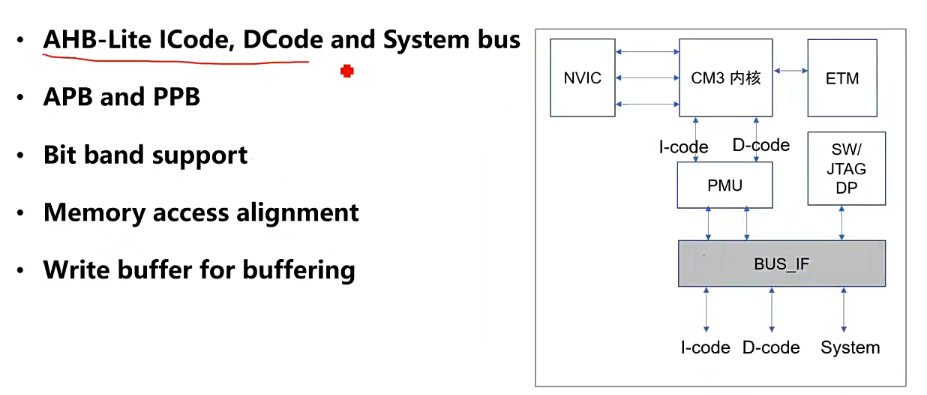

- Processor Core有指令总线和数据总线 - 指令和数据分离,指令和数据可以并行处理

- Memory Protection Unit(MPU)- 对地址进行约束和保护,一些地址只能是指令单元访问,不能数据单元访问,防止内存踩踏,可以理解为特殊地址单元的保护;可以设置privilege和user权限,priviledge用于操作系统访问,user用于用户软件访问,有些地址可以操作系统进行读写,用户不能读写,进行区分

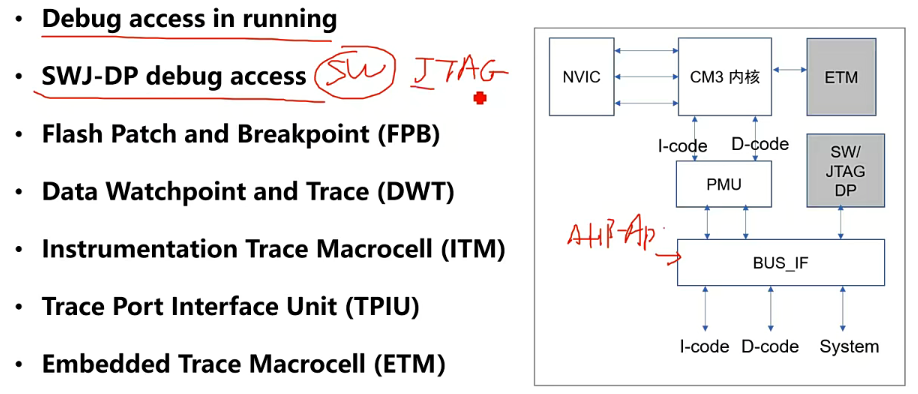

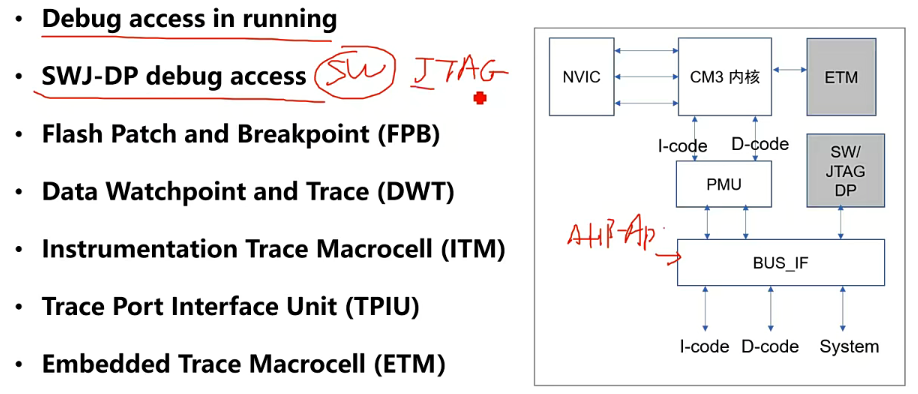

- Flash Patch Breakpoint(FPB)

- Data Watchpoint and Trace(DWT)

- Bus Matrix - 进行指令的译码

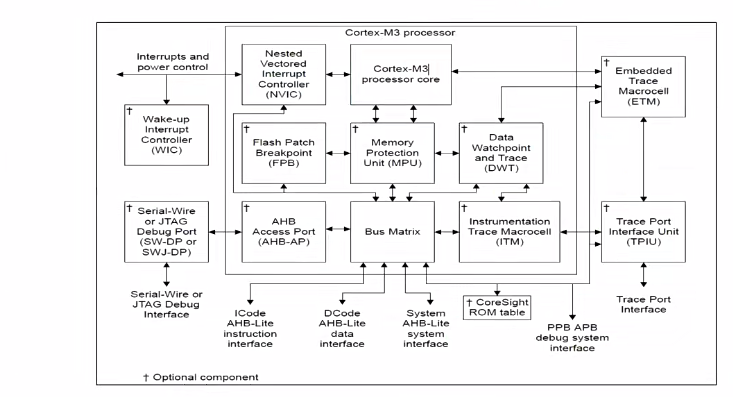

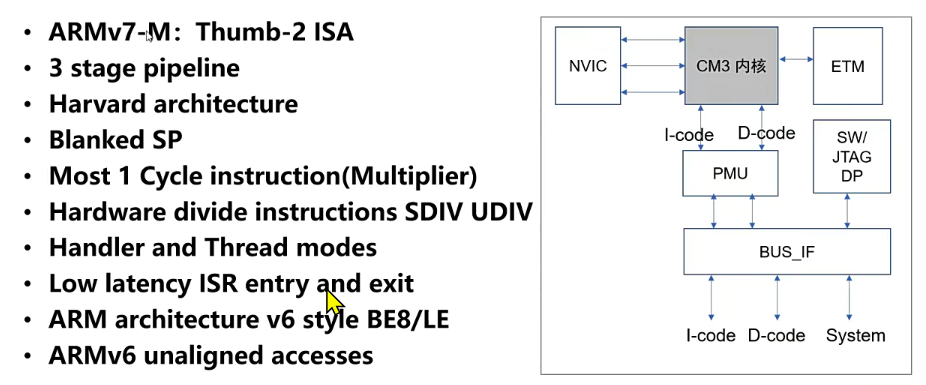

Cortex CM3 内核特性

- 支持Thumb 16bit的指令集,ARM 32bit指令集;ARM指令集位宽多,功能更强

- 支持Thumb-2 ISA 可以支持16bit和32bit指令

- 支持3级流水-取指\译码\执行的时候可以同时执行

- harvard architecture - 将指令存储和数据存储进行分开

- blanked SP - 有两套堆栈,一个是系统进行访问的,一个是用户进行访问的

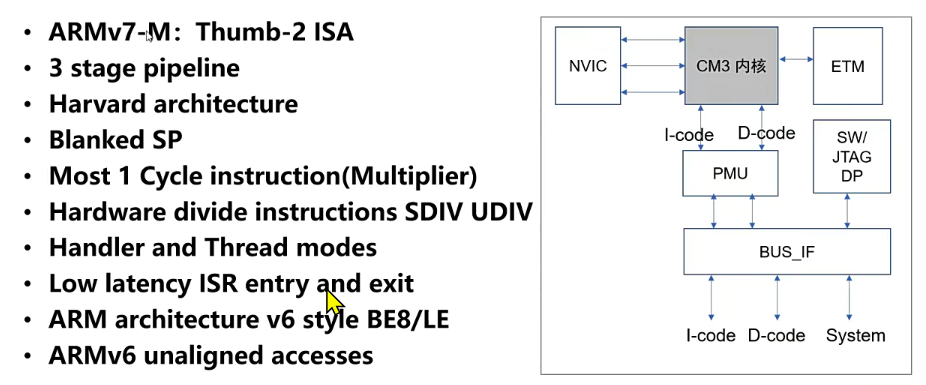

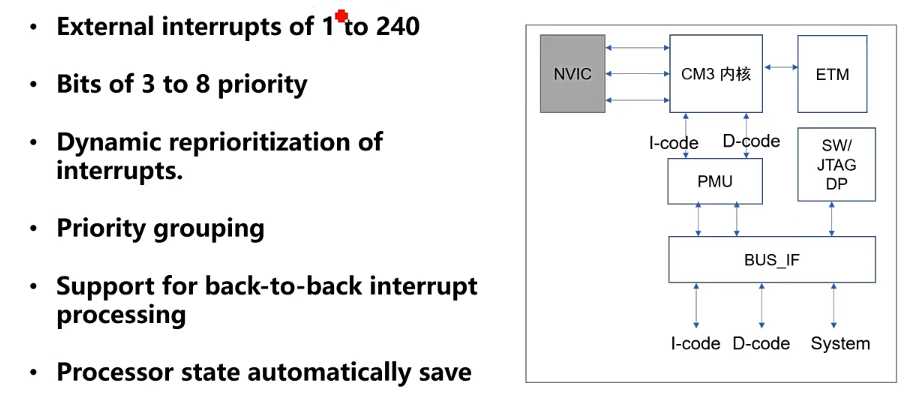

Cortex CM3 嵌套中断向量

- priority - 不同的中断可以设置不同的中断的优先级

- back-to-back - 中断的咬尾操作,高优先级的中断可以终止低优先级的中断,低优先级的中断不用进行出栈操作,可以提高中断处理程序的执行效率

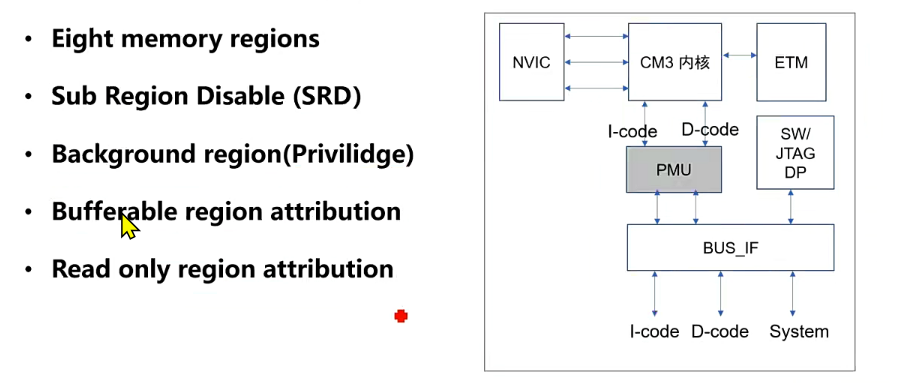

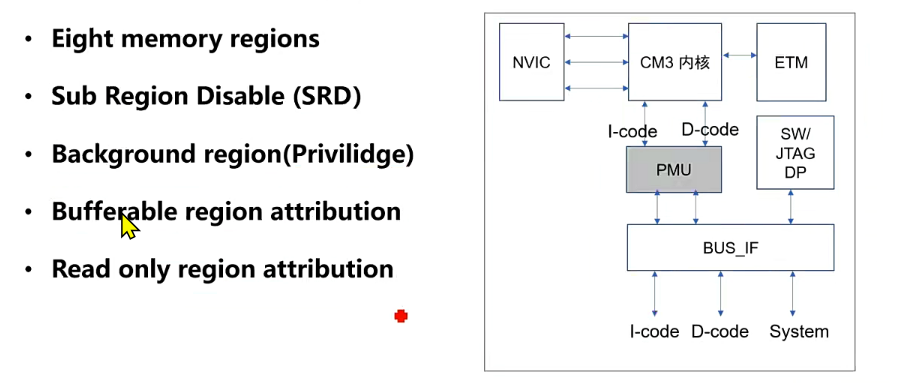

Cortex M3 MPU保护单元

- 支持8个memory region - 可以指定不同区域设置不同的访问权限

- 设置缓存进行加速

- 可以设置读写权限

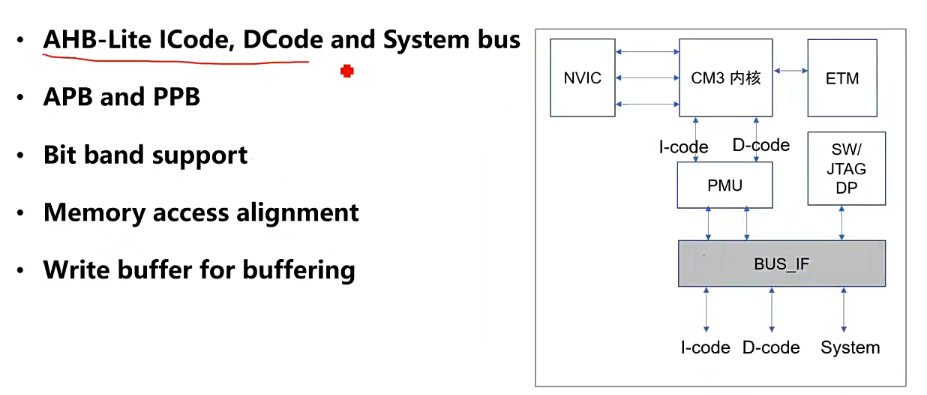

Cortex M3 总线接口

Cortex M3 低成本调试接口

posted @

2023-12-11 22:27

Icer_Newer

阅读(

452)

评论()

编辑

收藏

举报