SV 数据类型

Verilog数据类型

- 变量类型 - 用于存储值

- 线网类型 - 用于连接硬件模块

- reg - 在硬件中可能会被综合成DFF和Latch

线网类型

- 线网的驱动 - 可以是门,也可以是实例化的门

- 变量只能通过过程赋值进行赋值 - initial/always

- integer - 32bit,有符号数 - 通常循环变量的时候会使用

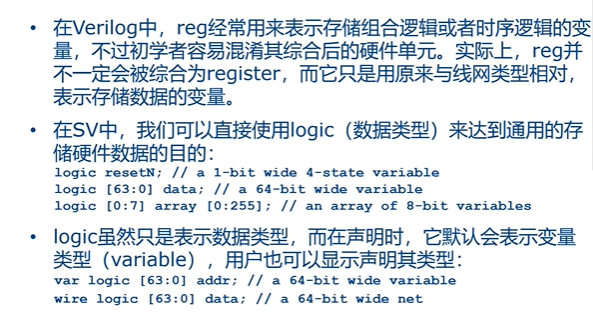

System Verilog新添加的数据类型

- x - 真实的电路中是没有的x的状态,x表示真实电路中不稳定的状态(可能是1或者是0)

- z - 表示没有驱动(悬空),如果DFF没有复位的时候,Q端是x;D端如果没有输入(驱动),Q端就是z

- SV - 具有数据类型

- SV中对于线网类型 - 通过使用连续赋值;变量类型使用连续赋值(assign)或者是过程赋值(always)

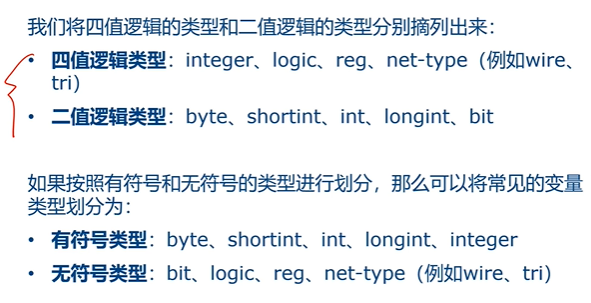

- 数据类型的三个方面:线网类型还是变量类型\2值逻辑还是4值逻辑\有符号还是无符号

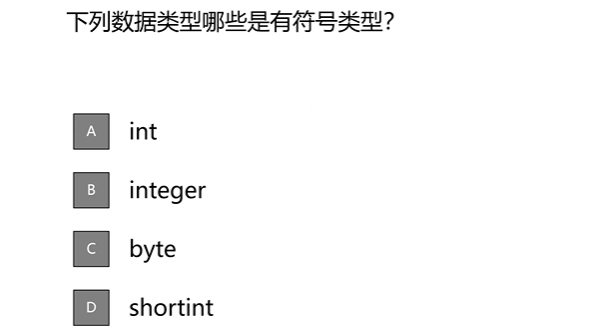

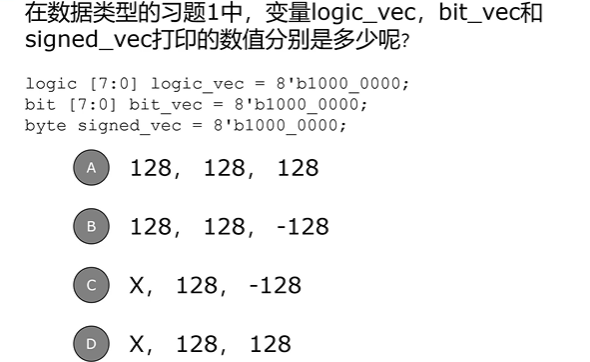

- BD

SV中的assign连续赋值可以赋值给logic(var)类型吗?

- 在SV中可以使用logic替代(wire和reg)

- 多驱动源的情况下或者设计模块端口是双向的(inout)的时候 - 不适用logic

module tb;

wire w1;

logic r; // logic (var)

assign w1 = 1'b1;

assign r1 = 1'b0;

wire w2;

var logic r2;

assign w2 = 1'b1;

assign r2 = 1'b0;

initial begin

#1ns;

$display("w1 = %b,r1 = %b",w1,r1);

$display("w1 = %b,r1 = %b",w2,r2);

end

endmodule

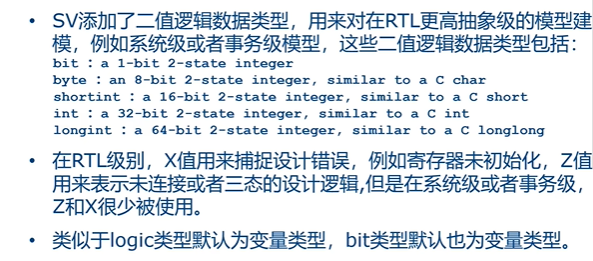

四值逻辑数据类型

- logic - 硬件中可以综合,软件中也可以使用

- logic [63:0] - 每1bit都是独立的,只要有一位是x,返回的数值就是不确定的

二值逻辑数据类型

- 二值逻辑bit/byte/shortint/int/longint - 可以进行综合,但是综合出来的电路会失真,使用二值逻辑表示不了延时和亚稳态

- bit类型也是变量类型

- int(二值逻辑)/integer(四值逻辑)/shortint/byte

有符号数和无符号数

- 有符号数和无符号数不要进行运算

- 硬件验证和测试,发送激励的时候只需要考虑发送0和1就可以,不需要发送x和z,所以使用二值逻辑即可

- SV中的四值逻辑和C中变量没有直接的对应关系

内建数据类型

仿真行为

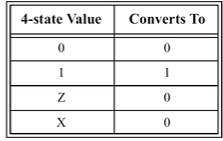

- 四值逻辑转变为二值逻辑的时候,x和z转变为0

其他类型

- void - 其他类型