SV Interface and Program 2

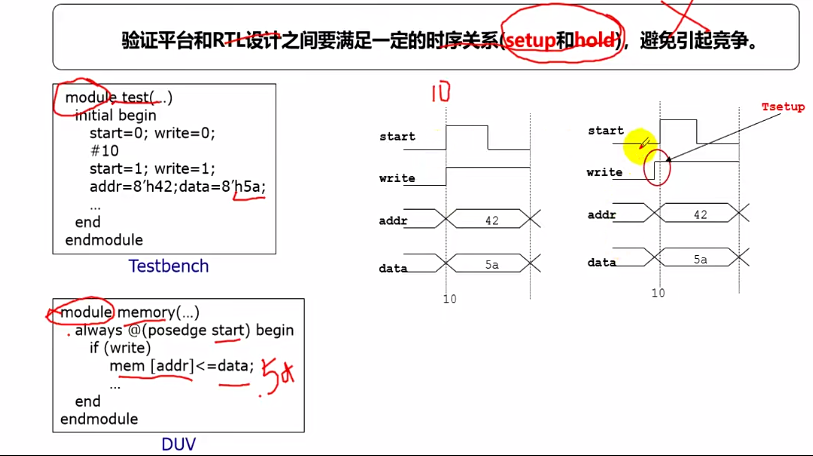

Clocking:激励的时序

- memory检测start信号,当start上升沿的时候,如果write信号拉高之后,将data存储到mem中

- start\write\addr\data - 四个信号是同时在start上升沿进行,在采样的时候,testcase和Dut都是module,write采样的时候,有时候会采样到上升沿之前的值或者上升沿之后的值,需要规避这种情况

- 信号在时钟的驱动下发生跳变,会有delta-delay产生,并且delta-delay是不确定的,所以会造成采样的不确定性,使用clocking模块进行控制

- 需要给write信号稳定之后进行采样

- 所以设置clocking模块进行控制

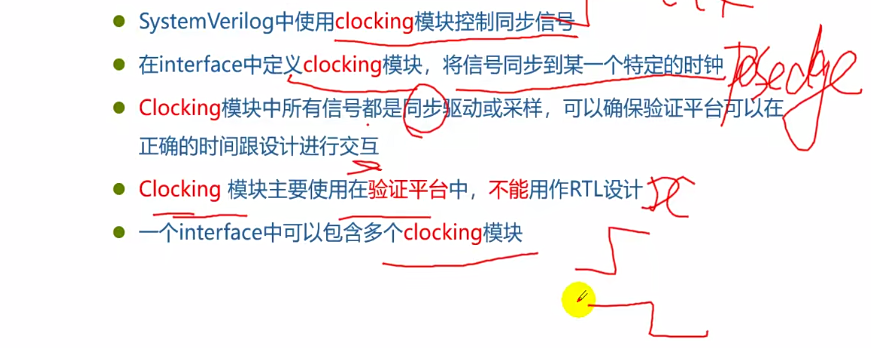

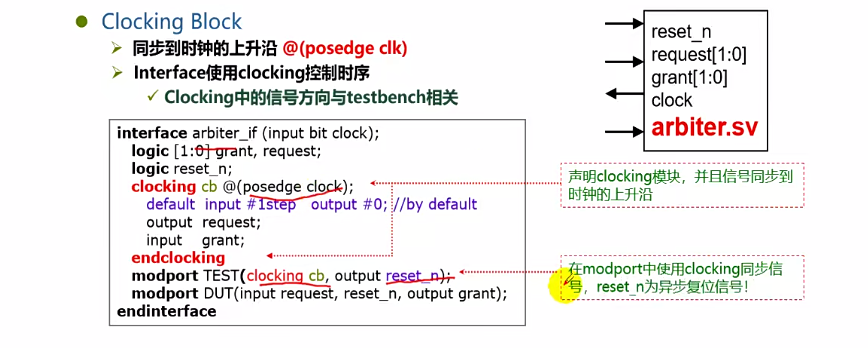

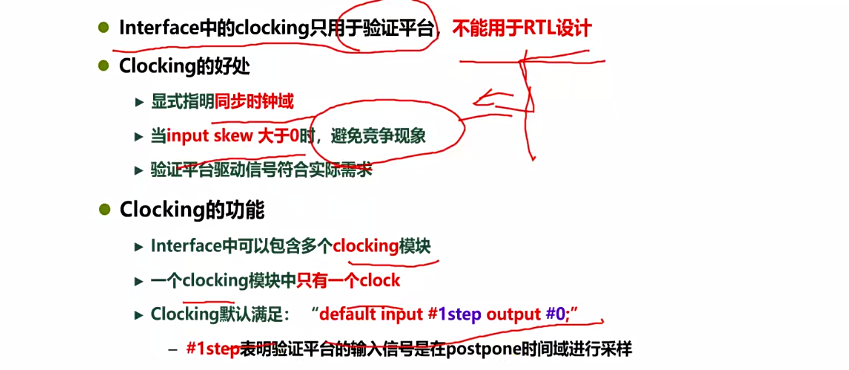

- 在clocking block定义在interface中,是不可综合的

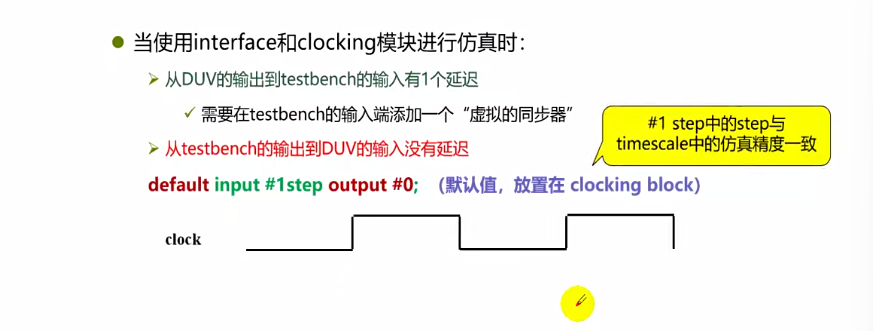

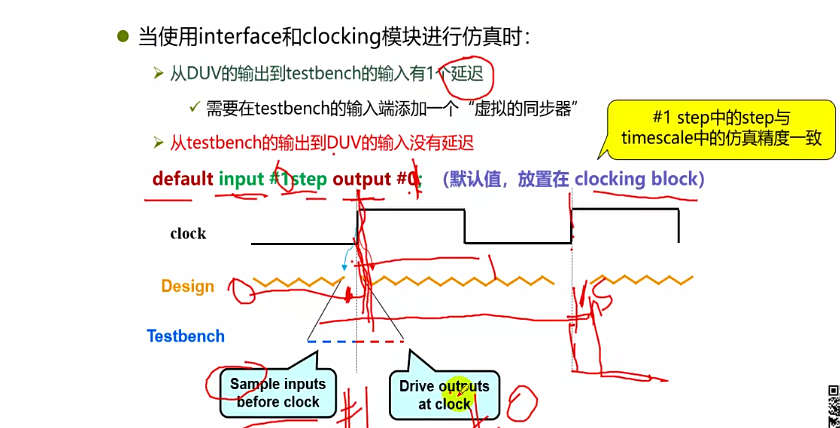

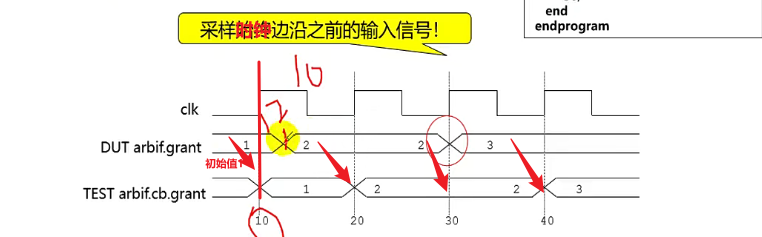

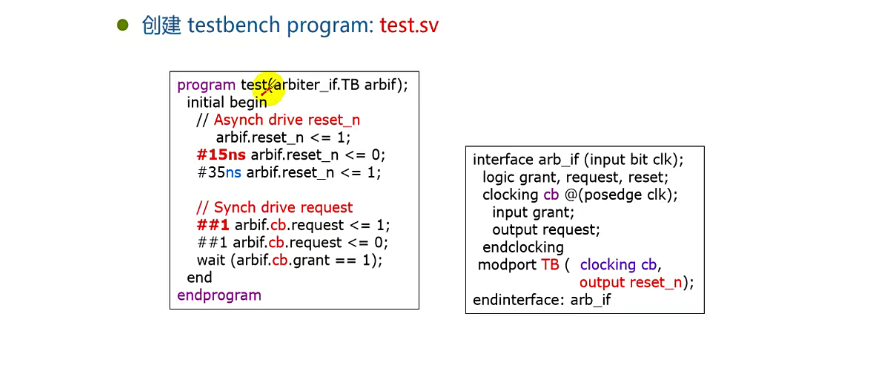

- 对于testbench,input(DUT输入)要延迟进行采样,就是在时钟上升沿之前1个时间单位采样

- output(输入给DUT) - 没有延时时间

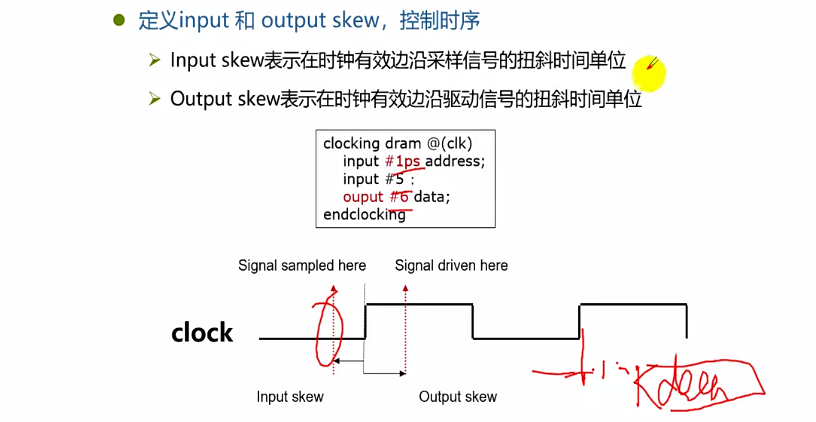

- input向时钟上升沿之前多少时间单位进行采样,output向时钟上升沿之后多少个时间输出

// 同步到时钟上升沿

clocking cb @(posedge)

default input #1step output #0;

output request;

input grant;

endclocking

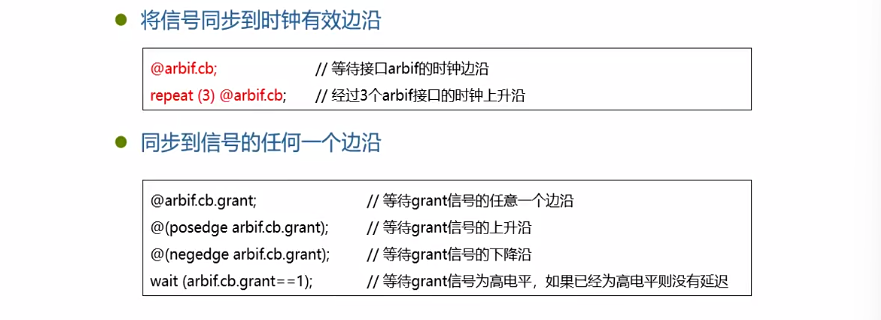

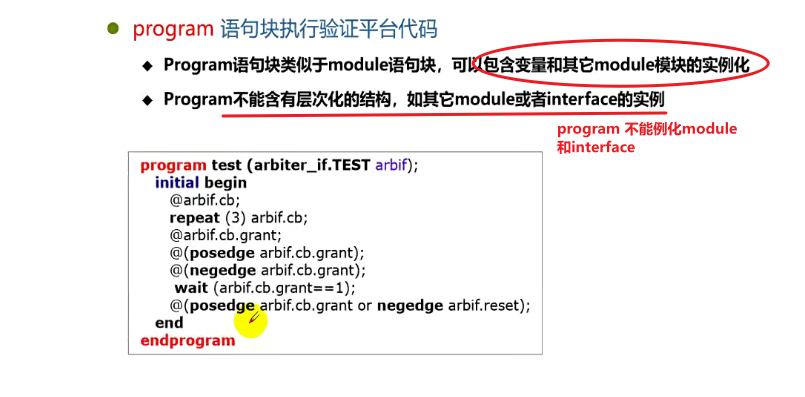

//将信号同步到时钟有效沿

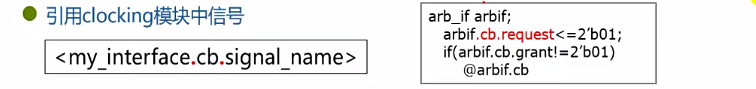

@arbif.cb; // 等待接口arbif的时钟边沿

@(posedge arbif.clk) //等待接口arbif的时钟边沿

repeat(3) @arbif.cb; // 经过3个arbif接口的时钟上升沿

// 等待n个时钟周期 ##n - 阻塞语句

##2 arbif.cb.request <= 0; // 经过两个时钟周期之后进行赋值

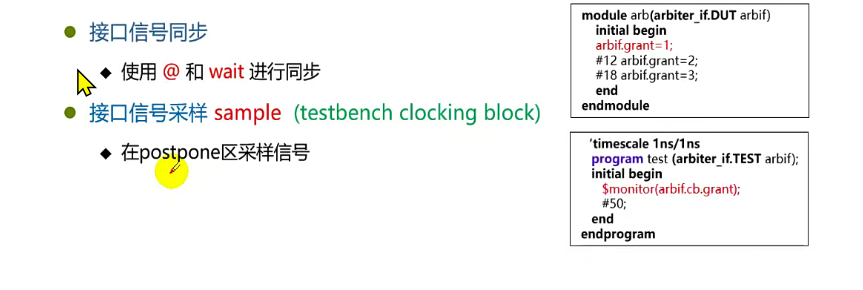

- 同步信号,驱动输出信号使用非阻塞赋值,采样输入信号使用输入信号

- 非同步信号,阻塞赋值

forever begin

if(request == 1)

grant <= 1; // forever中没有时间推进语句,会造成死循环

end

总结

- Clocking模块中信号的方向与testbench相关

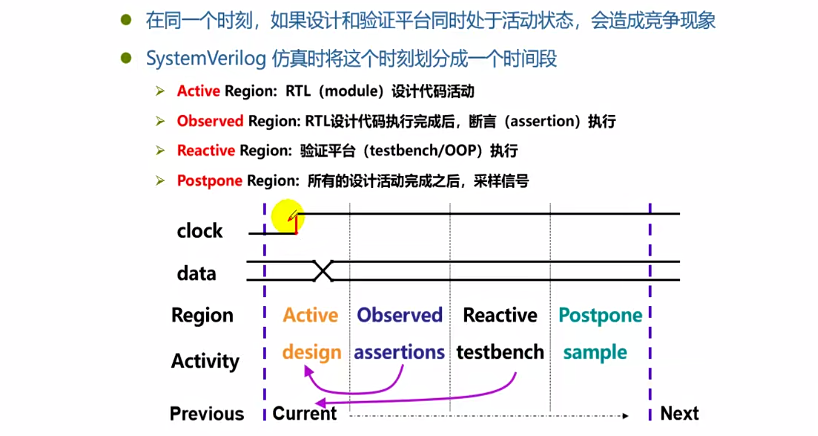

仿真时间域

- 不同代码的执行是有先后顺序的

- active region - 执行设计代码

- observed region - 执行断言

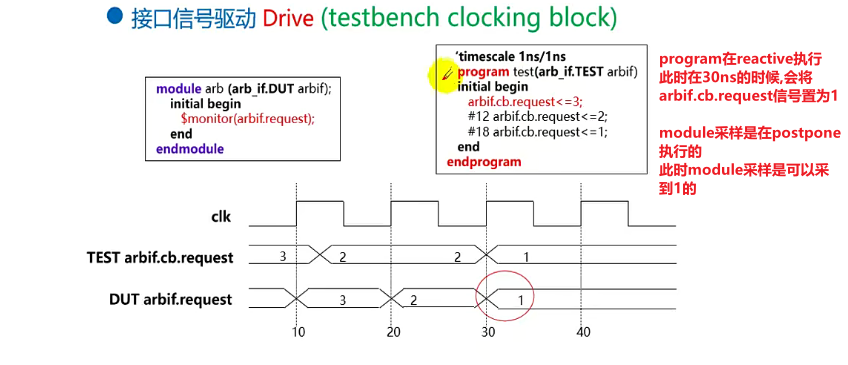

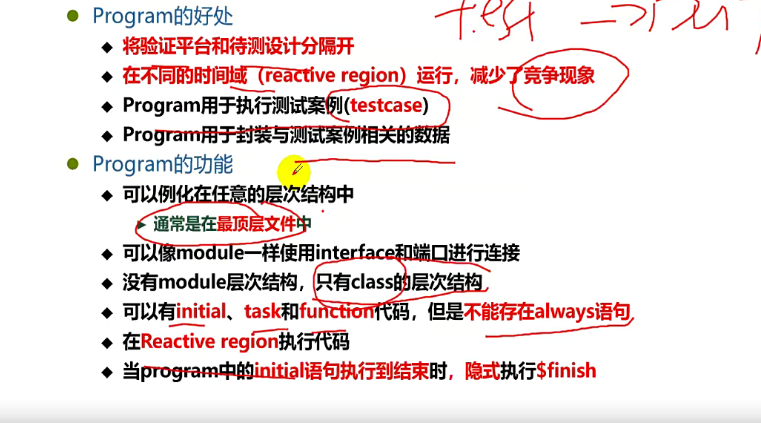

- Reactive region - testbench/oop,验证平台和dut都是module,仿真工具如何区分,testbench会用program进行定义,program可以认为是testbench

- Postpone region - sample

- program - 会在reactive region进行执行

- module - 会在active region进行执行

- 采样的时候采样到的是时钟之前的信号

Program block

- program语句只能用于testbench,不能用于design

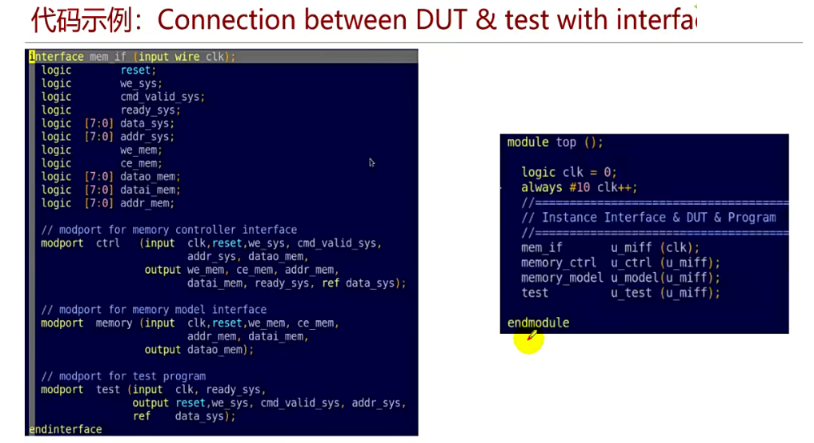

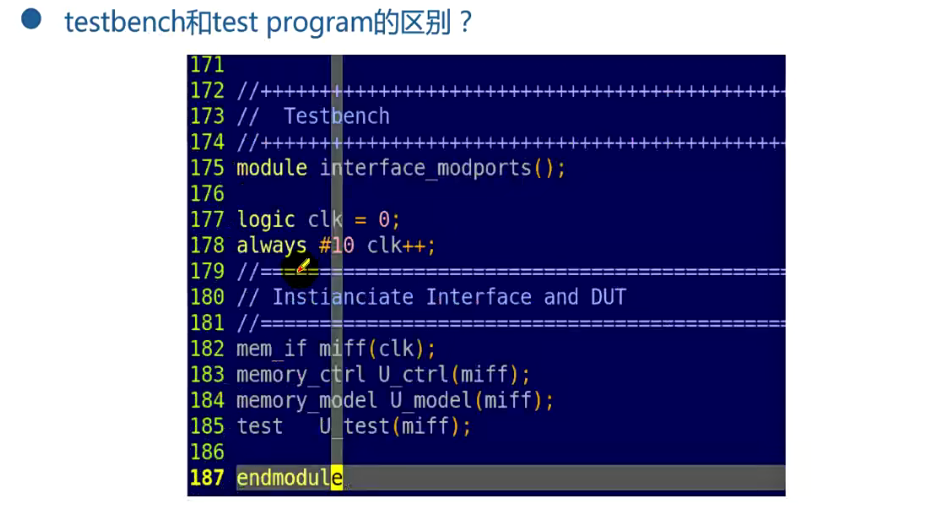

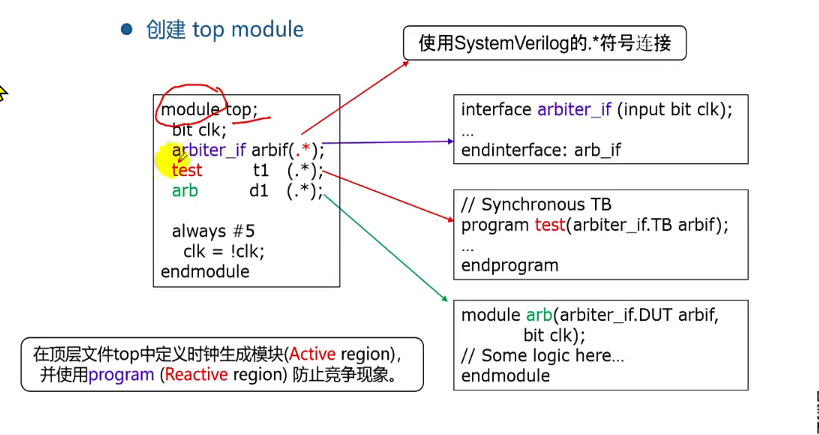

验证平台顶层文件-top文件

- tb_top必须是module

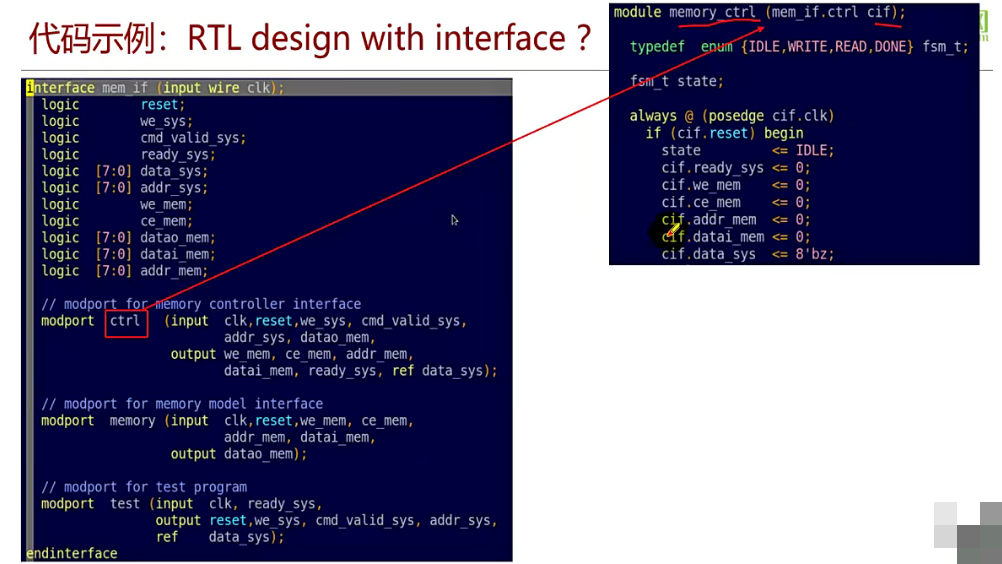

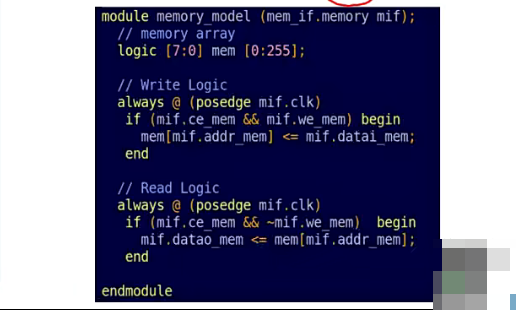

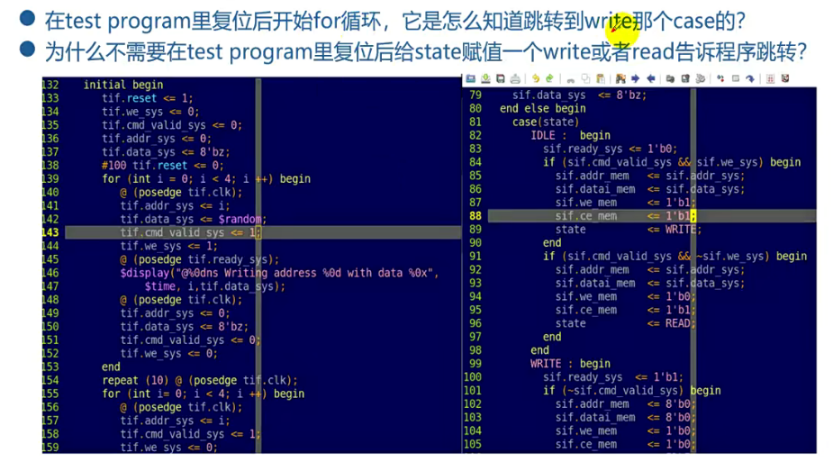

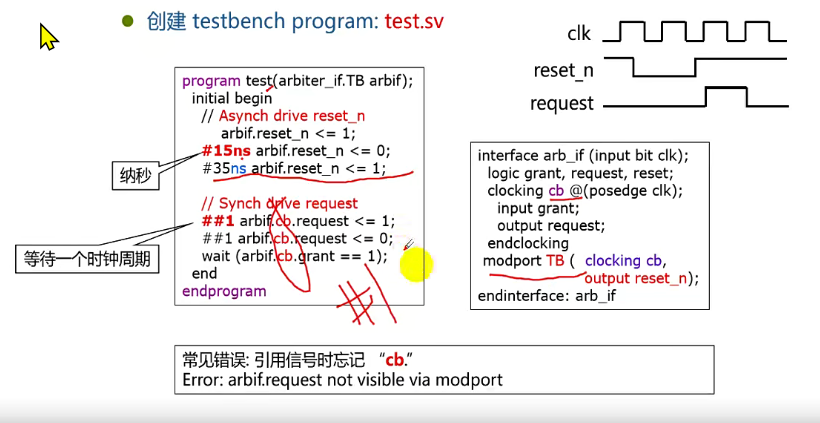

代码示例