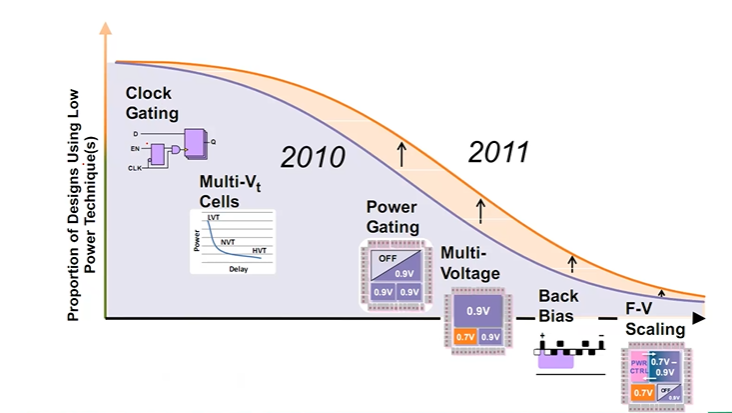

Mainstream Low Power techniques

- Low Vth - 阈值电压比较低,翻转时间小,漏电流比较大,功耗大,速度快

- High Vth - 阈值电压比较高,翻转时间长,漏电流比较小,功耗小,速度慢

- 使用多阈值的器件,处于关键路径上的器件使用Low Vth,不在关键路径上的使用High Vth

- 兼顾PPA

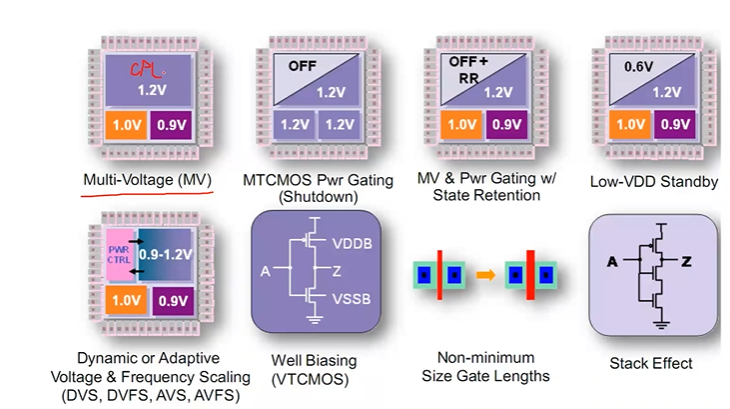

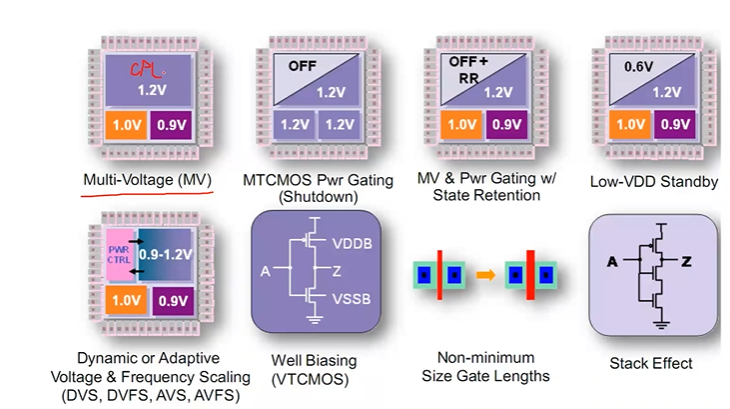

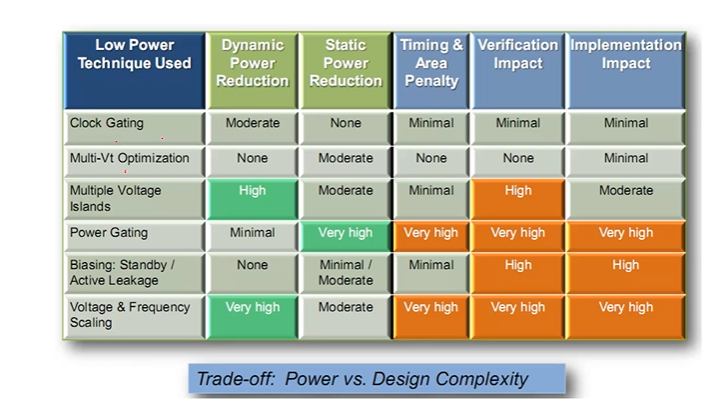

Advanced Low Power techniques

- 多电压域设计

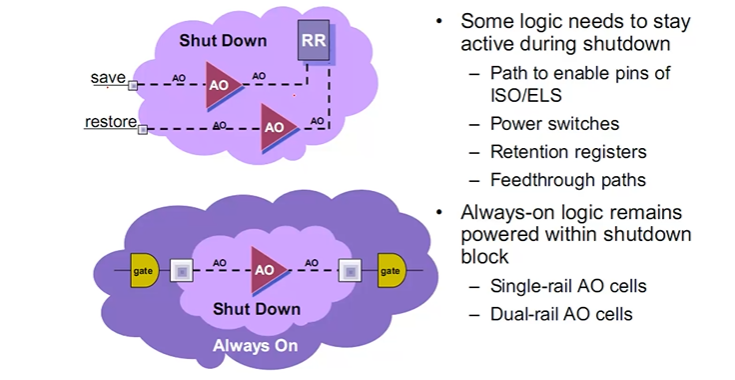

- power gating - 对于某些不用的电压域可以关掉(shutdown)

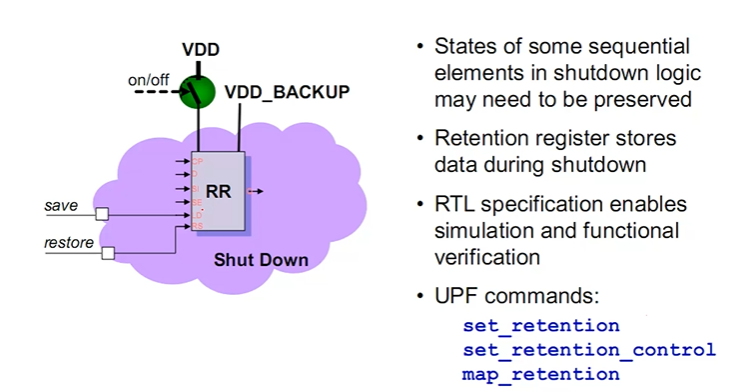

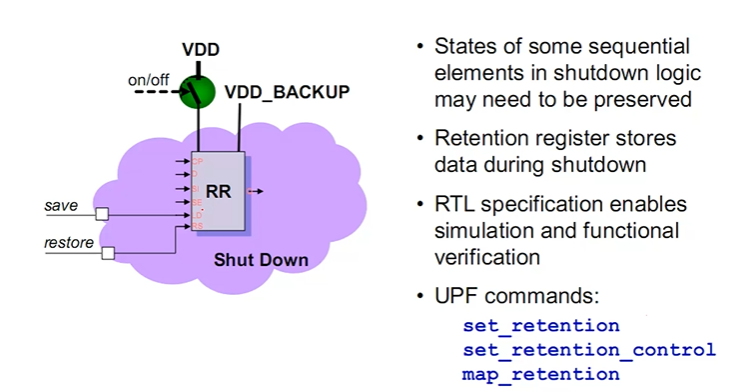

- 寄存器,电压关掉之后,其中保持的数据会消失;设置Retention register,用于存储寄存器的状态,这个寄存器一直维持上电状态

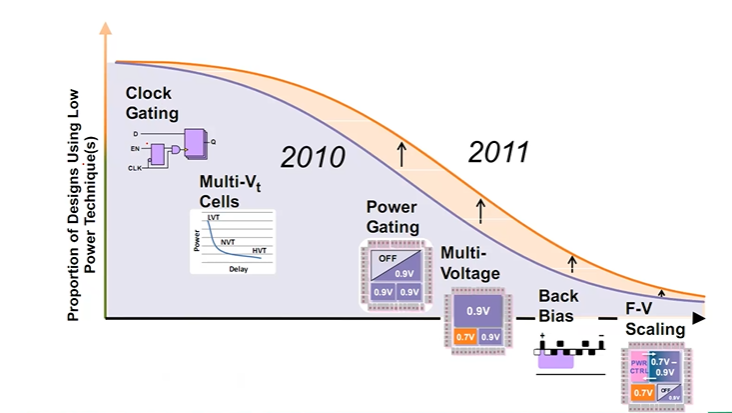

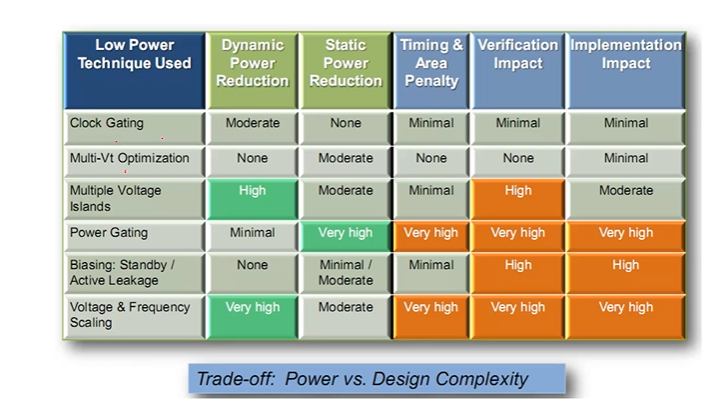

Adoption of low power techniques

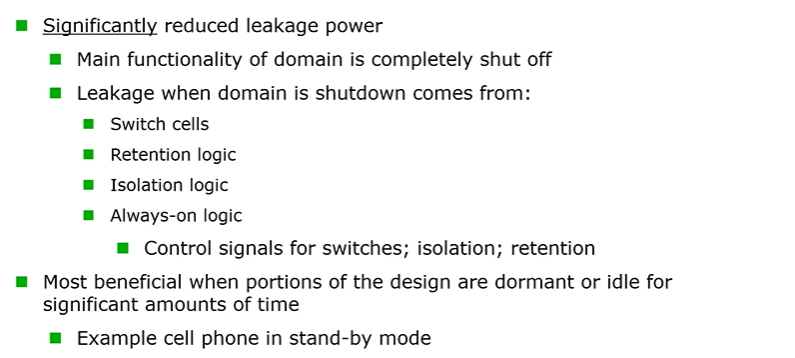

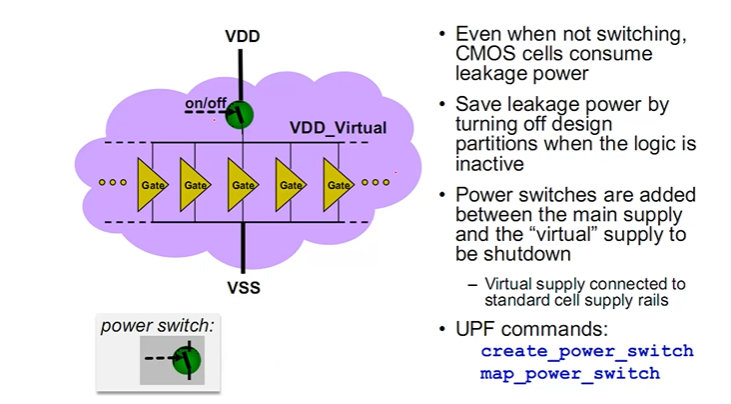

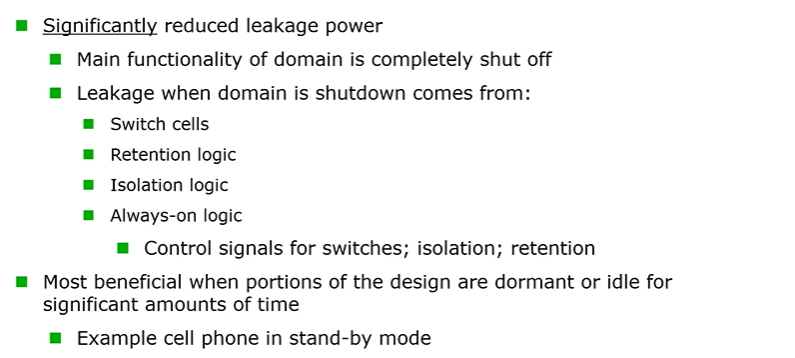

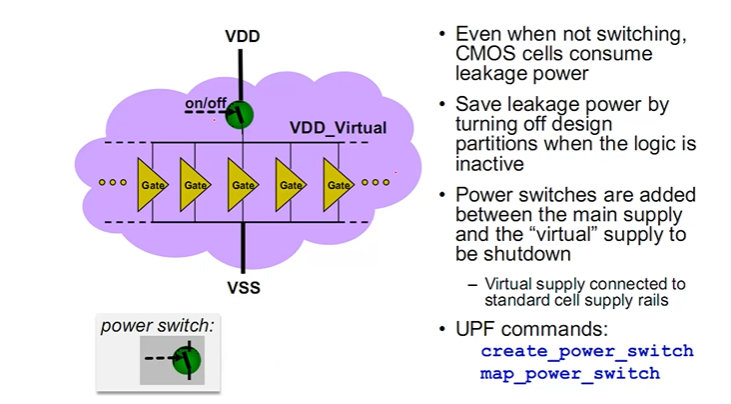

Power Gating(MTCMOS)

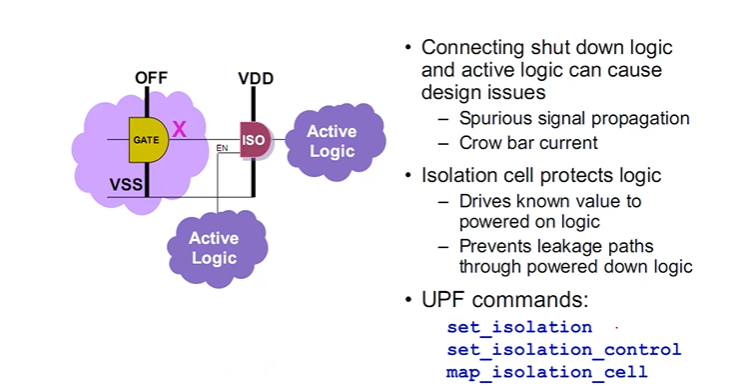

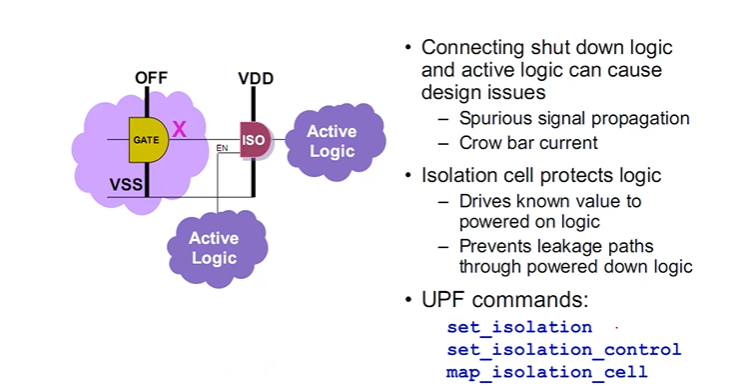

- VDD和logic连接的部分插入一个power switch(mos管),sleep enable = 1的时候,mos管关断,Logic没有供电,可以节省功耗,输出为Z(高阻态);如果将Z输入给其他模块会产生亚稳态,所以插入isolation模块,这个模块是为了关断之后,输出给其他模块输入没有影响的值

Power gating advantages

Power gating costs

- 需要增加一些面积

- IR-drop - 掉电瞬间,其他模块不太稳定

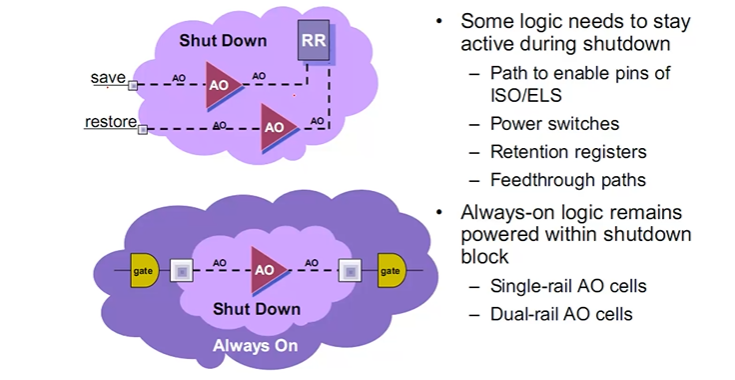

- 控制信号需要插入buffer,不能掉电

- isolation 模块,隔离高阻态信号传给其他模块

- retention logic - 将掉电之前的状态值保存

- 验证复杂度增加

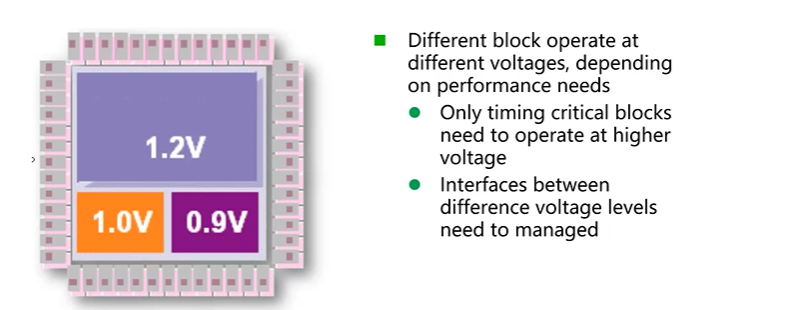

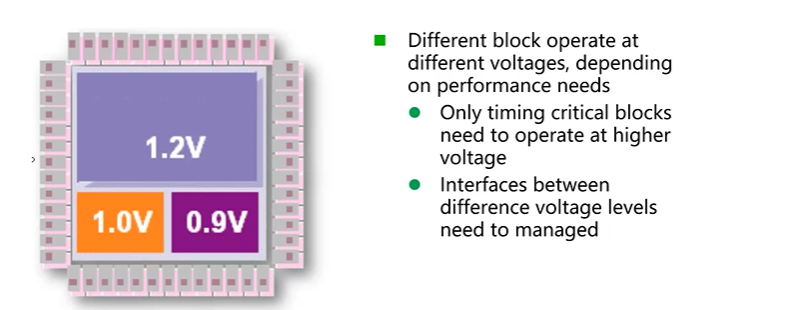

Multi-Voltages

Multi-Votages advantages and disadvantages

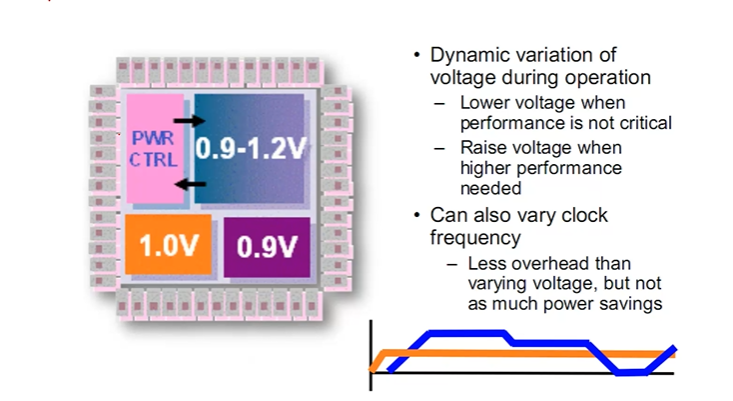

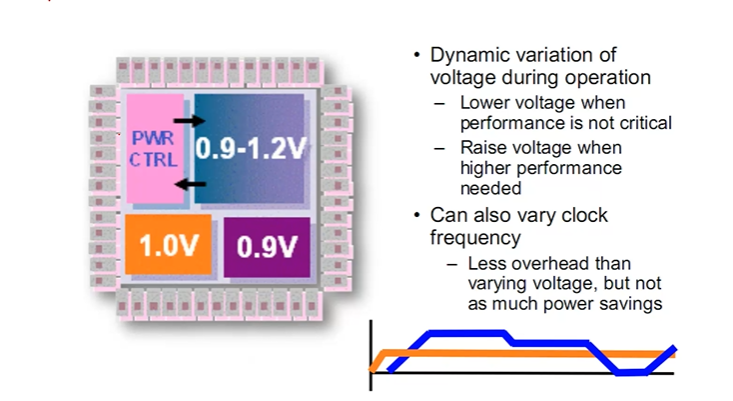

DVFS(Dynamic Voltage and Frequency scaling)

- 动态调控电压和频率,可以根据场景,自适应的去调节电压和频率

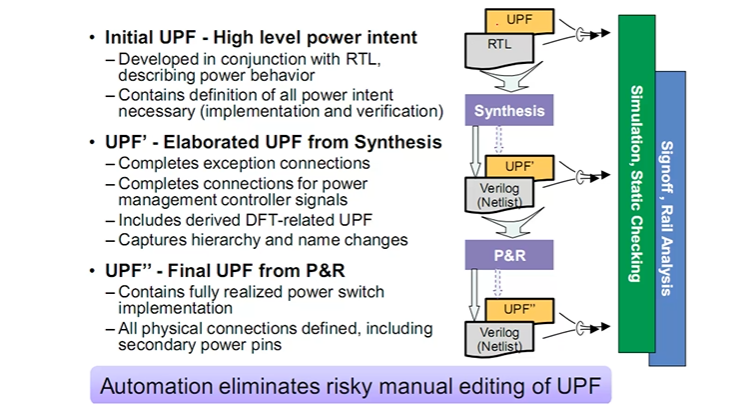

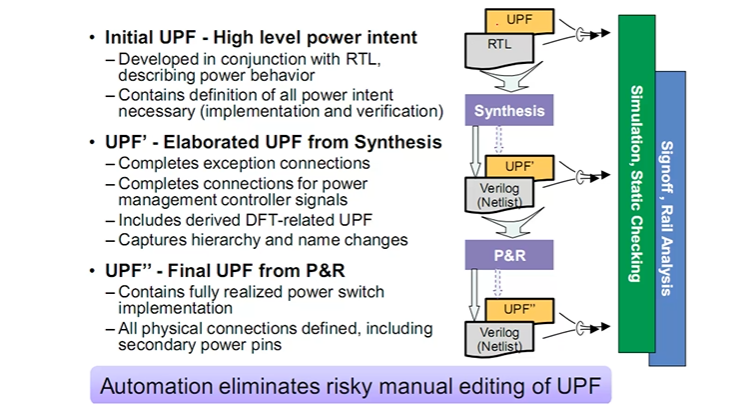

Low power impact on Design flow

Why do we need UPF

- 对于ICG,可以在写RTL的时候进行代码风格规范

- 其他低功耗设计方法,可以通过UPF文件进行引入

- UPF就是用于描述低功耗设计的文件,在整个芯片设计周期中都存在

UPF & RTL

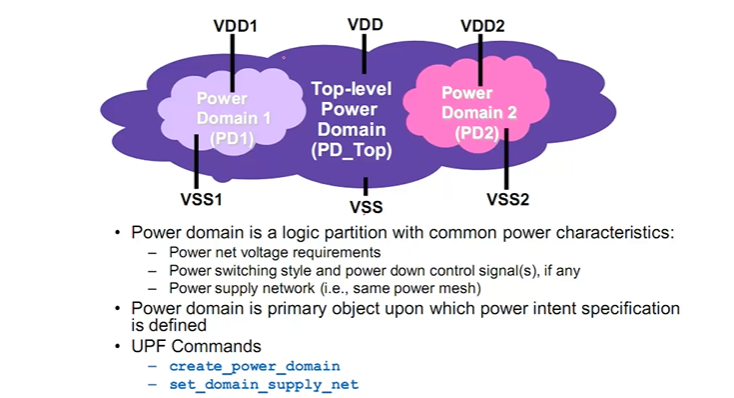

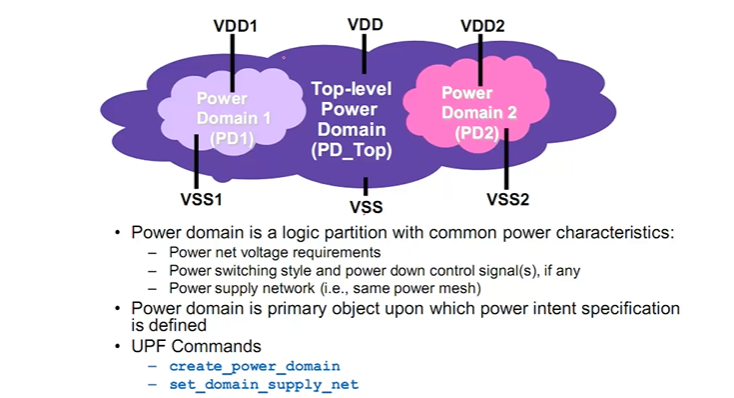

Power domain

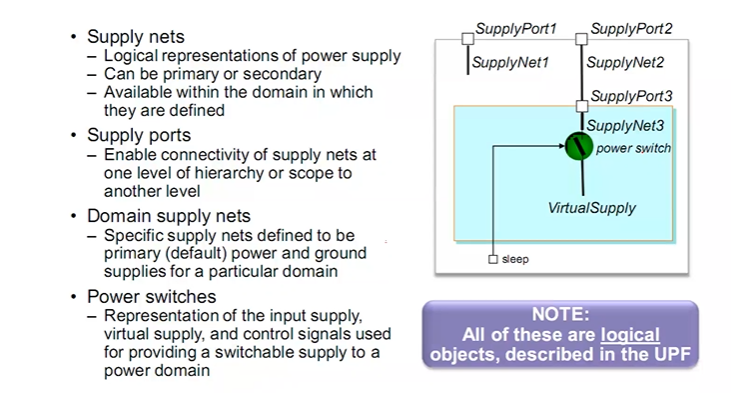

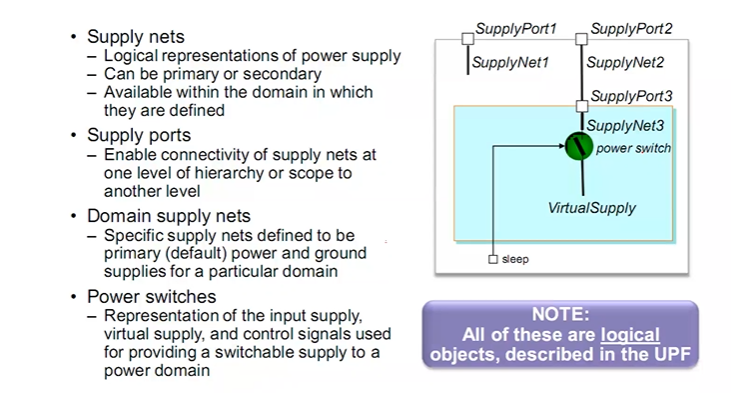

Power supply

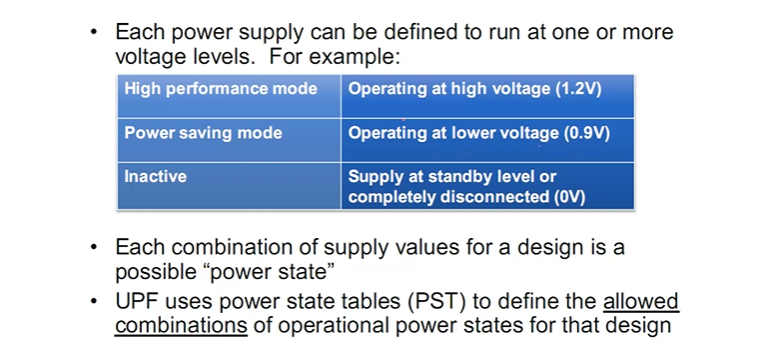

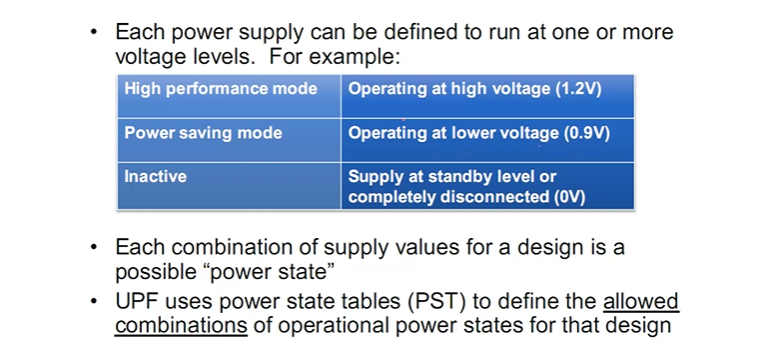

Power states table

Low lower design require special cells

Level shifter

- LS - 高电压域转到低电压域,低电压域转到高电压域

- “1”和“0” - 都是有一定范围的,1V - 传递到 1.6V-2V之间的高电压域,传递过来可能在当前的电源域表示0.需要设置Level_shifer

Isolation cell

- 对于掉电时钟域,需要设置Isolation cell进行隔离

Power switch

Retention Registers

- 掉电之前,将寄存器值存储到RR中,上电之后,回复之前的值

Always-On cells

UPF Example

UPF FLOWS

posted @

2023-11-28 22:09

Icer_Newer

阅读(

134)

评论()

编辑

收藏

举报