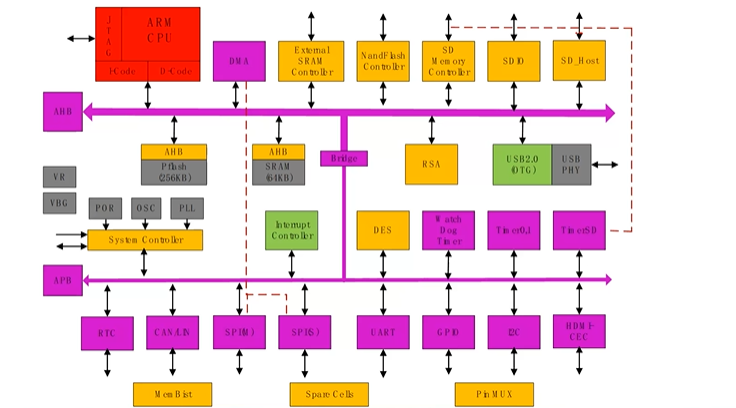

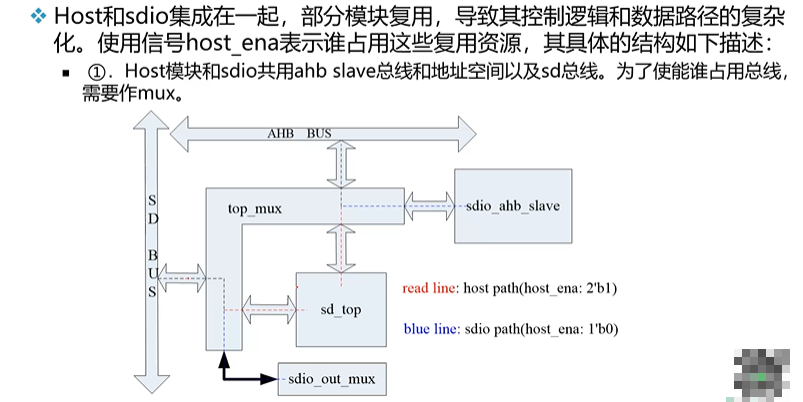

SD Host控制器的系统集成

控制器集成需求

- SD Host可以从外部读取数据存储到SRAM和eFlash或者可以从内部读取数据输出到外部存储

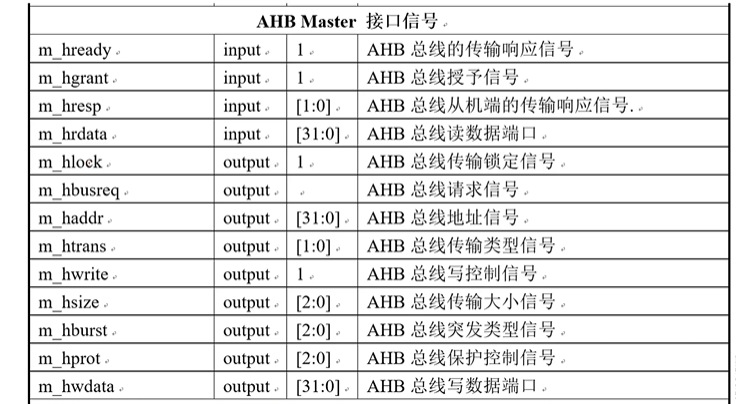

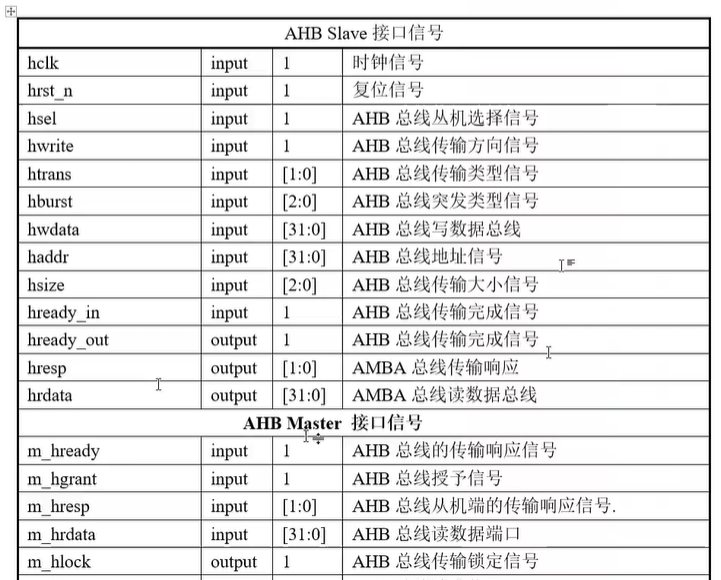

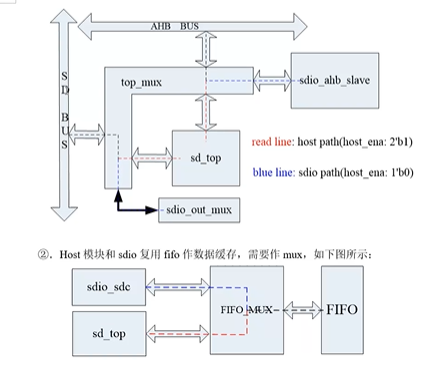

AHB Bus

- slave接口用于配置

- master接口作为主设备,DMA可以控制总线,传输数据

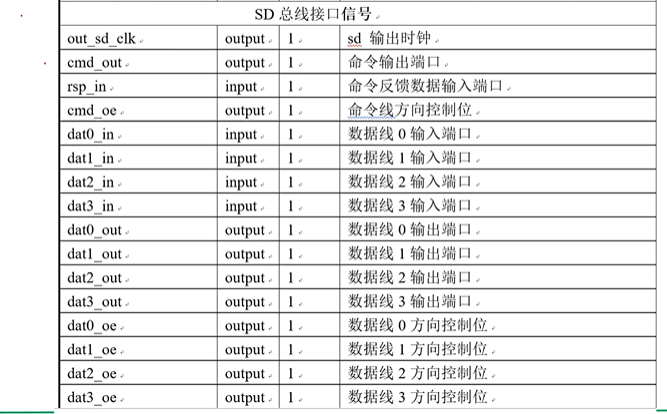

SD Bus

- CMD和data都是inout类型的,可以出入和输出

- cmd_oe - (output enable)

- cmd_oe = 1,输入的信号就是rsp_in,命令反馈输入接口

- cmd_oe = 0,输入的就是cmd_out,cmd_out = 1 输出数据,cmd_out = 0,输出z

- 将一个cmd分为三部分,再将这三部分驱动到pad上,芯片内部不实现三态逻辑

- data总线也是同样的道理,分成data_oe,data_out,data_in

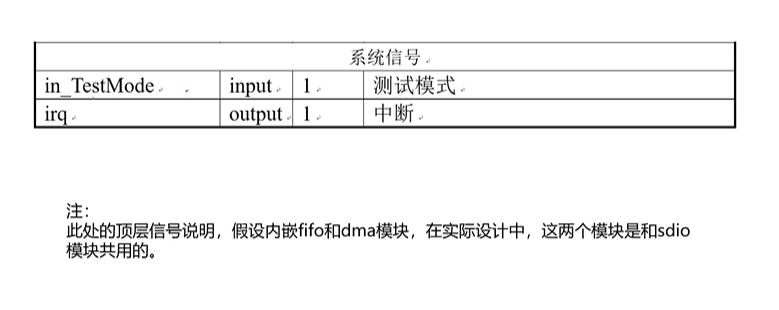

DFT & Interrupt

- 在进行设计模块的时候,可以预估面积,可以考虑将面积比较大的模块和其他比较类似的模块进行复用

控制器集成需求

SD Host集成需求文档

SD Host微架构设计文档

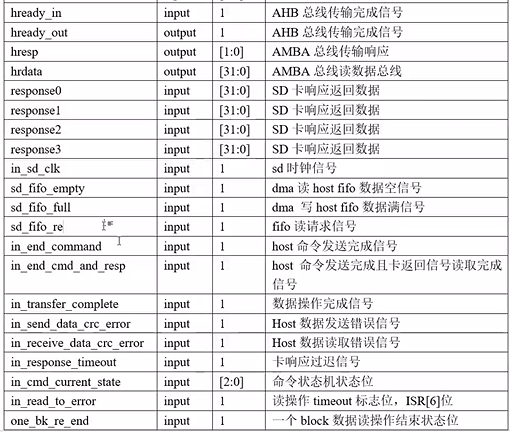

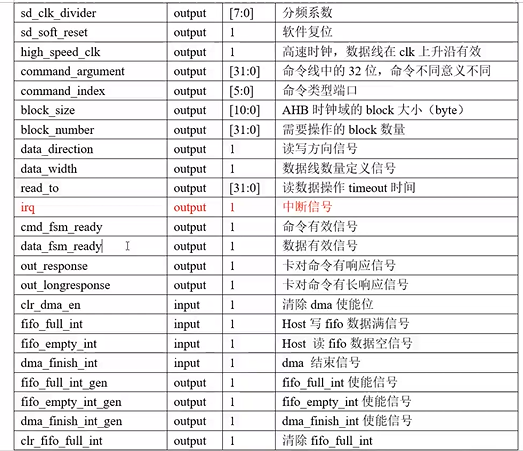

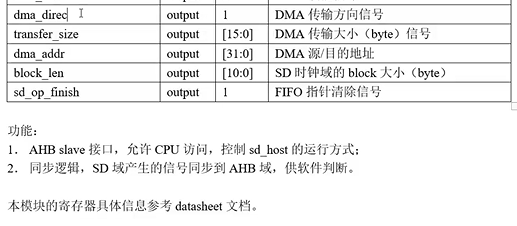

SD_if模块

ahb总线接口模块,用于软件的访问控制

接口在微架构设计文档阶段确定的

1、先定义明确的接口

2、按照需求方的角度收集信息

-

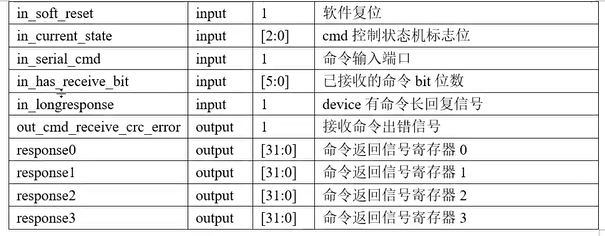

reponse0-response3 -- 是读取回来的数据,ahb总线是32bit,就按照ahb总线的宽度来

-

reponse中的start bit,index,crc是不需要回传的,只要将content回传就可以

-

sd_clk输入,ahb_slave_if(sd_if)模块,既需要和ahb bus通信又需要和sd bus进行交互,所以需要进行数据的同步处理(通过打拍的方式),所以需要输入sd_clk

-

sd_fifo_full 和 sd_fifo_empty - fifo的空满状体需要上传给cpu,fifo为空的时候才能发起读命令,fifo满之后需要cpu驱动dma将fifo中的数据搬移,fifo的空满状态需要以中断的形式上报,所以需要输入fifo的空满状态

-

了解cpu需要获取那些状态信号

-

sd_fifo_re - fifo读请求

-

in_end_command - host发送完成,信号来自于sd时钟域,如果要使用这个信号需要对其进行打拍处理

-

in_end_cmd_and_resp - 表示当前命令和相应都结束了,resp结束之后,cpu会读取resp的寄存器,查看其中的内容

-

in_transfer_complete - 表示数据传输操作完成

-

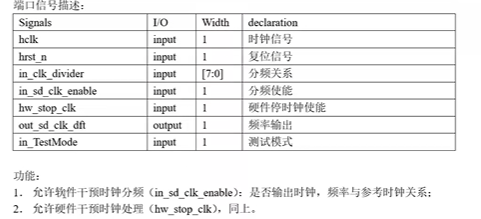

sd_clk_enable - 软件时钟门控

-

hw_stop_clk - 硬件停止sd_clk模块时钟输出

-

dma_en - 软件的置位,是dma启动

-

clr_dma_en - 硬件的清0信号

sd_clk模块

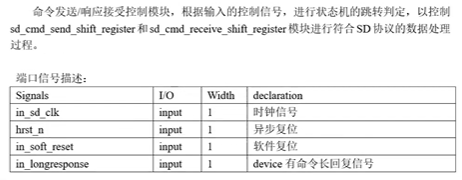

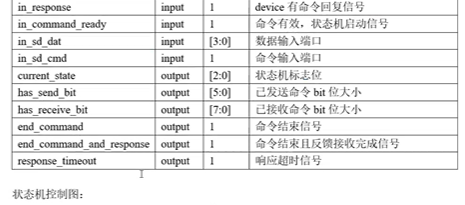

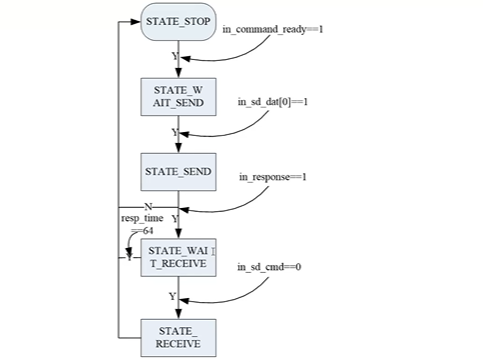

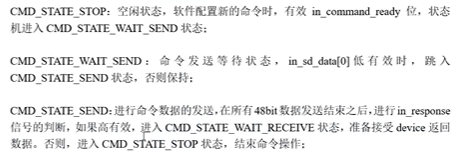

sd_cmd_fsm

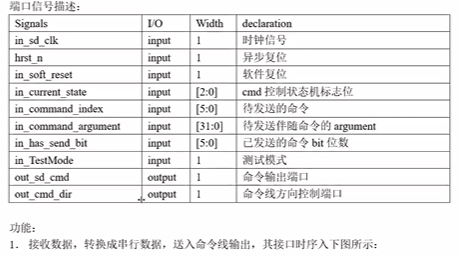

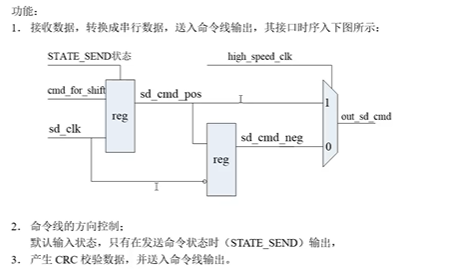

sd_cmd_send_shift_register模块

sd_cmd_receive_shift_register模块