芯片项目介绍-01

Linux基本操作及Gvim基本操作

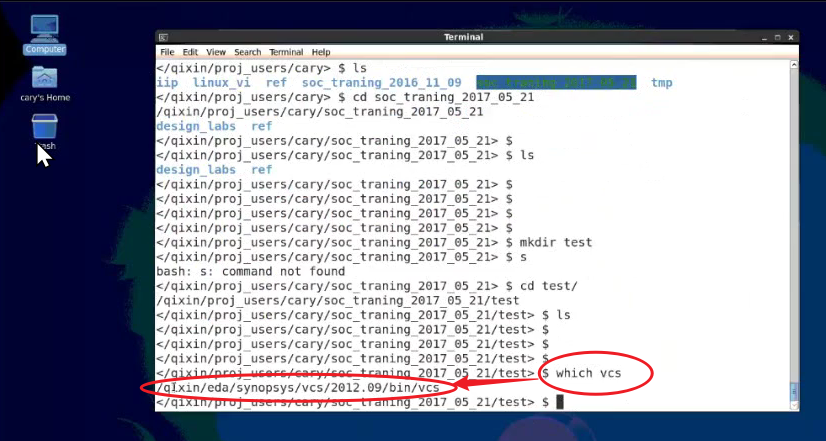

通常使用Linux系统进行设计

# 创建文件夹

mkdir myproj

mkdir design_labs

cp -rf 文件路径 复制到的路径

chmod 777 文件

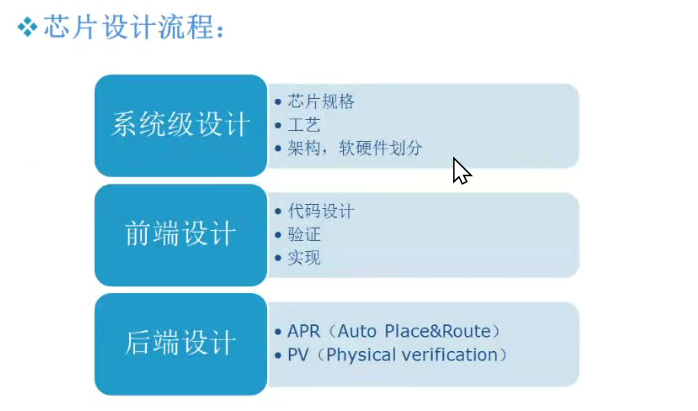

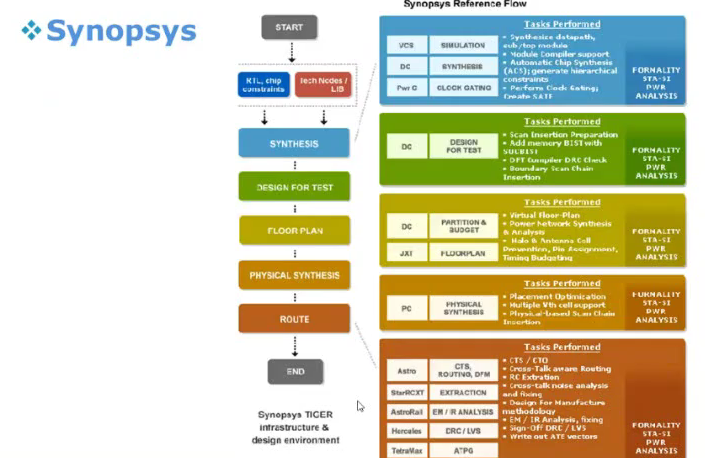

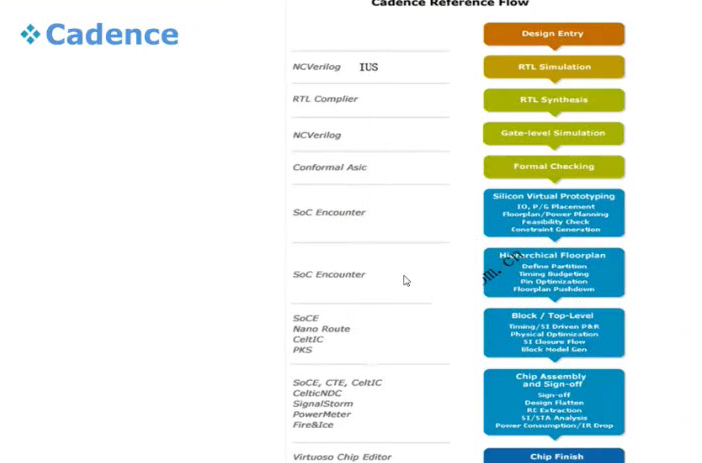

芯片产品流程

综述

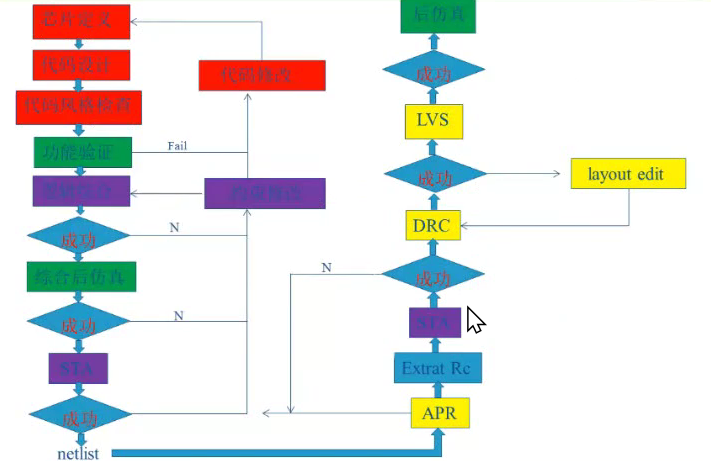

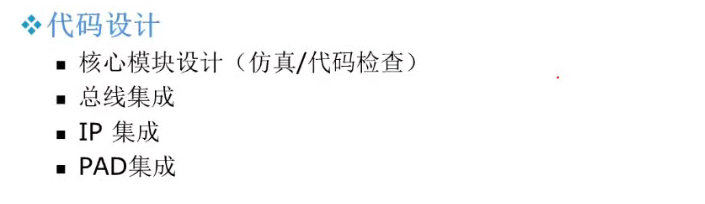

- 代码设计 - 迭代过程

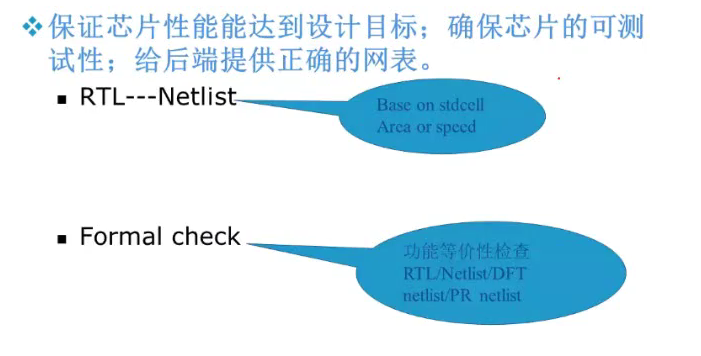

- 综合之后会进行formal check,形式验证

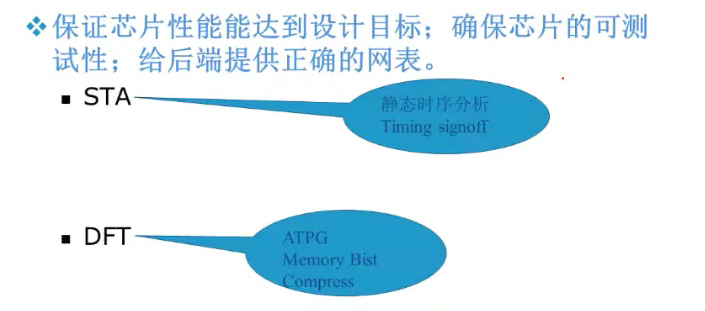

- 综合之后会进行初步的STA

- APR之后抽取RC之后,进行正式的STA

设计

中端

- RTL代码不考虑跑多快,中端之后RTL转变为网表,添加很多约束,进行速度和面积的平衡

- Formal Check:RTL和综合之后的网表进行formal check,综合之后的网表和插入DFT之后的网表再进行一次Formal Check

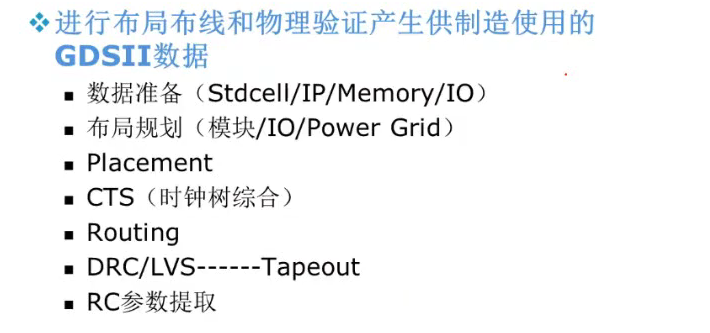

后端

- CTS - RTL设计的时候,寄存器的posedge默认是同时发生的,但是实际在布局布线的时候寄存器存在的位置不同,时钟到达的时间不同,posedge是不同步的,需要插入一些buffer,保证posedge是同时发生的

- 短路径插入大的buffer,长路径插入小的buffer

- RC参数提取之后进行时序分析

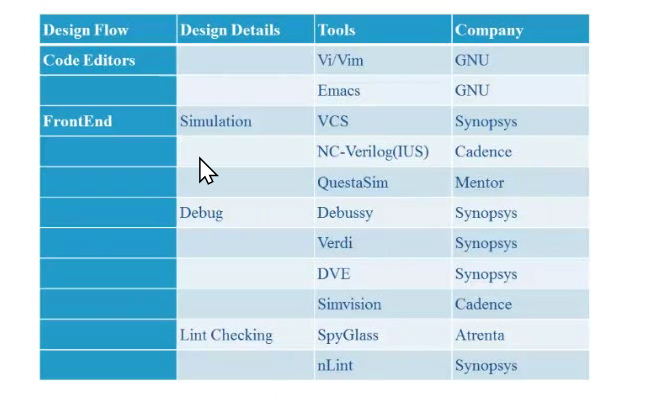

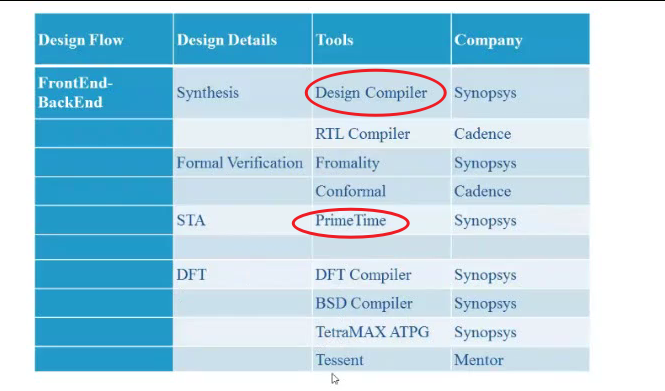

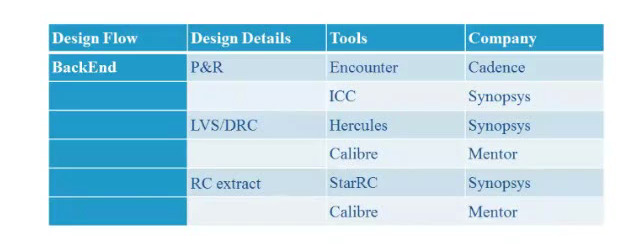

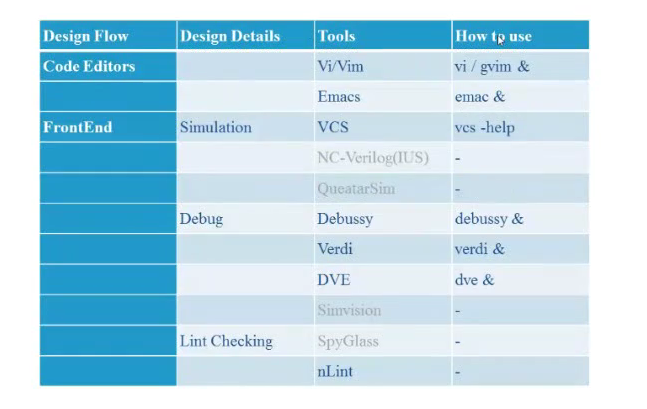

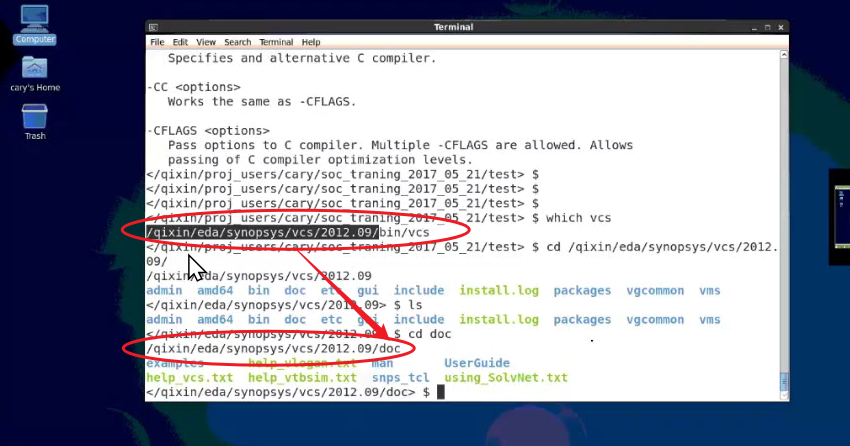

EDA Tools

常用工具

- LVS/DRC - 物理验证,对于版图走线\空间等进行验证

- RC extract - 布局布线之后,将电路图和config进行关联,然后在版图中,选择calibre工具,抽取RC,抽取RC之后会生成calibre文件,将原来的schematic替代为calibre显示,进行DRC和LVS,然后进行后仿

工具使用

- formal check经常的是写脚本