25-IP核简介

1.IP

- IP(Intellectual Property)即知识产权,在半导体产业中讲IP核定义为用于“ASIC或FPGA中的预先设计好的电路功能模块”。简言之,这里的IP即电路功能模块。

- 在数字电路中,将常用的且比较复杂的功能模块设计成参数可修改的模块(FIFO、RAM、SDRAMC),可以让其他用户可以直接调用这些模块,这就是IP核。

2.为什么要使用IP核?

- 随着FPGA的规模越来越大,它的设计也是越来越复杂。随着设计规模增大,复杂度提高,使用IP核可以提高开发效率,减少设计核调试时间,加速开发进程,降低开发成本,是业界的发展趋势。

- 据说IC的复杂率每年提高55%,设计能力每年提高20%,设计周期会越来越长,为了缩短设计周期,可以使用IP核

3.IP核的存在形式

分类依据:产品交付方式

- HDL语言形式(软核,软IP) -- 硬件描述语言的形式进行提供,可以进行参数调整,复用性强,布局布线灵活,设计周期短,设计投入少

- 网表形式(固核) -- 完成了综合的功能块,可以预布特定信号或者分配特定的布线资源

- 版图形式(硬核)-- 硬核是完成提供设计的最终阶段产品--掩膜(Mask),缺乏灵活性,可移植性差,更易于实现IP核的保护

4.IP核的缺点

- IP核往往不能跨平台使用

- IP核不透明,看不到内部的核心代码

- 定制IP需要额外收费

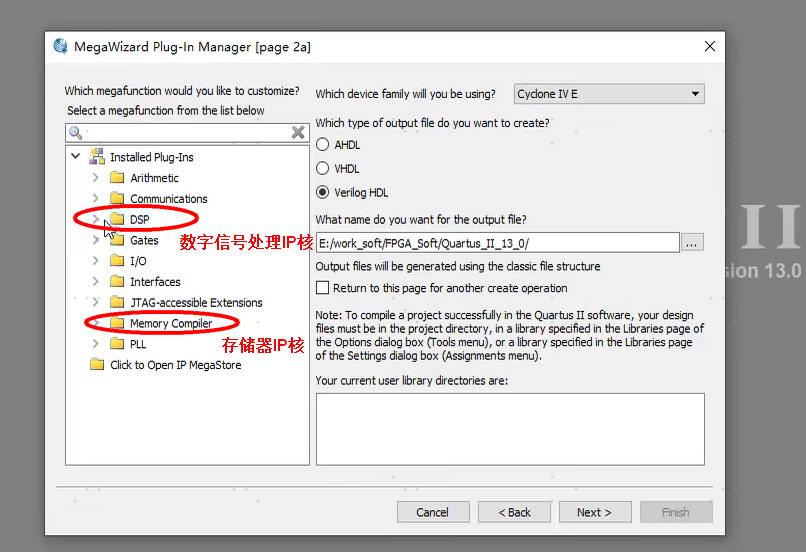

5. Quartus II 软件下IP核的调用

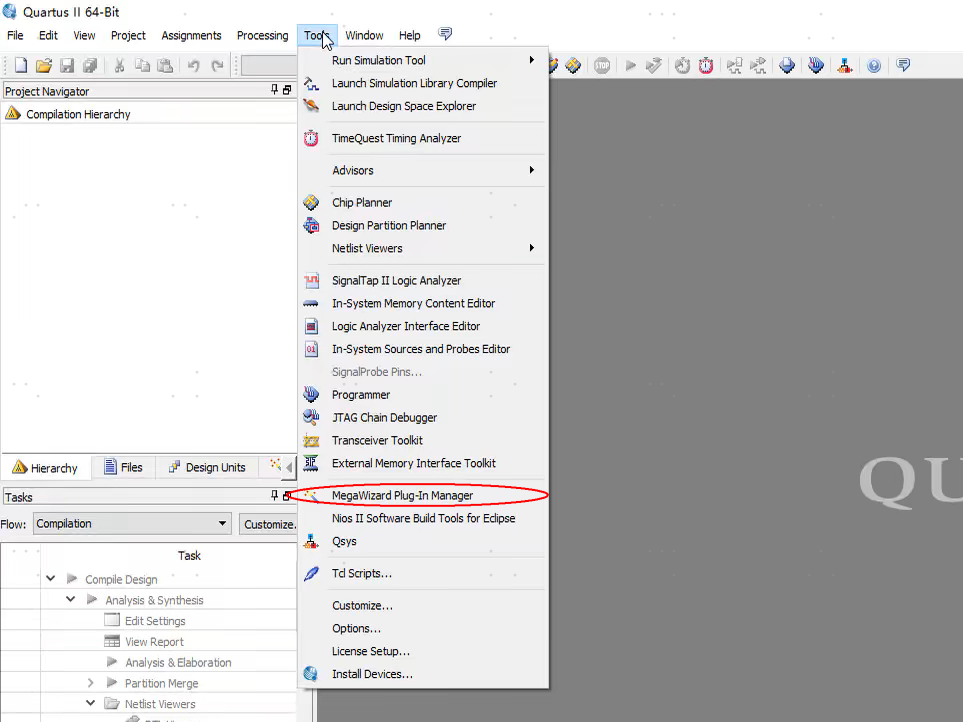

- Mega Wizard插件管理器(最常用)

- SOPC构造器

- DSP构造器

- Qsys设计系统例化

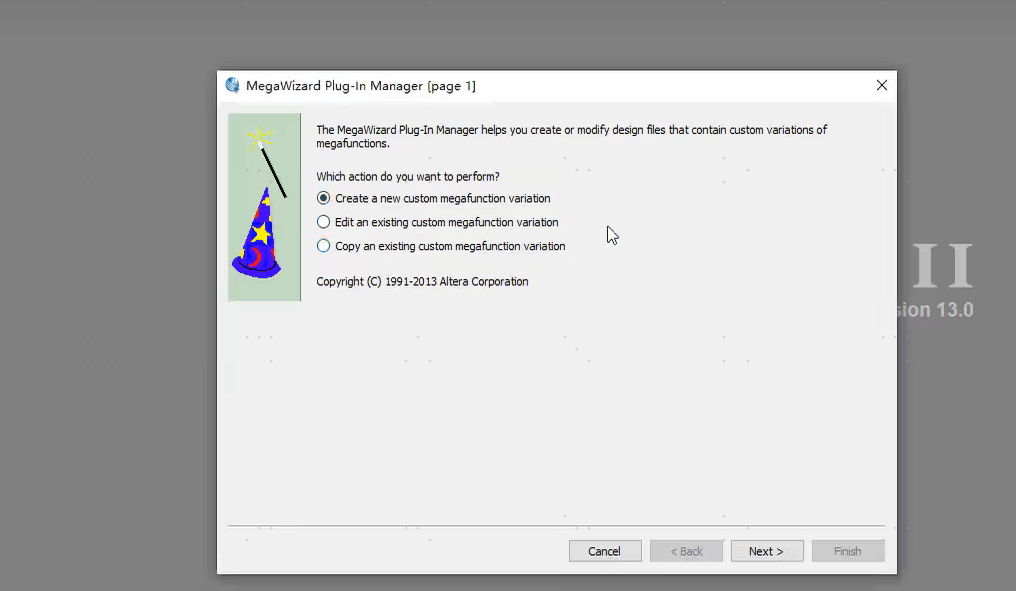

Mega Wizard插件管理器可以用于创建和修改设计文件

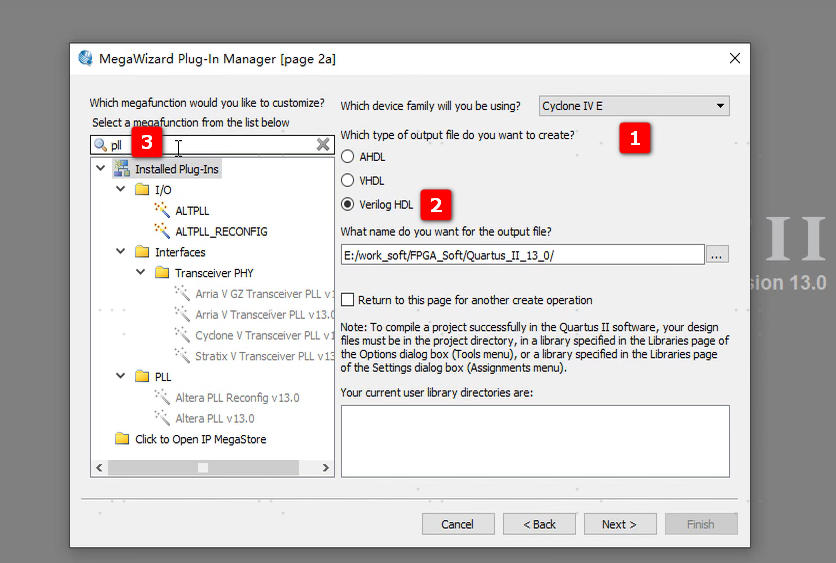

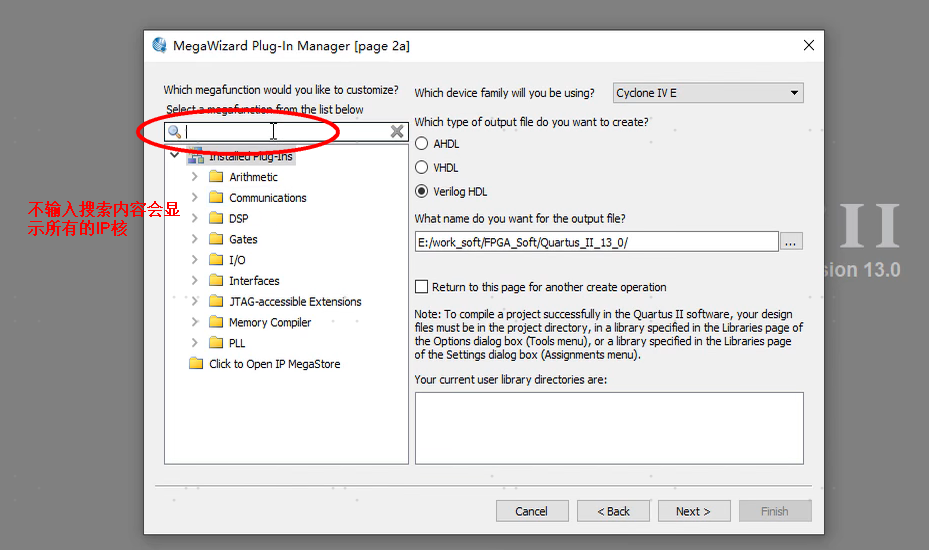

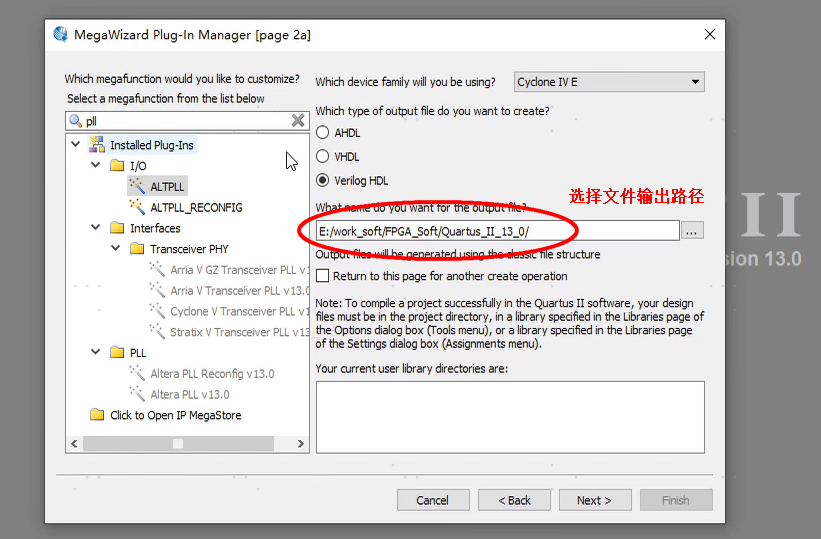

6.Mega Wizard插件管理器使用

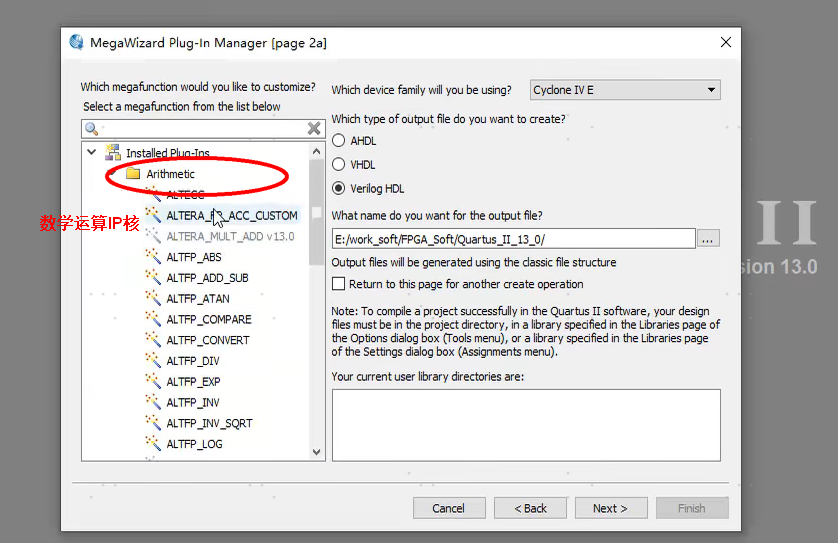

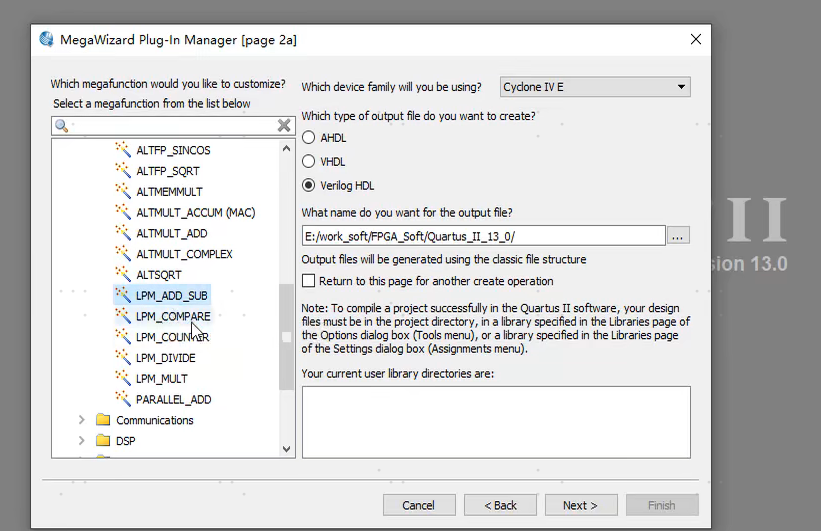

7.Altera IP核的分类

- LPM -- 参数化IP核库

- ALT -- 表示Altera特定的IP核

- 浮点数运算IP核

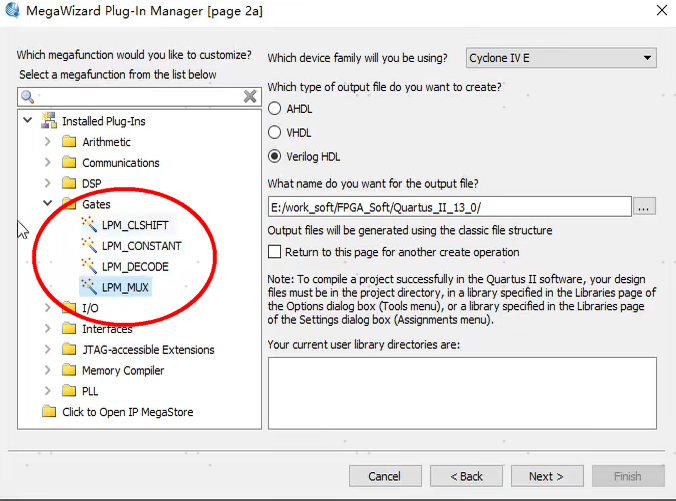

- 逻辑运算IP核

逻辑运算IP核位置再Gates文件夹下

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 张高兴的大模型开发实战:(一)使用 Selenium 进行网页爬虫

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构