1.SD Timing

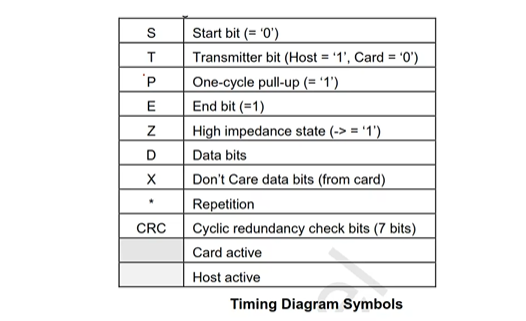

- 时序主要体现在CMD和Response的时序

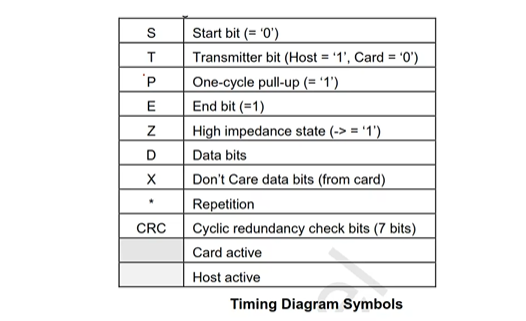

- S - 起始位,一直为0

- T - Transmitter,1表示CMD(发起端是Host),0表示Response(发起端是Card)

- P - pull up(上拉),当总线上所有的SD Host和SD Card都输出高阻态的时候,可以认为是总线没有驱动总线,此时可以给总线挂接一个上拉电阻或者下拉电阻,可以给总线一个固定的电压值,上拉为高电平(1),下拉为低电平(0)

- E - 结束位,一直为1

- Z - 高阻态,表示从总线断开,不驱动总线(作为Slave),SD Host发送命令的时候,SD Host作为Master,SD Card作为Slave,SD Card一定是输出z的

- D - Data

- X - 不需要关心的bit

- CRC - (循环冗余校验)用于数据传输的校验

- 灰色区域表示Card和Host有效

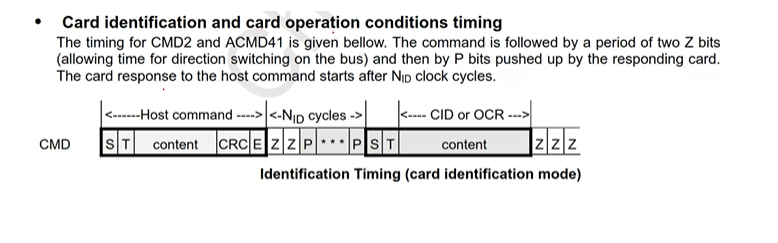

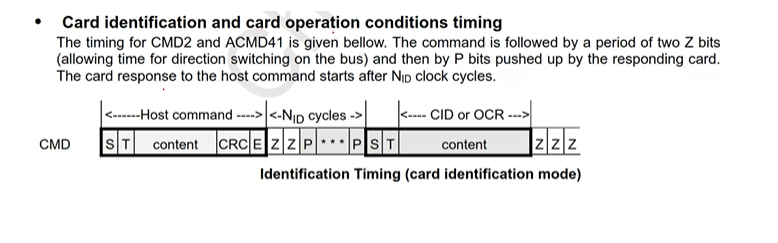

1.1 Card Identification

- P(=1)的个数取决于从Host Command到CID or OCR的时间NID

- 中间的两个Z:用于SD Host驱动总线和SD Card驱动总线的切换,总线控制权切换需要一定的时间

- 电容的充放电需要一定的时间,总线可以等效为一些电容

- 当SD Host发送完最后CMD的一个bit,发送一个Z,此时SD Host和SD Card都不驱动总线,经过两个Z之后,切换总线的控制权,经过一段上拉P,然后SD Card就可以返回数据了

- P是SD Card进行驱动的

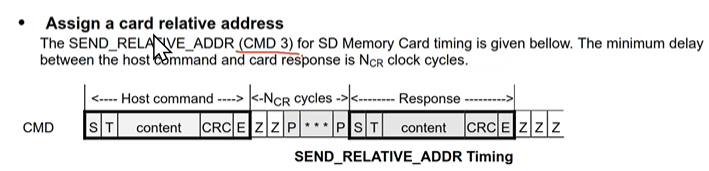

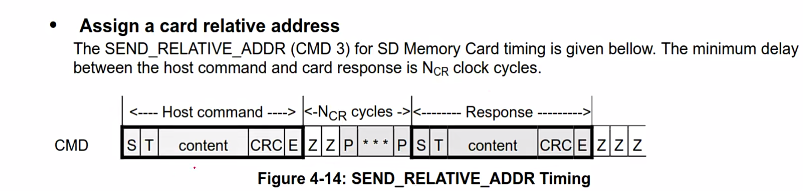

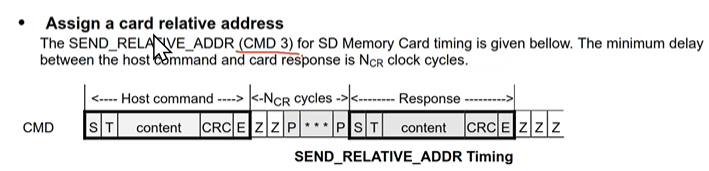

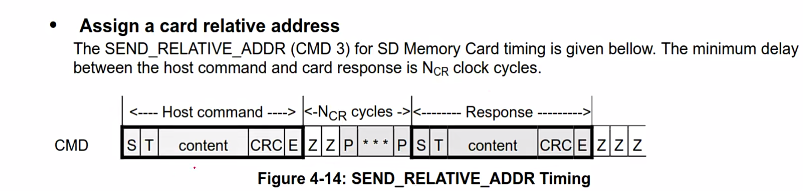

1.2 Assign a Card relative address

- CMD3 - SD Card会发布一个RCA,SD Card会转到data transfer state

- RCA值会附带在content中,SD Host收到content之后,保存RCA值,然后发送其他指令

- 不同指令之间的时间可以是不一样的

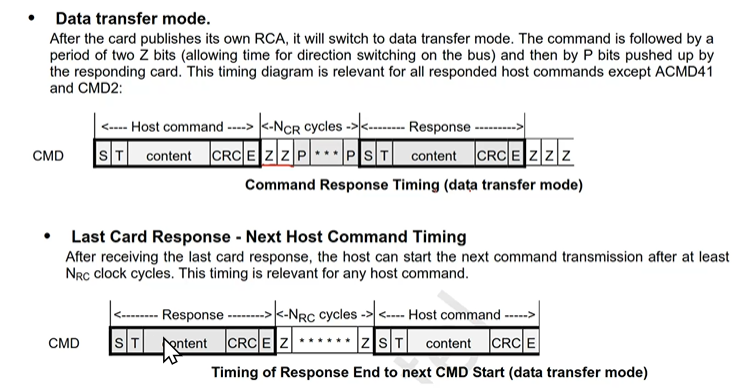

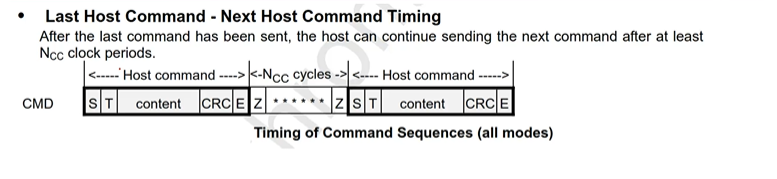

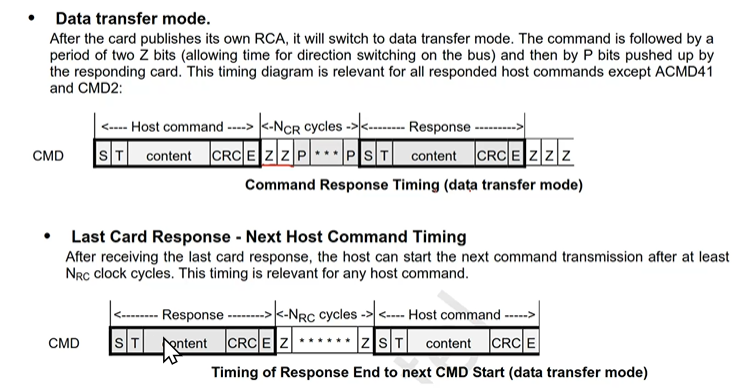

1.3 Data Transfer mode

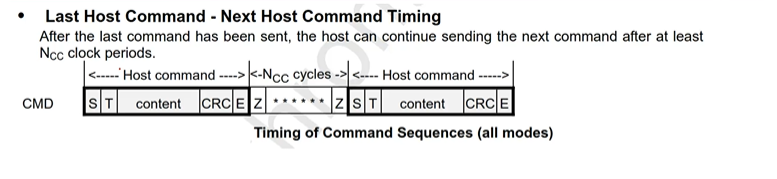

- 发送完一条指令之后,接收完response之后,需要经过一个NRC之后才能进行发送下一条CMD

- 前一条CMD没有reponse,后面也可以跟一条CMD,中间要间隔Ncc

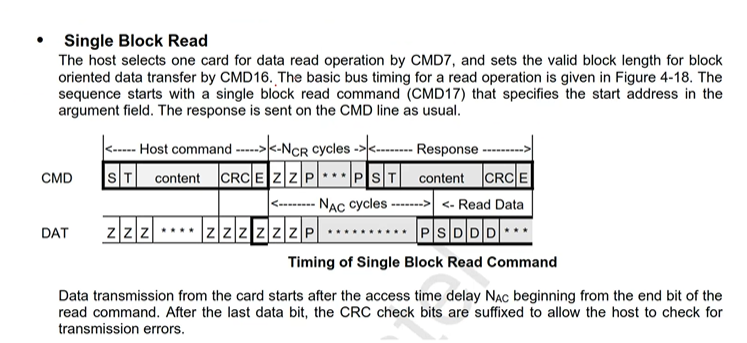

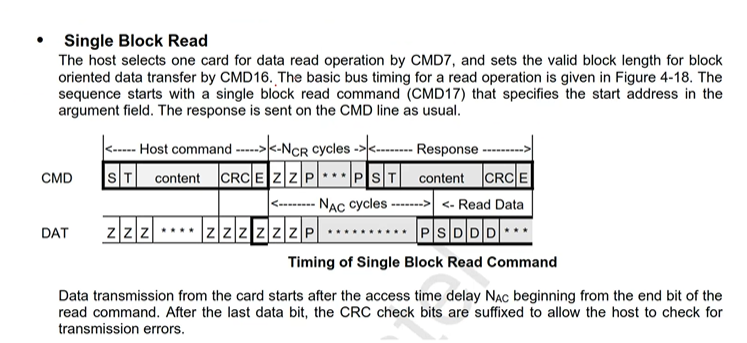

1.4 single block read

- 需要在CMD和Data总线上一起走

- CMD16 - 设置block length

- CMD17 - 经过一个NCR之后返回一个response

- Data可以和response并行返回,需要经过一个NAC时间access time(访问时间),可以返回第一笔数据(start bit)是0;所有的器件的输出都是z的话,总线会被上拉为1,P就是1,如果start bit是1的话,就无法区分这个1是前面的z还是P还是开始的数据1,所以start bit为0,当Data总线检测到start bit为0的时候,就表示SD Card返回response,在start bit下一个周期就可以采用返回的数据

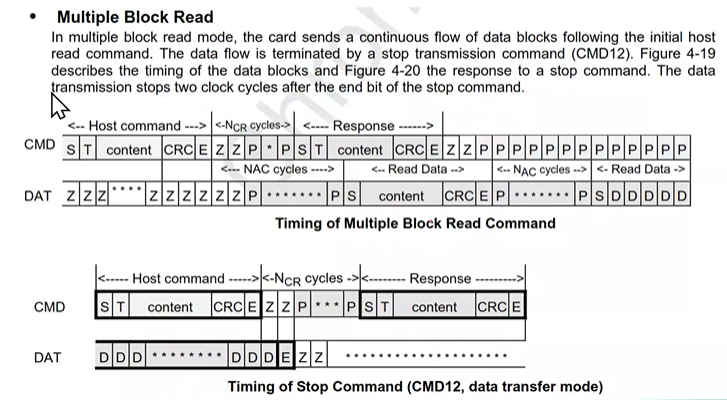

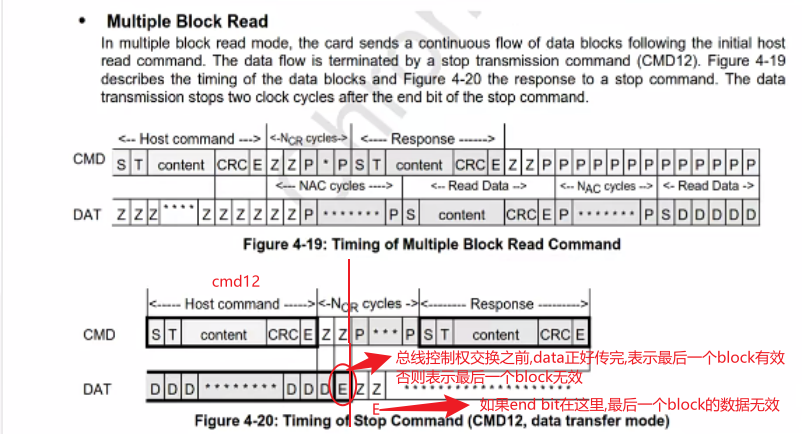

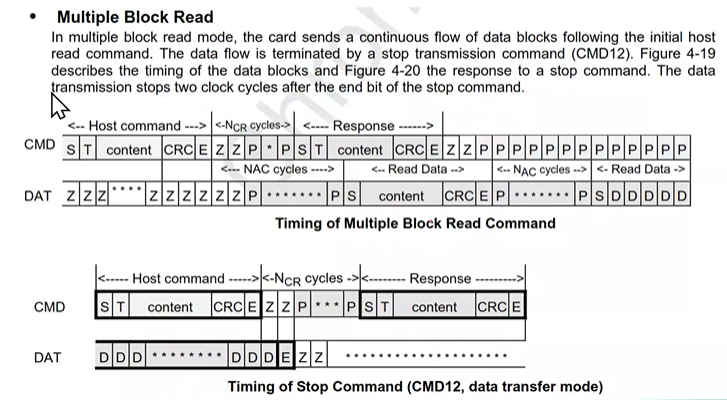

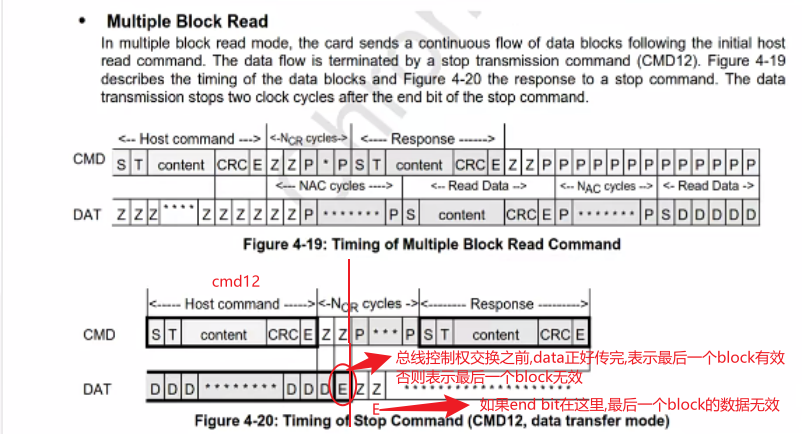

1.5 multiple block read

- single block read - block为512byte,数据多的时候,通过single block read读取效率不高,使用multiple block read

- CMD18 - 发送multiple block read请求

- 接收CMD到接收第一笔数据需要经过NAC的时间,返回start bit,然后返回数据,在返回第一个block数据之后,需要有一段时间的上拉(时间间隔),然后再进行下一个block的数据传输

- 在两次block传输之间的上拉时间NAC,在这段时间内,总线的控制权还在SD Card

- 读数据结束? -- 发送CMD12,告诉SD Card可以停止传输

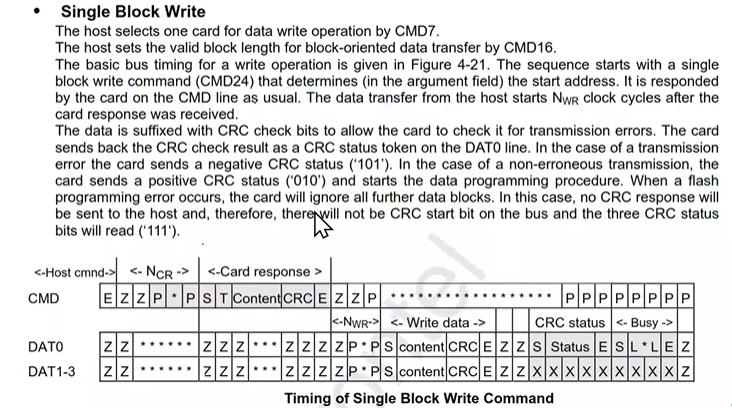

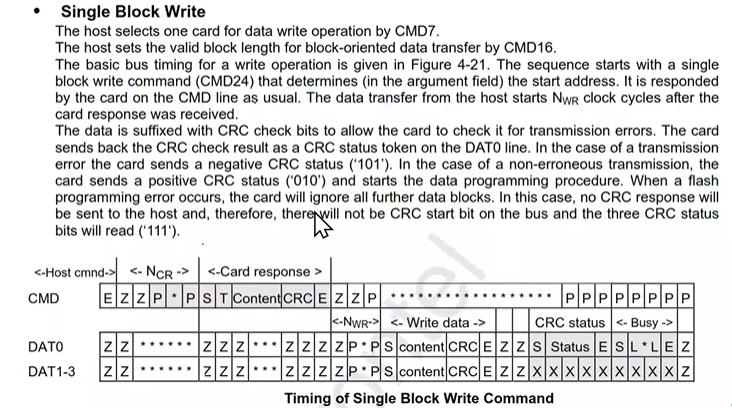

1.6 single block write

- SD Host先发起命令,然后经过NCR时间,接收到卡的response

- 然后经过NWR时间,这段时间是SD Host控制总线,然后可以发送写数据

- 为什么需要SD Card返回response?需要进行判断这个卡是不是能够正常接收命令,如果SD Host发送的命令存在错误或者CRC存在问题,response就是不正当的response,后面就没有必要发送数据了

- 发送完写数据和CRC,SD Card接收完数据之后,会返回CRC的状态,如果数据传输错误返回101,数据传输正确返回010,SD Host接收到错误信息,会重新发送一个请求

- Busy状态 - 写的步骤分为两步,有一个receiving data state,先将数据接受到buffer中,然后进入programming state,将buffer中的数据写入存储颗粒,如果当前buffer满了或者在programming state,会将Busy拉低(将总线Data0拉低),表示当前Card正在忙,不能接收下一笔读写操作,当SD Card写完之后,会将busy状态解除,SD Card发一个end bit,值为1

- Busy解除 - 一连串的0之后有一个1,busy解除之后才能进行下一条命令

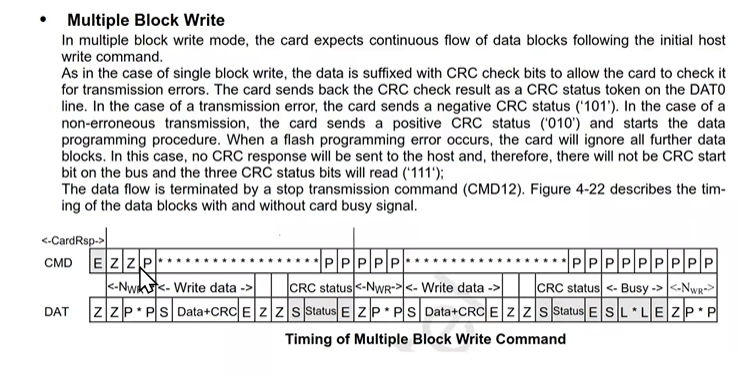

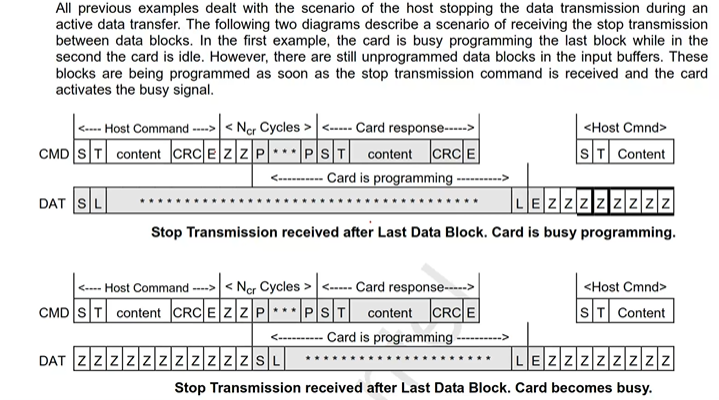

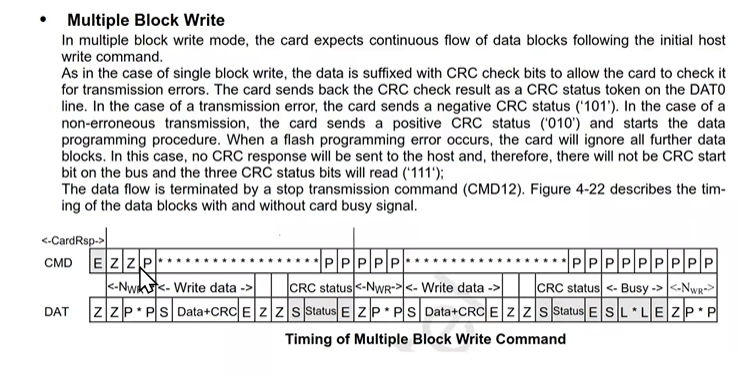

1.7 multiple block write

- 写操作与之前single block write时序一致

- 通过CMD12终止

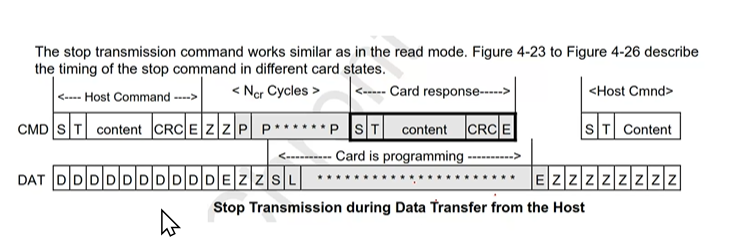

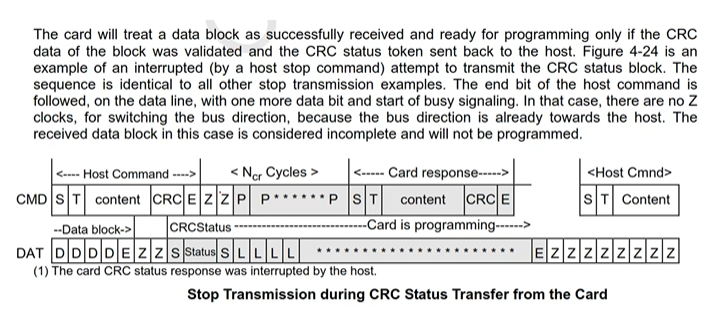

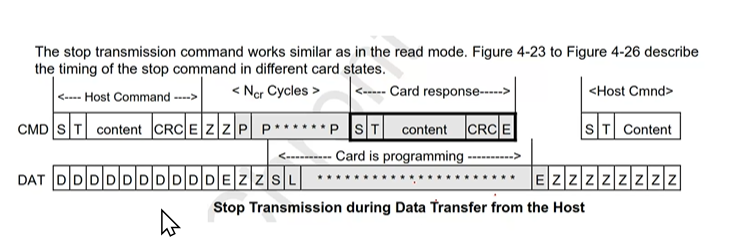

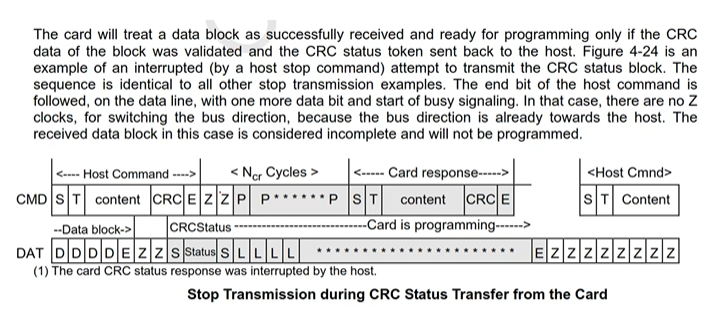

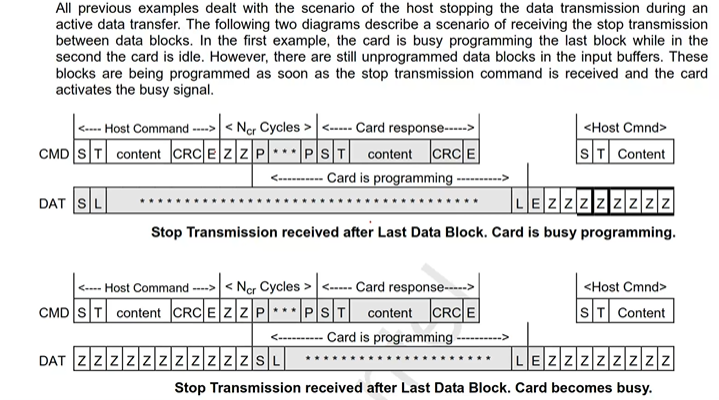

1.8 stop command

- 当前正在写数据,CRC之后,会将Data0拉为0,表示当前卡是busy状态,此时可以发送CMD12

- 在发送CMD12的时候可能存在不同的状态,比如CMD12的end bit正好处于CRC的接收端,如果当前卡正在进行programming,来了一个CMD12,并不会终止当前programming过程

- 如果当前CMD12的end bit处于Data传输过程中,会终止数据存储到SD Card的buffer中

- 在进行SD Card驱动设计的时候,数据发送完成之后才能发送CMD12

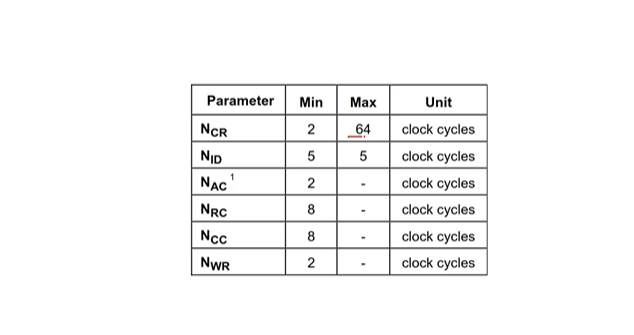

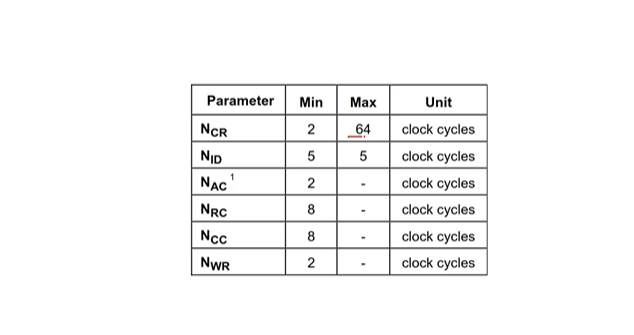

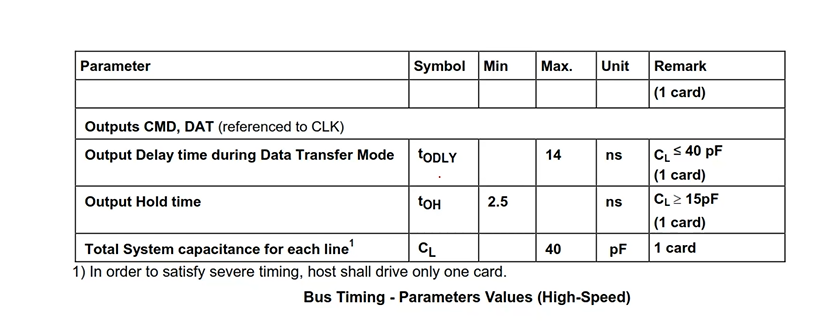

1.9 时序参数

- 在进行设计SD Host的时候,有最大周期数和最小周期数,使用计数器进行计数,如果超过64个cycle没有response,就可以发起下一个CMD

- NAC - access time,读访问时间,没有设置最大周期,但是最好还是设置一个时间,不能无限的进行等待,否则效率不高

- NRC - response 和 command之间

- NCC - command 和 command之间

- NWR - 在SD Host接收到response之后可以发送写数据

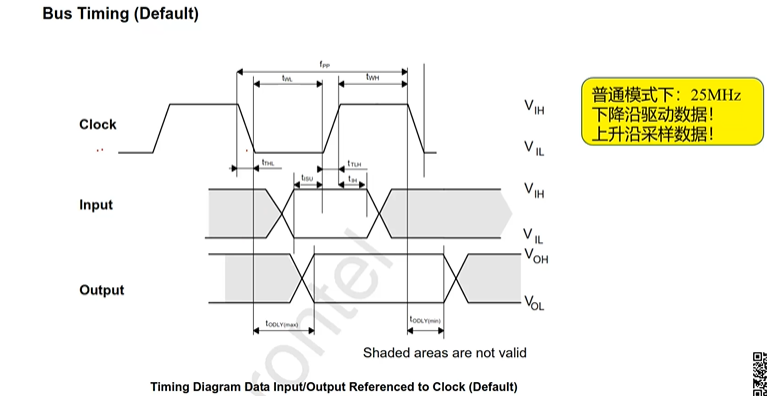

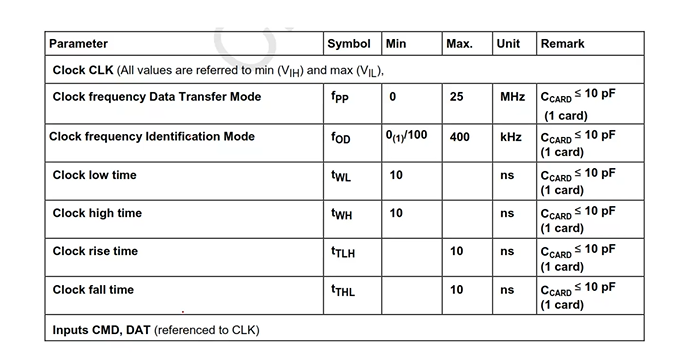

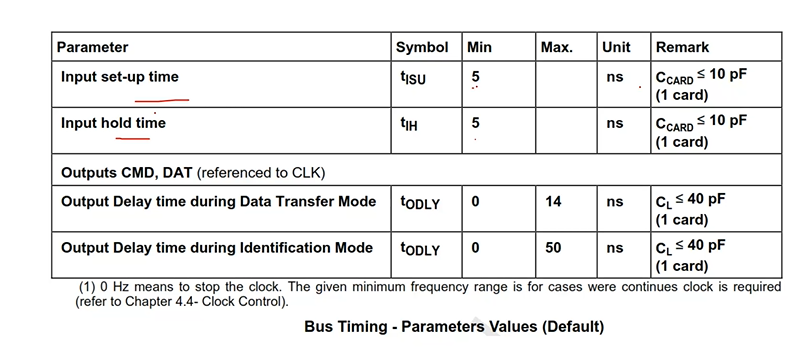

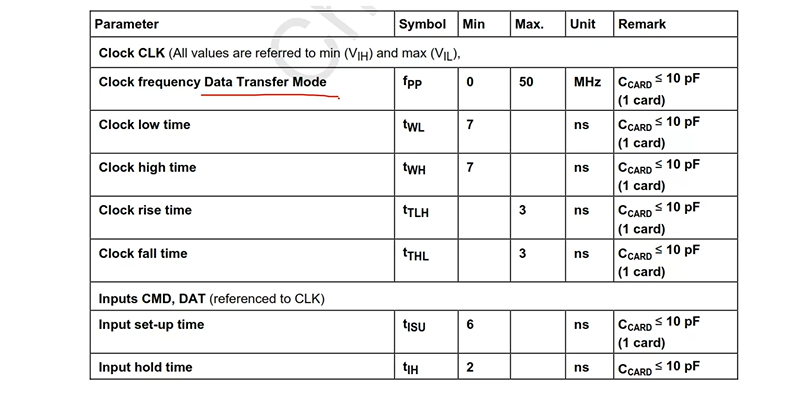

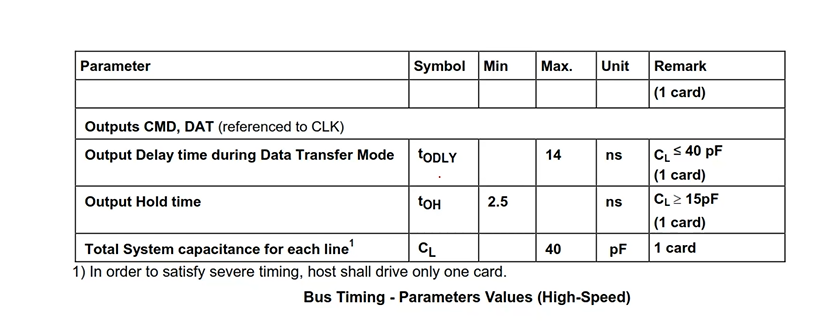

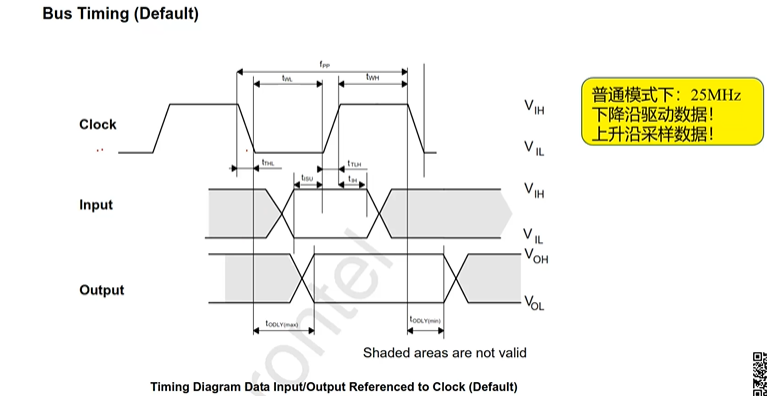

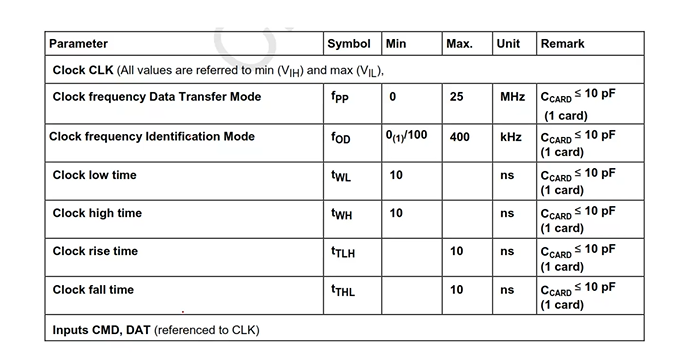

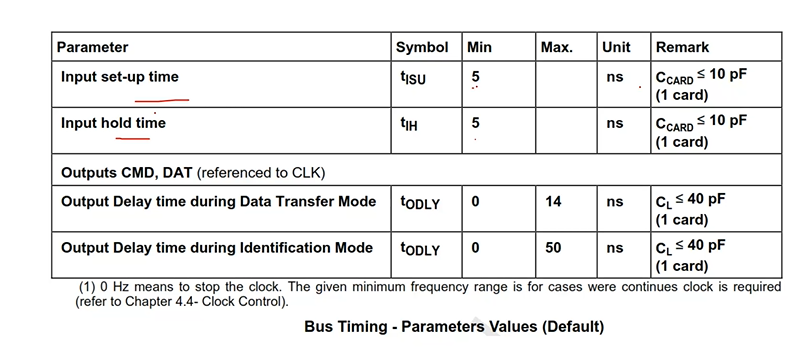

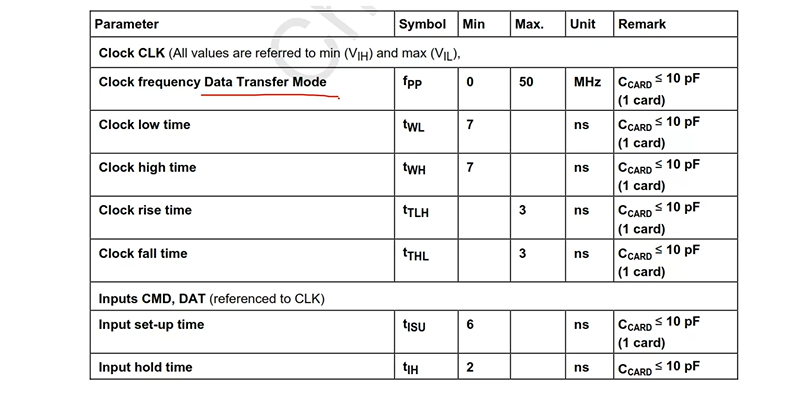

1.10 普通模式

- SD时序有两种模式,一种是普通模式,另外一种是高速模式

- 普通模式的时钟频率在0-25MHz,时钟频率比较低

- 需要在时钟的下降沿驱动数据,SD Card或者SD Host要发送一笔数据或者CMD,需要在时钟的下降沿驱动数据,数据真正在总线上被看到需要一定的时间,原因是设备从0变为1或者从1变为0需要一定的时间(电容的充电或者放电),这个时间与总线的负载和驱动能力有关

- thl - 时钟从高到低的时间

- tlh - 时钟从低到高的时间,时钟的变化不能太缓慢,保证时钟的质量

- twl - 低电平时间

- twh - 高电平时间

- fpp - 时钟周期

- toDLY(max) - 在采样之前数据需要保持稳定,如果数据延时时间过长,在采样的时候数据不稳定,会导致出错

- toDLY(min) - Hold时间,时间不能过小

- 时钟频率最小值是0,最大值是25MHz

- 卡识别模式下,不需要传输数据,只需要传输数据和响应,数据量比较小,频率较低

- 数据传输模式下,传输数据量比较大,频率比较高

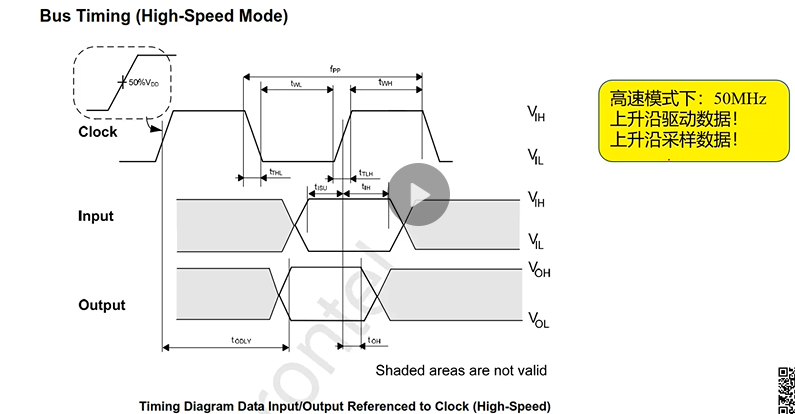

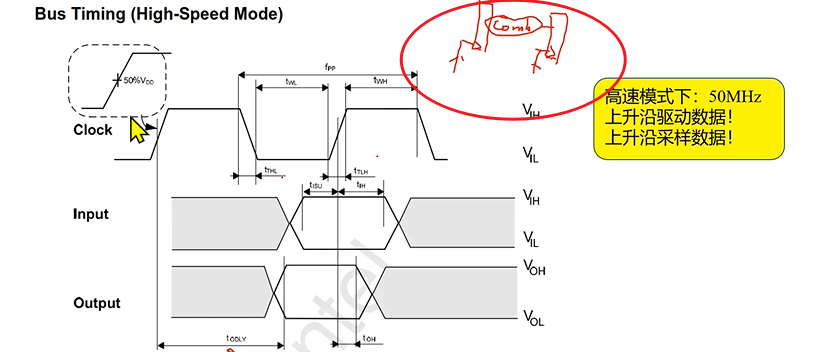

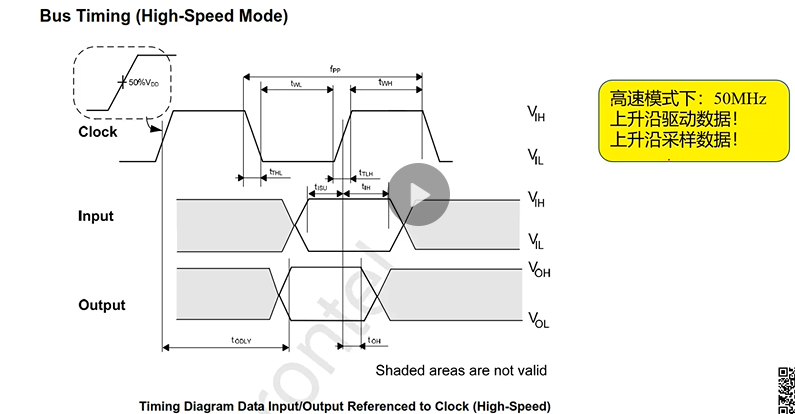

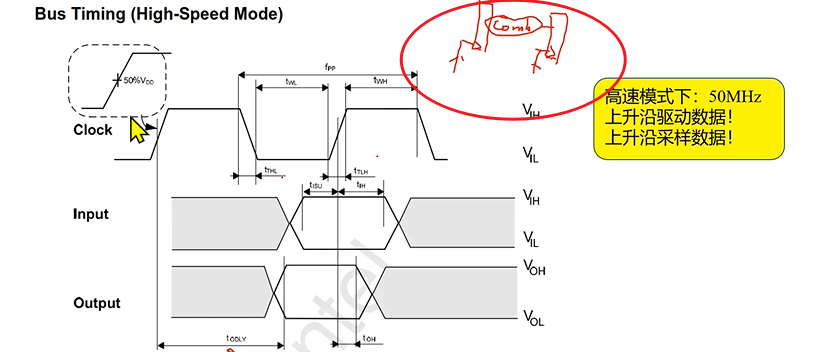

1.11 高速模式

- 上升沿驱动数据,上升沿采样数据

- toDLY - 类似与两个寄存器之间组合逻辑的延时,延时时间过大,在上升沿进行采样的时候,可能会采样到不稳定的值

- toH - 采样完成之后需要稳定的时间

- high speed mode只会对应于data transfer mode下,最大时钟频率是50MHz

- 单卡的负载电容40PF

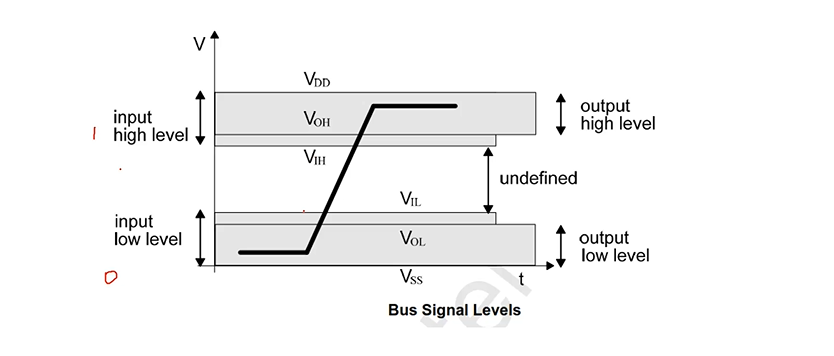

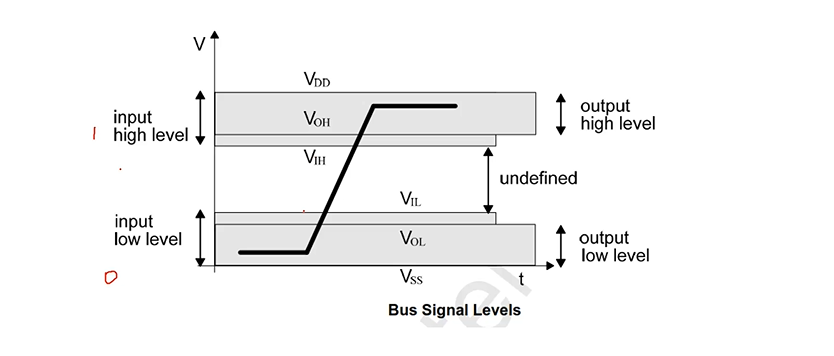

1.12 SD Bus Signal Level

- VoL - Vss -- 输出为0

- VoH - VDD - 输出为1

- Vss - VIL - 输入为0

- VIH - VDD - 输入为1

- "1"和"0"会有一定的容限

posted @

2023-06-05 22:40

Icer_Newer

阅读(

1234)

评论()

编辑

收藏

举报