05-译码器

1.译码器

- 译码器是编码的逆过程,在编码时,每一种二进制代码都赋予了特定的含义,即都代表了一个确定的信号或者是对象;把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器,或者说,译码器可以将输入二机制代码的状态翻译成输出信号,以表示其原来含义的电路

- 译码器(decoder)是一类多输入多输出组合逻辑电路器件,其可以分为变量译码和显示译码两类

- n-2^n译码器 - n个输入,可以表示2^n方种状态

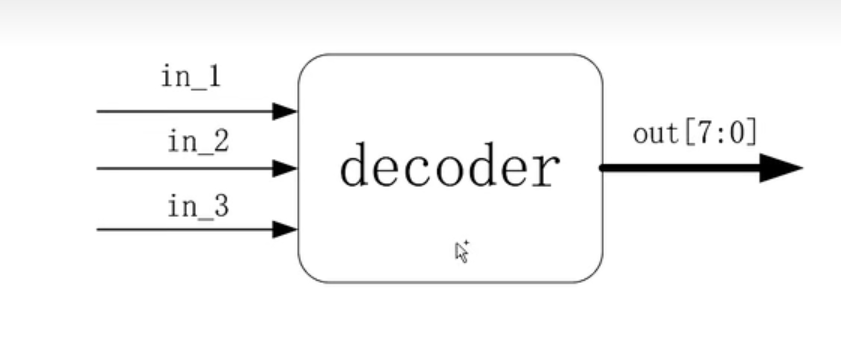

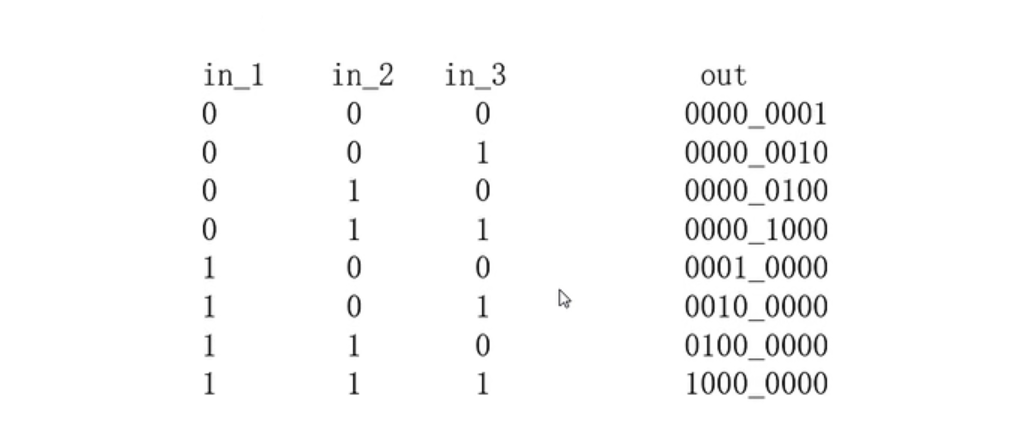

2.实现3-8译码器

- 3-8译码器有3路输入,8路输出

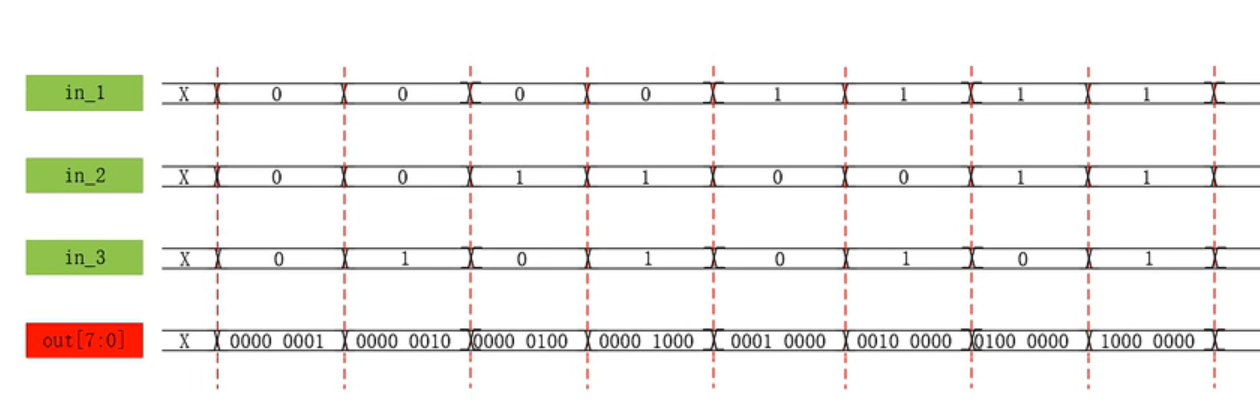

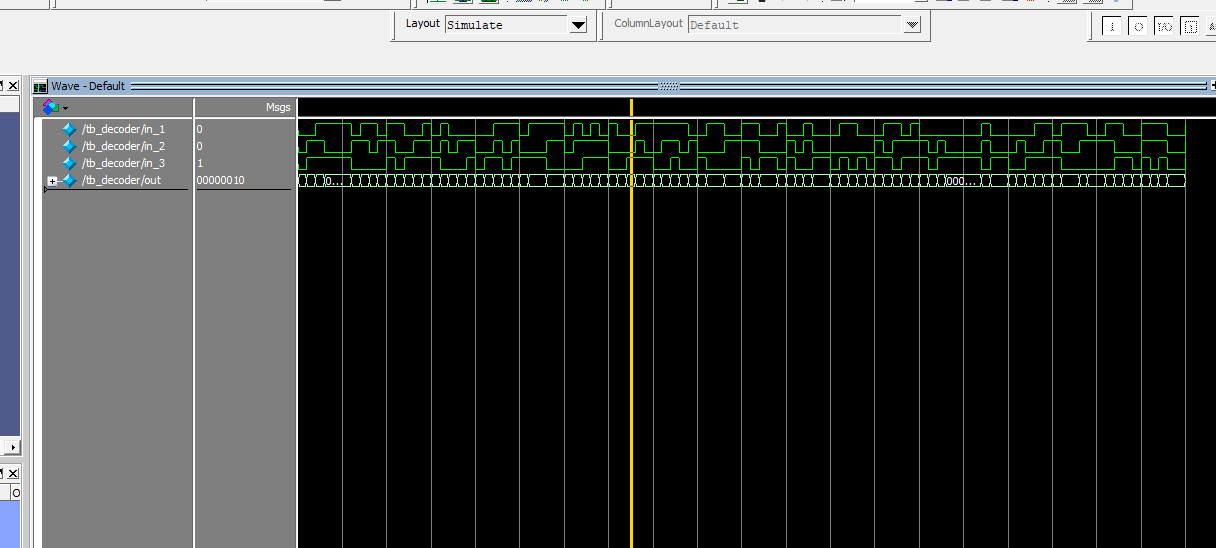

2.1 框图和波形图

- 三个1bit输入,输出8位独热码

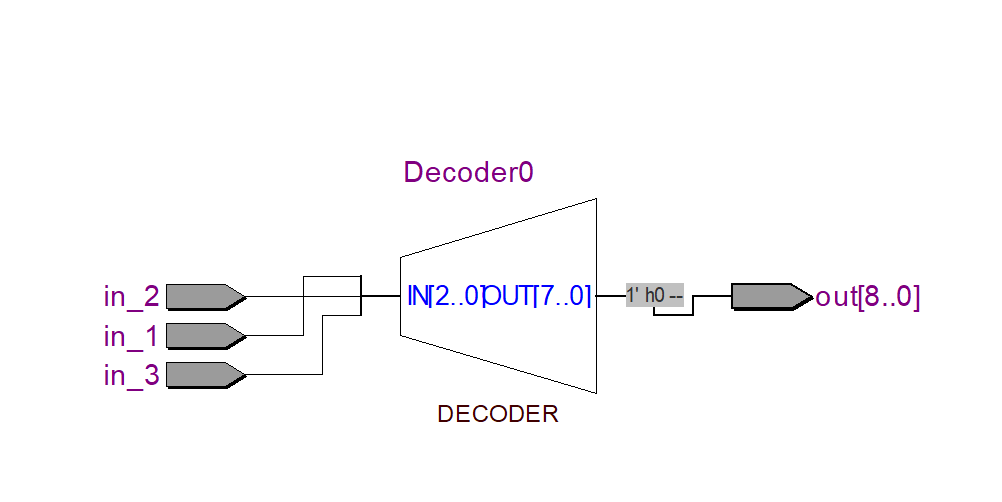

2.2 RTL

module decoder

(

input wire in_1,

input wire in_2,

input wire in_3,

output reg [8:0] out

);

// 使用case语句

// 使用if-else语句

always@(*)

begin

case({in_1,in_2,in_3})

3'b000 : out = 8'b0000_0001;

3'b001 : out = 8'b0000_0010;

3'b010 : out = 8'b0000_0100;

3'b011 : out = 8'b0000_1000;

3'b100 : out = 8'b0001_0000;

3'b101 : out = 8'b0010_0000;

3'b110 : out = 8'b0100_0000;

3'b111 : out = 8'b1000_0000;

default : out = 8'b0000_0001;

endcase

end

endmodule

- case语句和if-else语句都可以实现译码器,但是if-else语句实现有优先级,就是先后判断的顺序,而使用case语句实现则没有优先级的问题

- 进行代码编译

2.3 Testbench

`timescale 1ns/1ns

module tb_decoder();

reg in_1;

reg in_2;

reg in_3;

wire [7:0] out;

initial begin

in_1 <= 1'b0;

in_2 <= 1'b0;

in_3 <= 1'b0;

end

initial begin

$timeformat(-9,0,"ns",6);

$monitor("@time:%t:in_1=%b,in_2=%b,in_3=%b,out=%b",$time,in_1,in_2,in_3,out);

end

always #10 in_1 <= {$random} % 2;

always #10 in_2 <= {$random} % 2;

always #10 in_3 <= {$random} % 2;

decoder decoder_inst(

.in_1 (in_1),

.in_2 (in_2),

.in_3 (in_3),

.out (out)

);

endmodule

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 【自荐】一款简洁、开源的在线白板工具 Drawnix

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· C#/.NET/.NET Core优秀项目和框架2025年2月简报

· DeepSeek在M芯片Mac上本地化部署