1.多路选择器

- 组合逻辑是Verilog设计中的一个重要组成部分,从电路本质上讲,组合逻辑电路的特点是输出信号只是当前时刻输入信号的函数,与其他时刻的输入状态无关,无存储电路,也没有反馈电路

组合逻辑电路输出信号的电平变化仅仅与输入信号的电平变化有关,不涉及信号跳变沿的处理

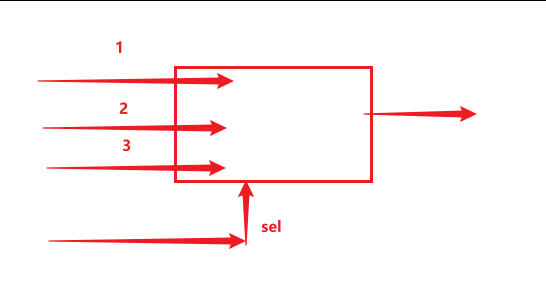

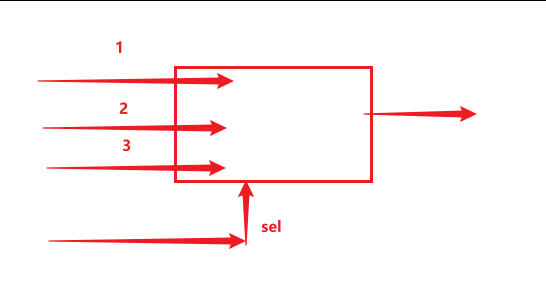

- 多路选择器,是数据选择器的别称,在多路数据传送过程中,能够根据需要将其中任意一路选择出来的电路,叫做数据选择器,也称作是多路选择器或者多路开关

2.二选一选择器

- 输入两信号,在选择信号为高的时候输出第一个信号,选择信号为低的时候输出第二个信号

- 在开发板上使用KEY1,KEY2作为两个信号输入,KEY3作为信号的选择,LED灯为输出

3.FPGA设计

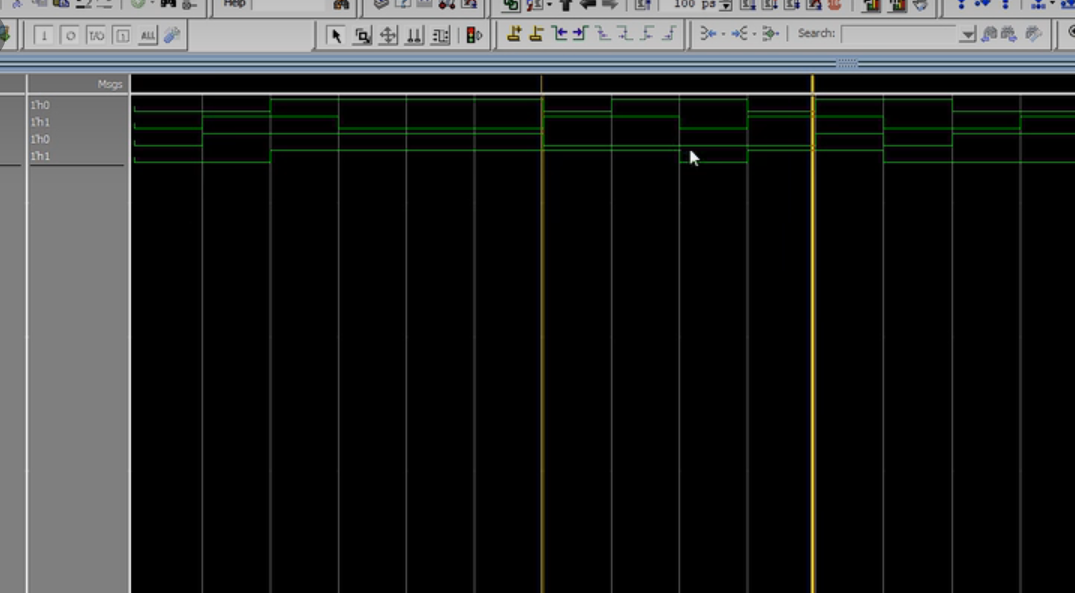

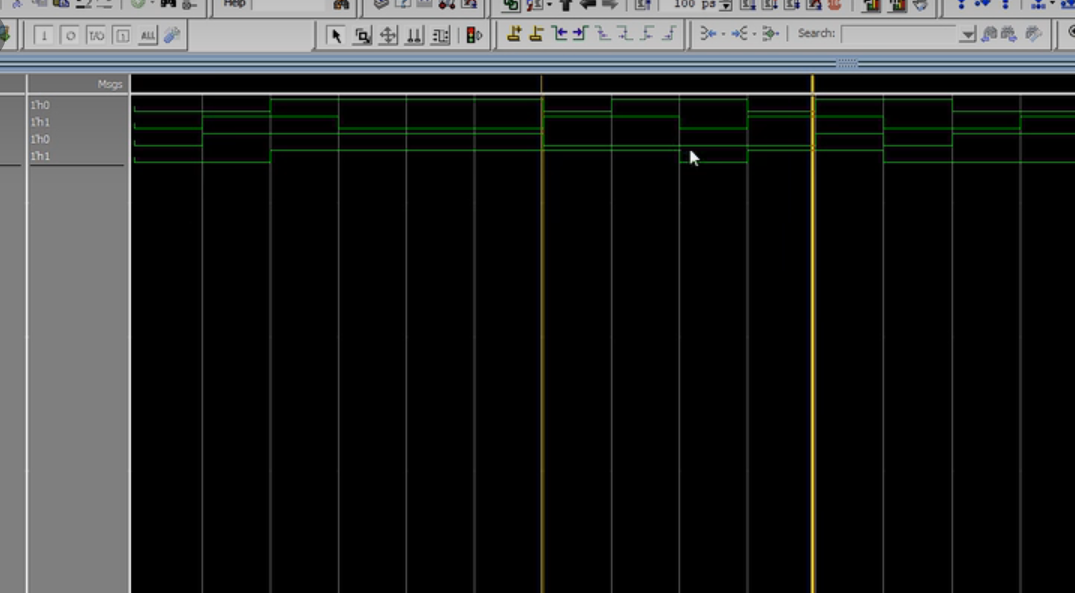

框图与波形图

- in_1和in_2信号是随机的

RTL

module mux2_1

(

input wire [0:0] in_1,

input wire in_2,

input wire sel,

output reg out

);

// always产生组合逻辑的时候使用*

always@(*)

if(sel == 1'b1)

out <= in_1;

else

out <= in_2;

endmodule

- 创建quartus项目,添加verilog代码,编译文件

testbench编写

`timescale 1ns/1ns

module tb_mux2_1();

reg in_1;

reg in_2;

reg sel;

wire out;

initial begin

in_1 <= 1'b0;

in_2 <= 1'b0;

sel <= 1'b0;

end

always #10 in_1 <= {$random} % 2;

always #10 in_2 <= {$random} % 2;

always #10 sel <= {$random} % 2;

initial begin

$timeformat(-9,0,"ns",6); //-9表示以ns的时间显示时间 10^-9表示ns,10^-3表示ms

// 0表示小数点后打印的位数

// 最小显示位数6个

$monitor("@time %t:in_1=%b in2=%b out=%b",$time,in_1,in_2,out);

// %t 是时间的占位符 $time使用%t占位

end

// 例化module

mux2_1 mux2_1_inst(

.in_1 (in_1),

.in_2 (in_2),

.sel (sel ),

.out (out )

);

endmodule

- 在quartus中添加仿真文件

- 设置仿真格式

- 在modelsim中进行仿真

// 其他方式实现

// 方式2

always@(*)

case(sel)

1'b1:out = in_1;

1'b0:out = in_2;

default : out = in1;

endcase

// 方式3

assign out = sel ? in_1 : in_2;