01-module/分频器/激励写法

1.module

- module有出入接口,输出接口

- module有时钟和复位

// input

clock;

rest_n; // n表示低电平复位

//output

o_data;

module module_a(

// module是关键字表示声明一个模块

// module module名

// module .. endmodule是一对

// module module_name(模块的输入输出列表);

// 输入只能是wire变量,只有线才能连入module

// 输出可以是wire类型也可以是reg类型,一般是reg变量

// 不写位宽,默认是1bit位宽的

input wire clk,

input wire rest_n,

output reg [7:0] o_data // 8bit数据

);

endmodule

module Lut_m(

input wire sclk,

input wire rst_n,

input wire [9:0] i_data,

input wire [15:0] i_sin,

output reg [15:0] o_cos,

output reg o_div_clk,

output reg [9:0] div_clk,

// module中包含子module

// 嵌套子模块,就是例化,首先要先将子模块写成单独的模块

// 例化:先写模块的名字 例化的名字

sub_m u_sub_m (

// 如何引入接口

//用点的方式先写模块的接口(接入的接口)

.sclk (sclk),

.rst_n (rst_n),

.i_data (i_data),

.i_sin (i_sin),

.o_cos (o_cos),

.o_data (o_data)

);

sub_n u_sub_n(

.sclk (sclk),

.rst_n (rst_n),

.i_data (i_data),

.i_sin (i_sin),

.o_data (o_data)

);

);

endmodule

2.分频器

// 输入50MHz,二分频

module div_clk(

input wire sclk,

input wire rst_n,

output reg div_clk_o

);

// 分频器,需要一个计数器,二分频,需要记录01状态,1bit

// div_cnt就是一个计数器

// 计数器为0的时候,输出为低,计数器为1的时候,输出为高

reg div_cnt;

//寄存器使用always语句进行赋值的

// 这是一种异步复位的写法

// 在时钟上升沿的时候触发逻辑

// 复位使用作用下实现复位逻辑

// 计数器逻辑

always@(posedge sclk or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

div_cnt <= 1'b0;

end

else begin

div_cnt <= div_cnt + 1'b0;

end

end

// 产生div_sclk_o

always@(posedge sclk or negedge rst_n) begin

if(rst == 1'b0) begin

div_cnt <= 1'b0;

end

else if(div_cnt == 0) begin

div_clk_o <= 1;

end

else

div_clk_o <= 0;

end

endmodule

- div_cnt = 0的时候,给输出赋值1,下一个时钟上升沿就可以输出1

- div_cnt = 1的时候,给输出赋值0,下一个时钟上升沿就可以输出0

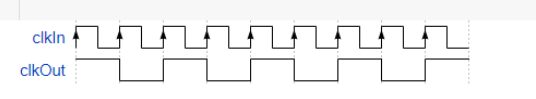

在时序电路里,一般系统时钟都是高频的,不同外设对时钟频率的要求不同,所以需要通过分频来获得相应的时钟频率,一般都是将高频的时钟转换为低频的时钟。最简单的分频就是2分频,也就是把时钟频率减半,输出时钟和输入时钟上升沿对齐,波形图是这样的:

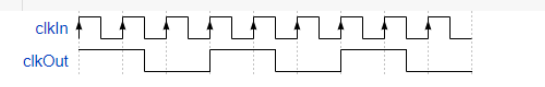

有遇到需要奇数分频的时候,这时候上升沿和下降沿都需要用到,3分频波形图是这样的:

上面两张图都是50%占空比的,有的时候我们只需要用输出时钟的上升沿,不需要考虑下降沿,这样的话我们的输出时钟只需要是单脉冲的就可以了,设计的时候会简单很多,单脉冲的3分频波形图是这样的:

8分频 -- 4周期反转一次

4分频 -- 2周期反转一次

3分频 -- 1.5周期/3周期

5分频 -- 2.5周期/5周期

7分频 -- 3.5周期/7周期

后期会补充分频器和计数器的书写方式

浙公网安备 33010602011771号

浙公网安备 33010602011771号