31-触发器01

触发器

1.时序逻辑电路概述

数字电子技术分为组合逻辑电路和时序逻辑电路

组合逻辑电路:输出仅仅与当时的输入有关,比如与非门,输入两个1输出0

时序逻辑电路:输出不仅仅与当时的输入有关,而且与过去的输入有关需要记忆功能

组合逻辑电路就相当于普通的锁,钥匙对了就可以打开;时序逻辑电路相当于电子密码锁,比如密码有三位(123),假如前两位输入错误,第三位输入正确,锁也是不开的,所以输出与之前的输入有关,并且需要记住之前的状态

时序逻辑电路:包含组合逻辑电路和存储单元

2.锁存器和触发器概述

- 锁存器和触发器都是存储单元

- 锁存器是电平触发的,触发器是边沿触发的

- 触发器是时序电路的最小单位

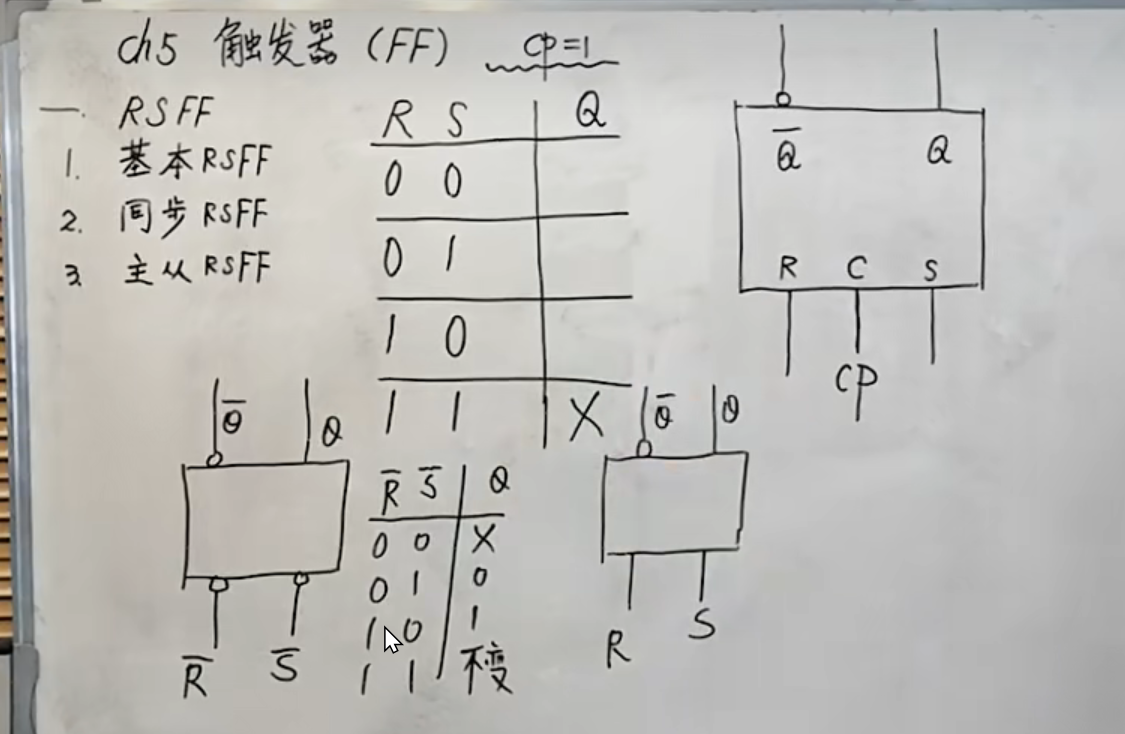

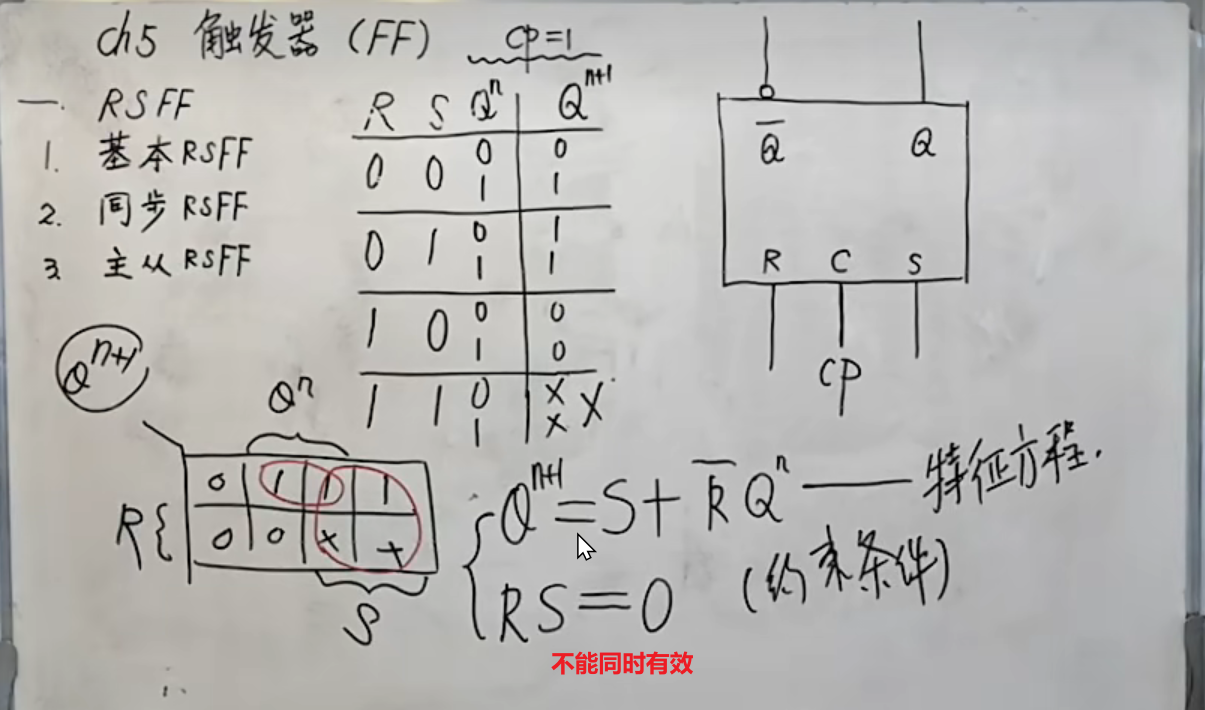

3.RS触发器

- 触发器的名称为Flip-Flop -- FF

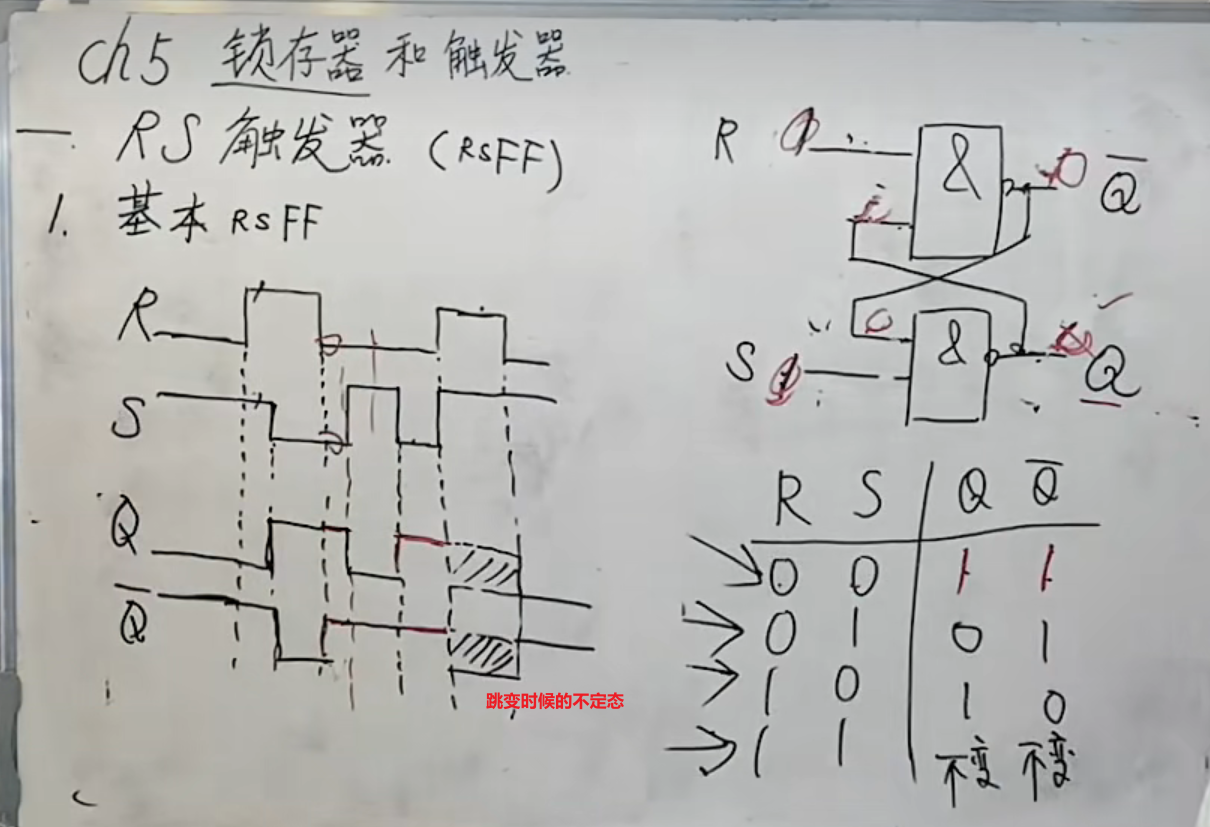

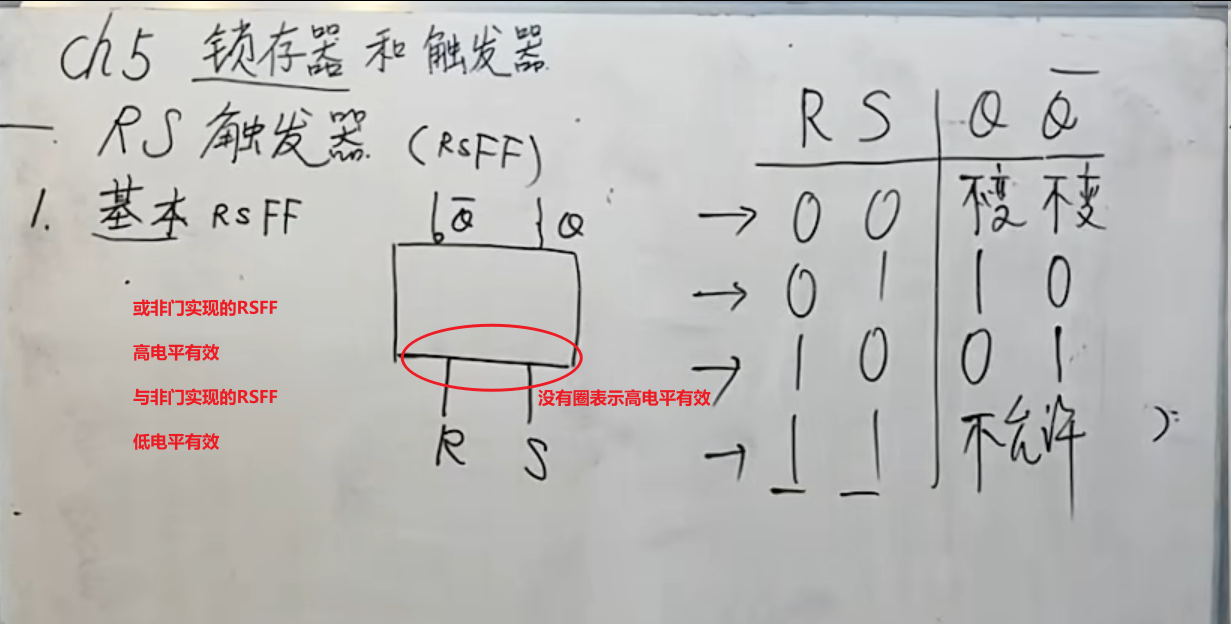

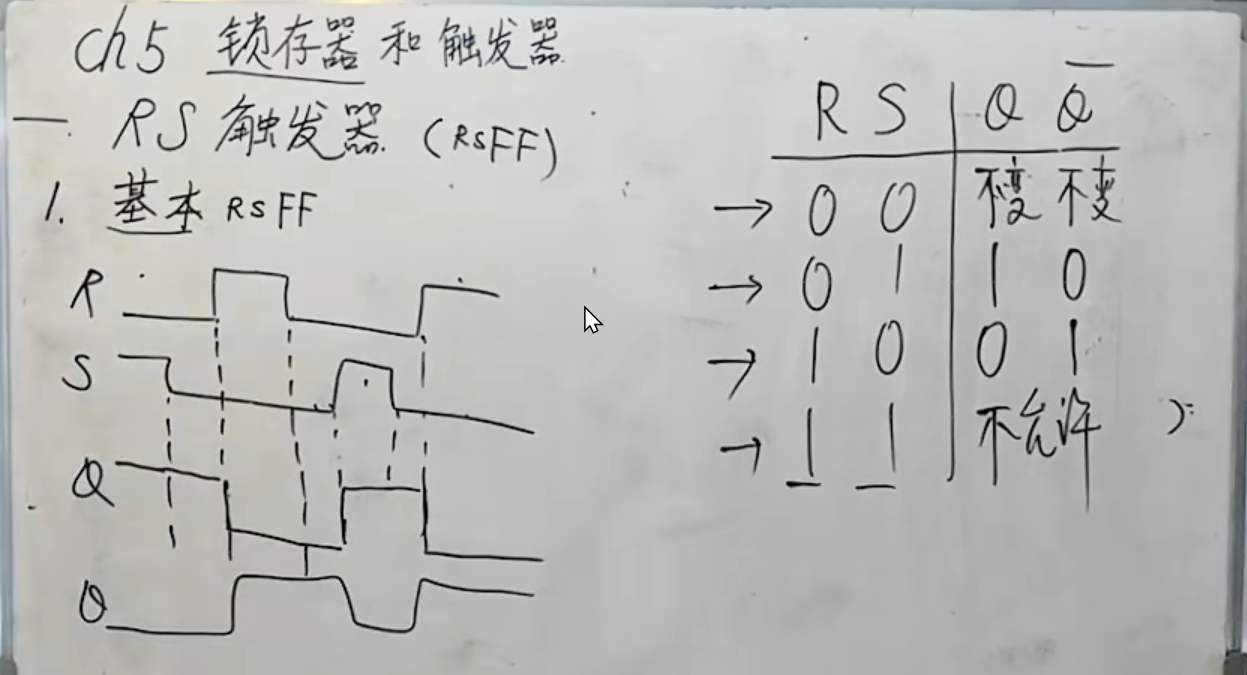

3.1 基本RS触发器

普通的门电路是没有记忆功能的

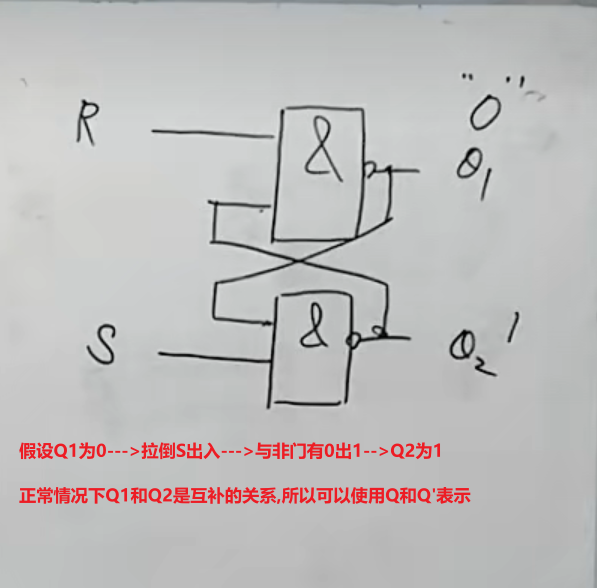

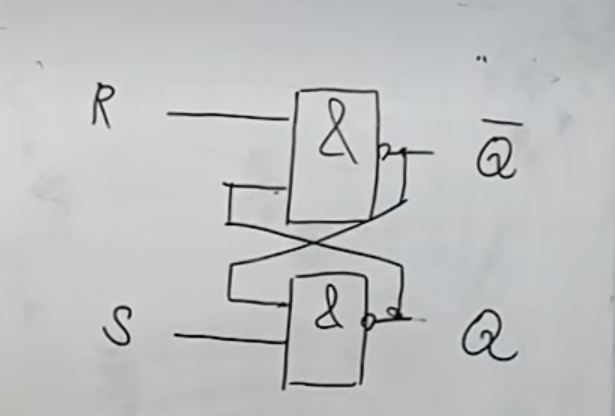

使用两个与非门实现触发器

触发器处于0状态和1状态都是指的Q端

与非门,0输入可以直接决定输出;或非门,1可以直接决定输出

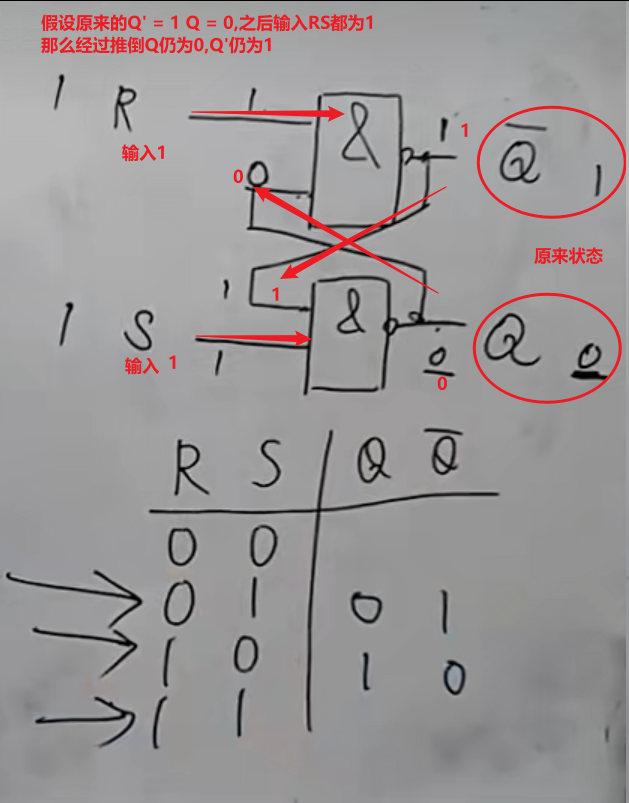

-

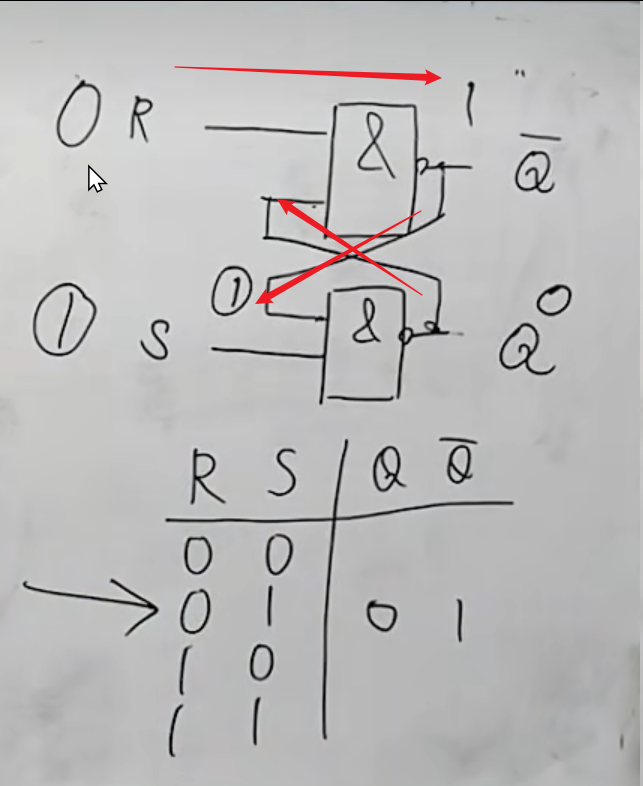

R是0,S是1

-

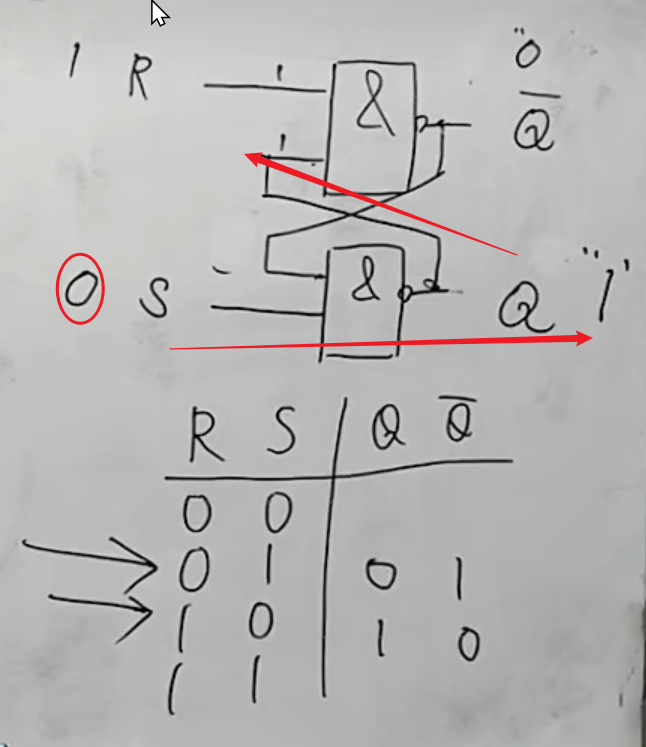

R是1,S是0

-

RS都是1

- R,S端都加入1,输出的状态保持原来的状态不变

- RS都是0

- RS都是0,输出都是1,不符合正常工作的状态

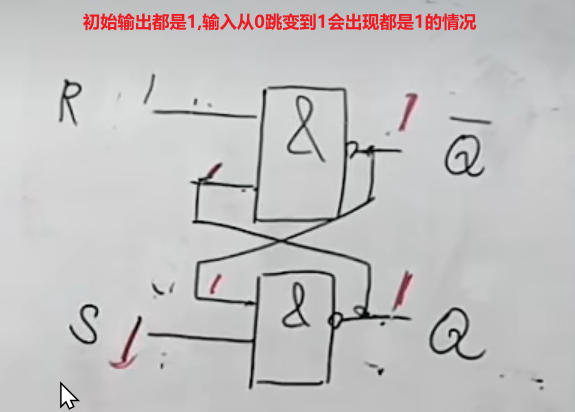

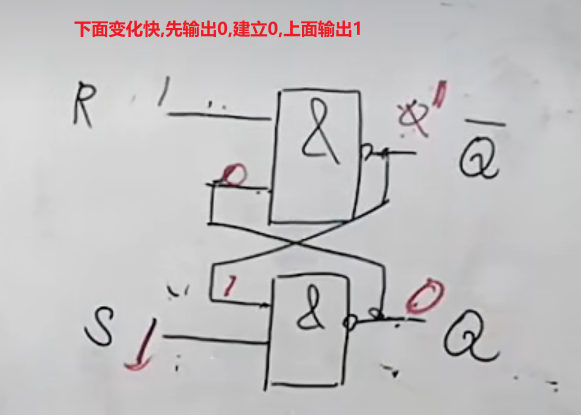

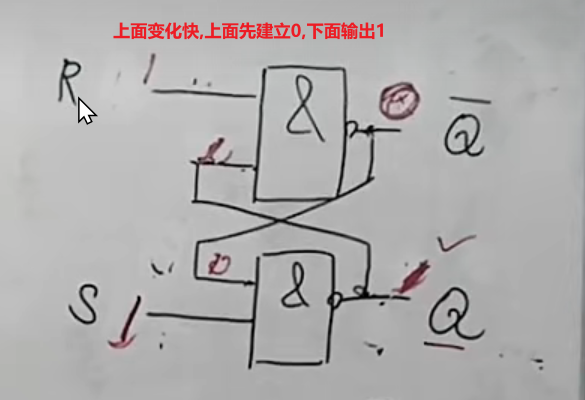

假设RS开始加进去的状态都是0,两个输出都是1,此时将R,S端都进行跳变为1,结果会出现两种情况

此时的输出会有两种情况,看RS所在端的与非门的变化快慢,取决于门的延迟时间

RS在都是0的情况下,输出是确定的,只有在RS端从0跳变到1的时候,会出现不定态

与非门实现,0表示有效,R(Reset)有效,Q输出0,也就是复位;S(Set)端有效,Q输出1,置位端

与非门实现,0有效,或非门实现,1有效

- 在了解有效端之后,进行波形绘制比较方便

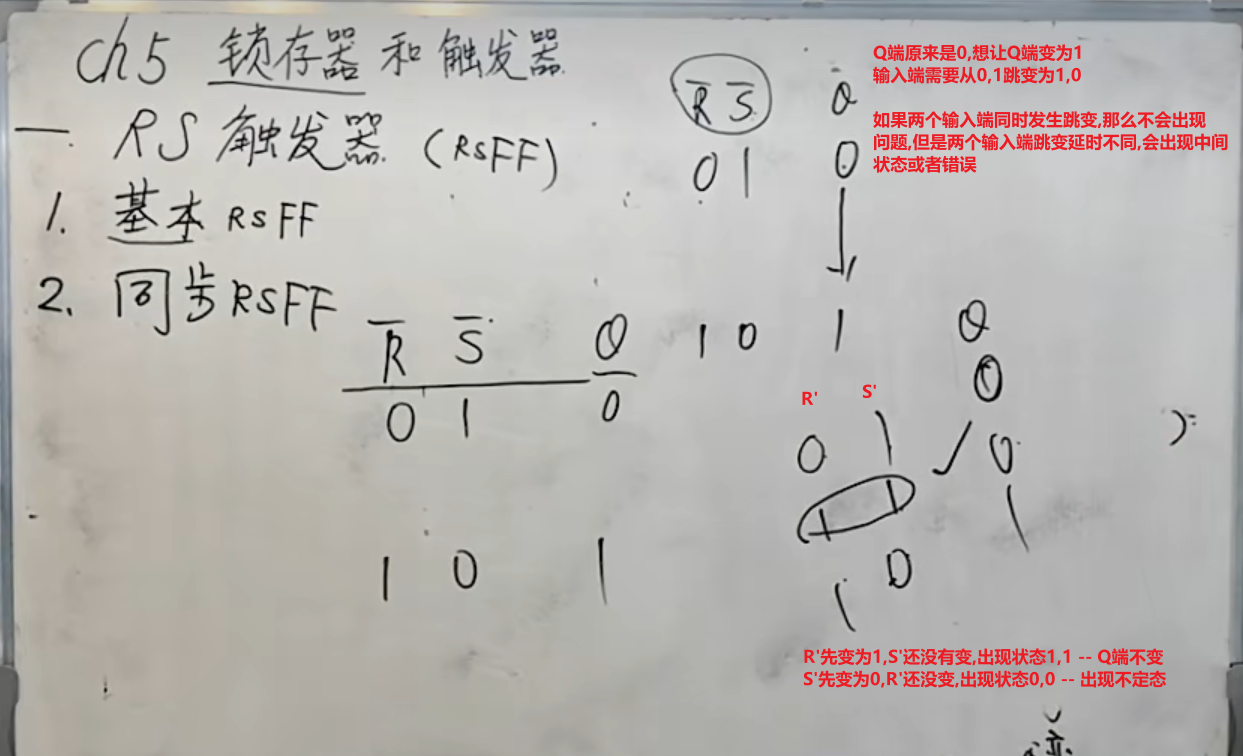

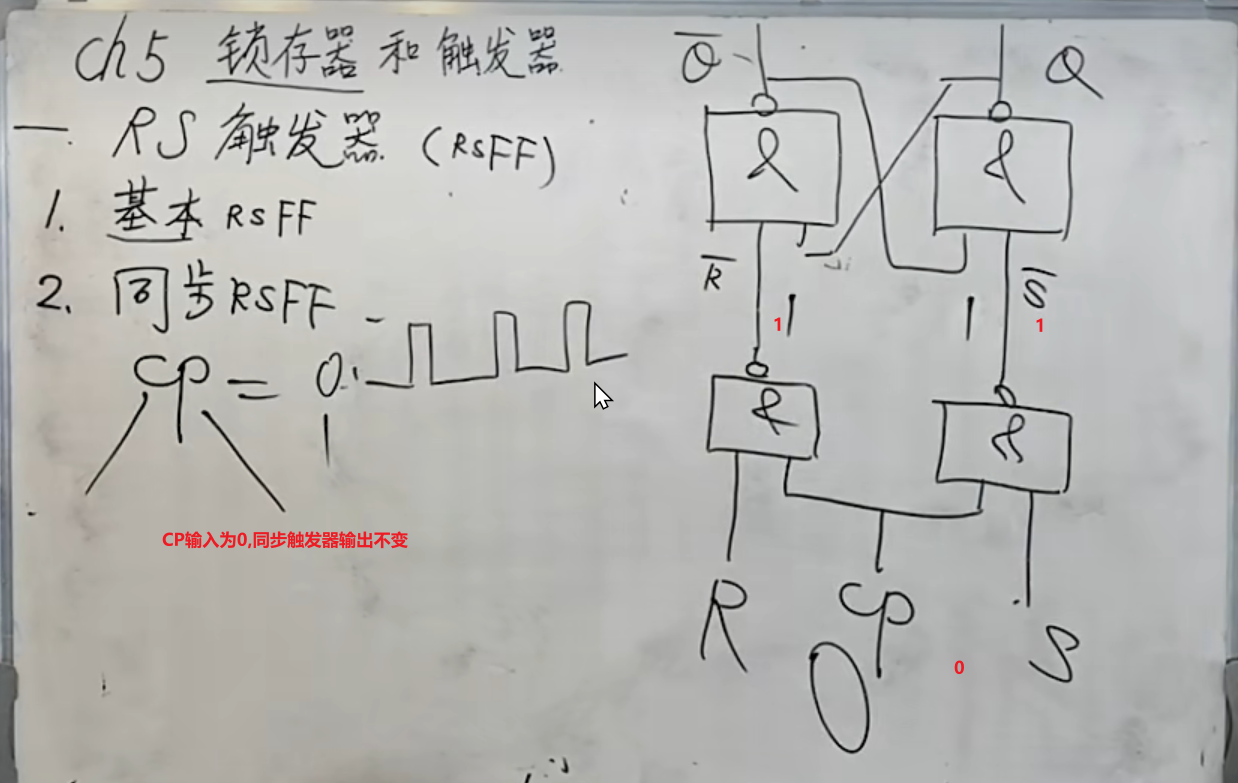

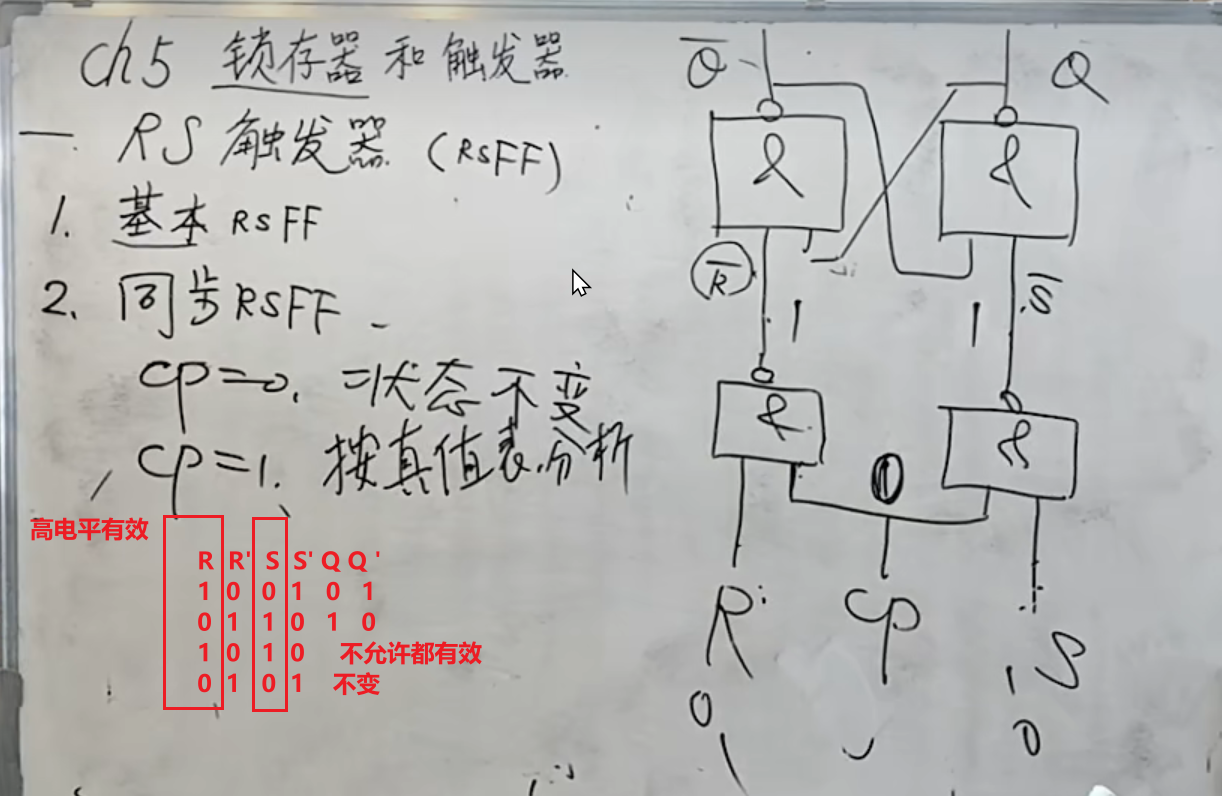

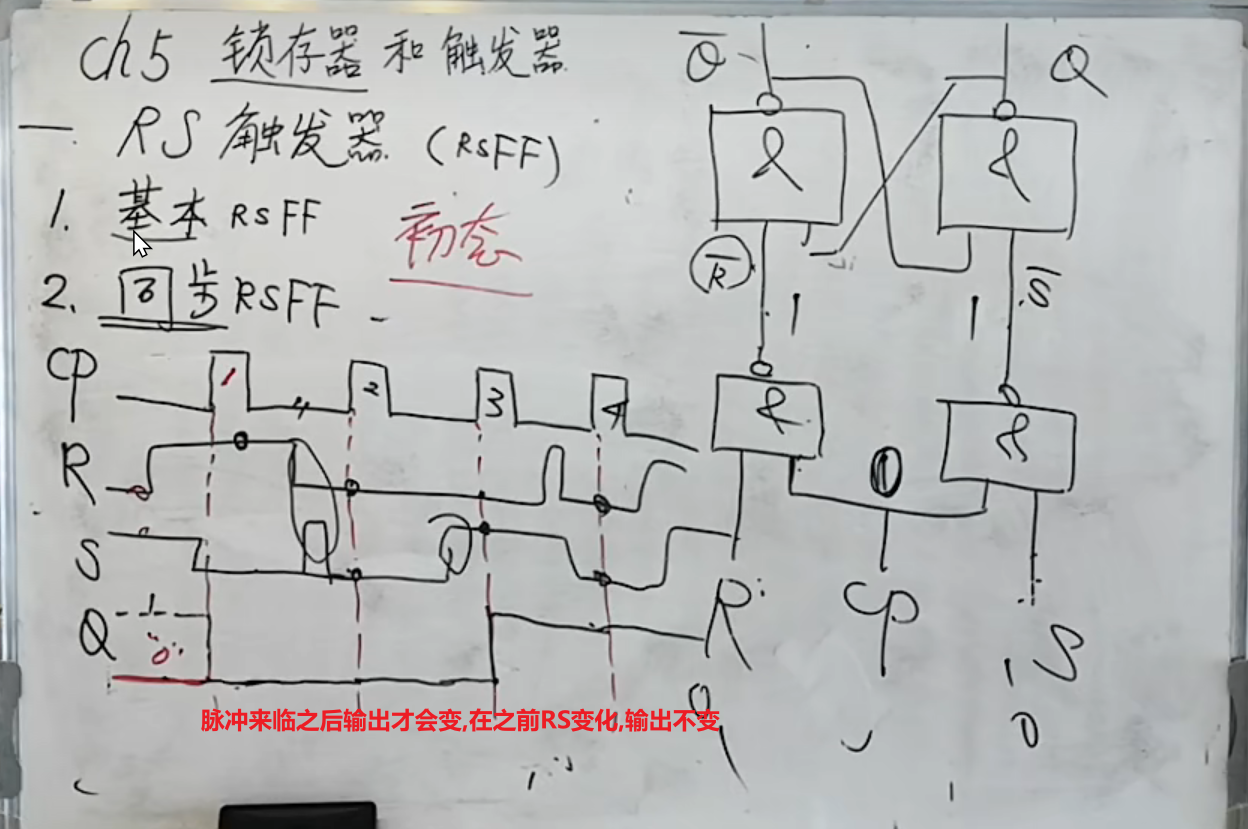

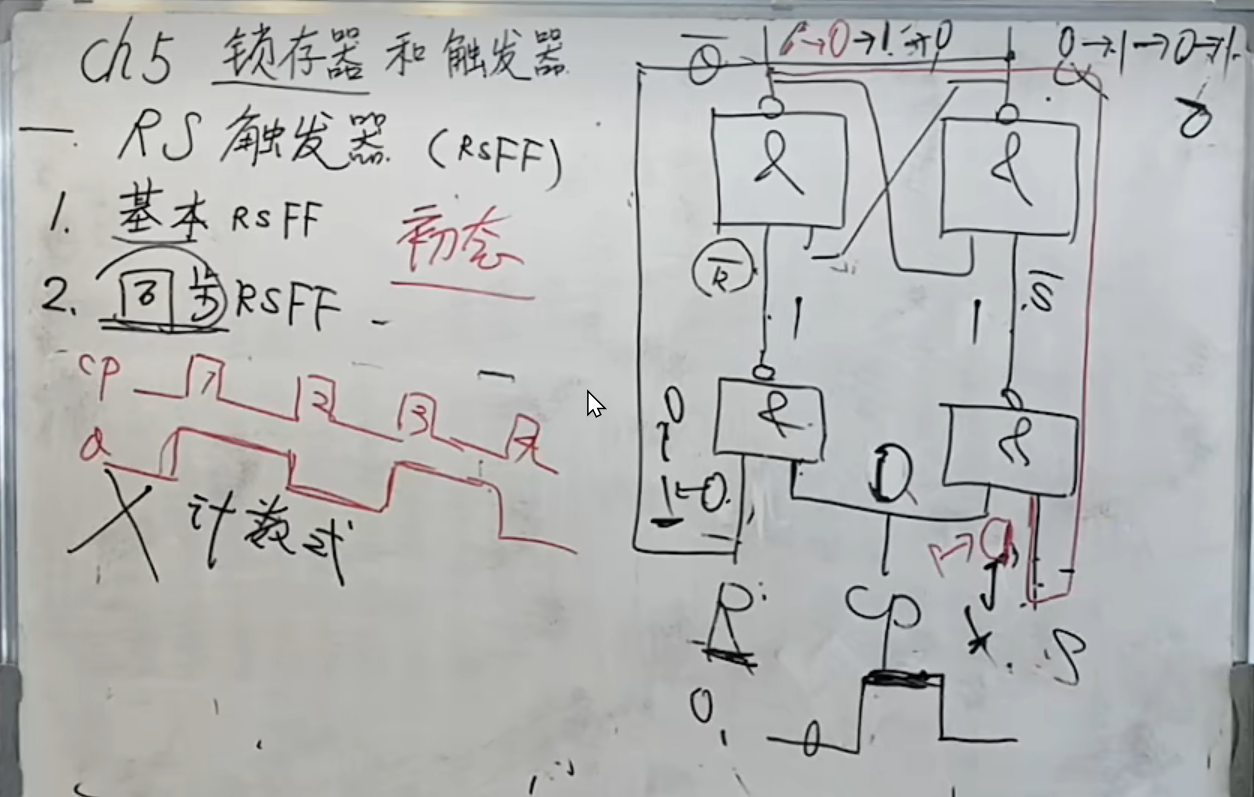

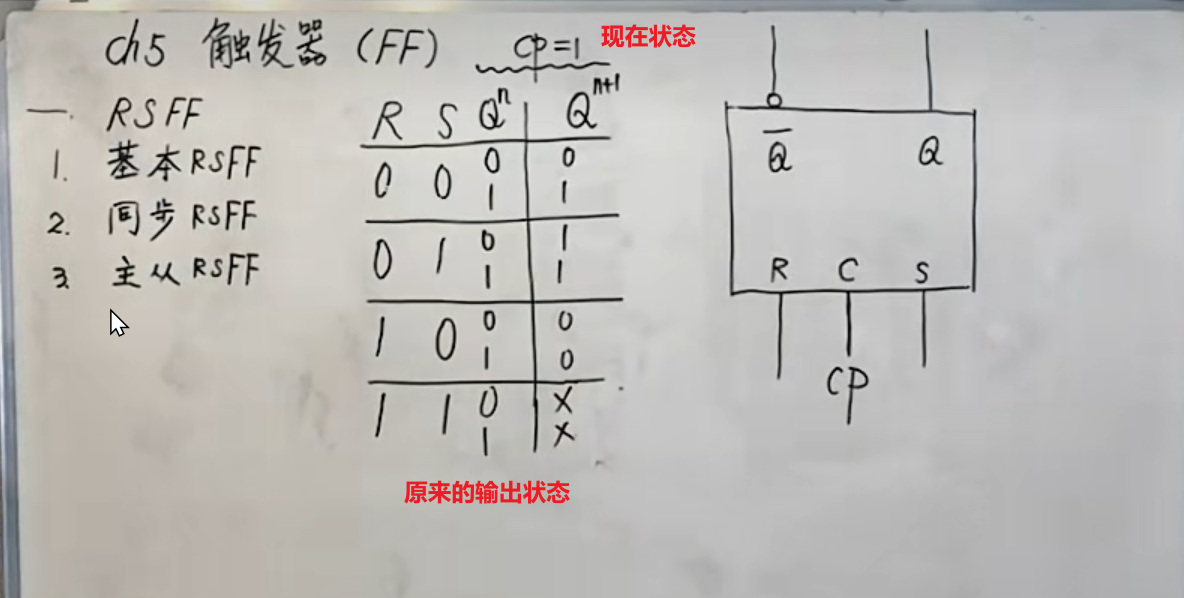

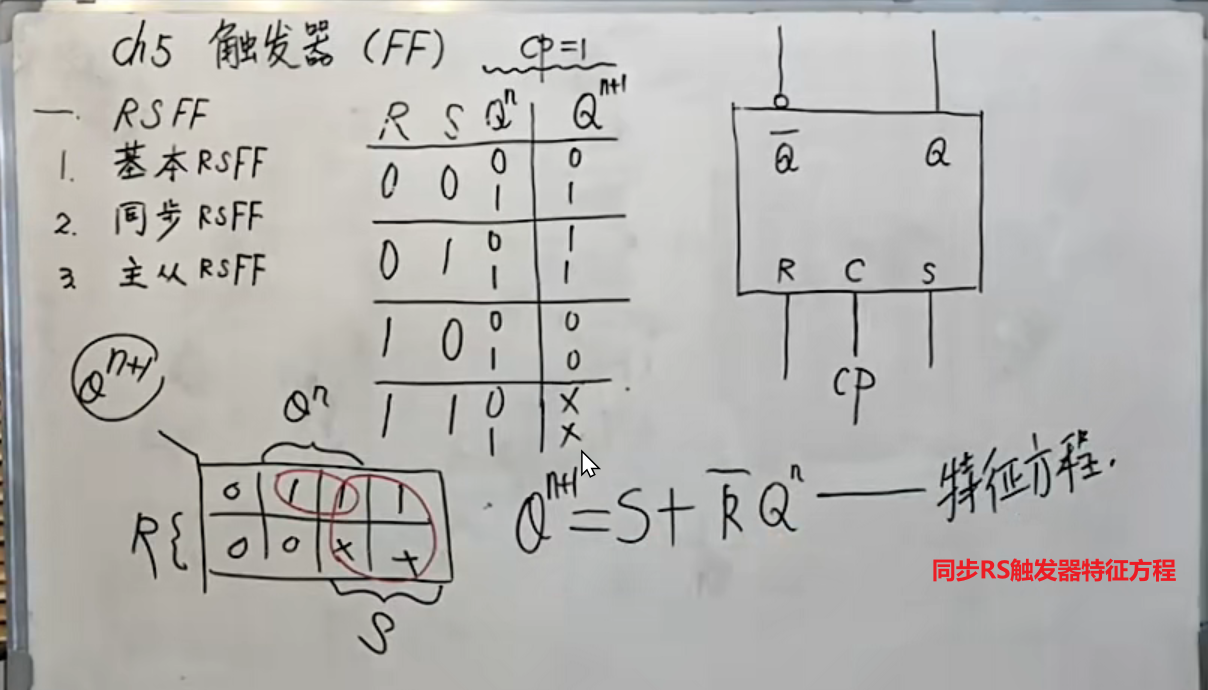

3.2同步RS触发器

- 基本RS触发器存在一些问题,由于组合逻辑的延迟,导致出现一些中间状态错误

cp:clk pluse 时钟脉冲

- CP = 0的时候,同步触发器输出不变,只有来了脉冲输出才可能发生变化

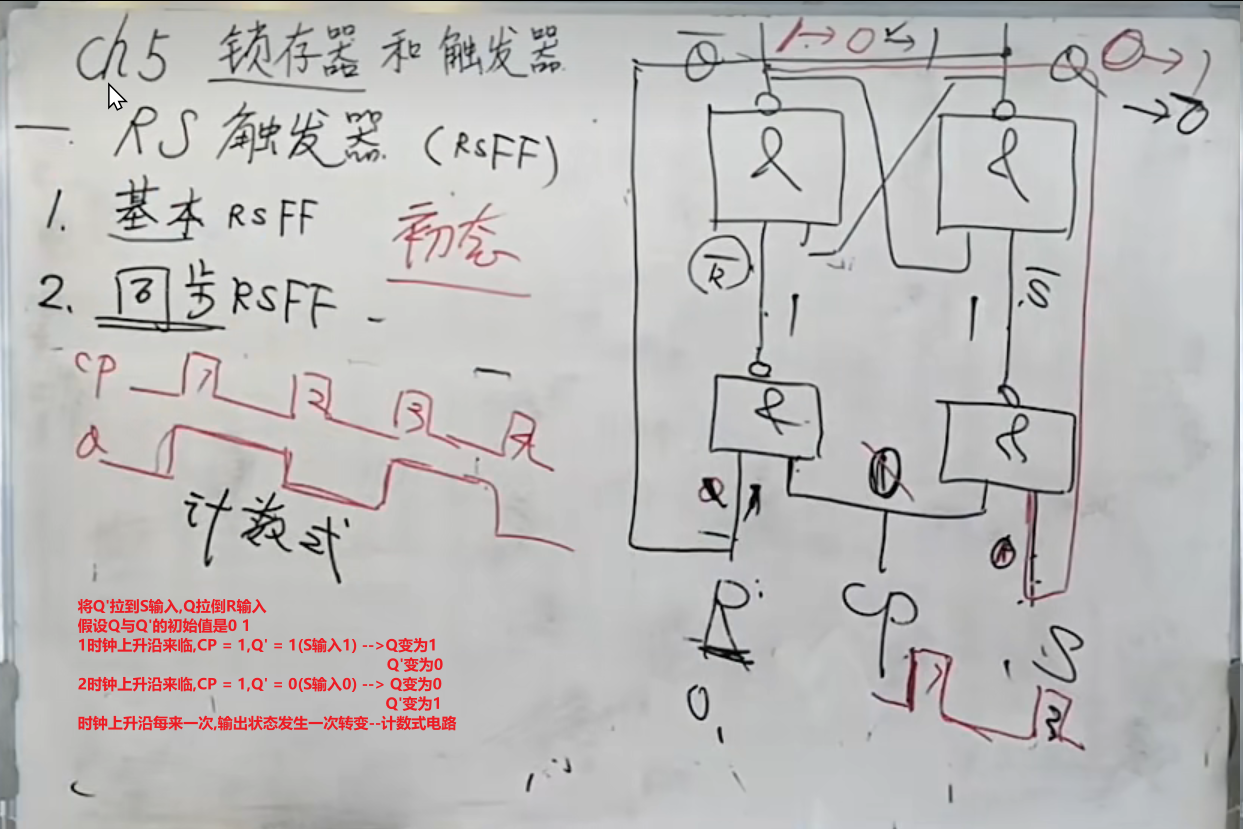

同步RS触发器是不能构成计数式电路的,因为CP上升沿来临之后,会维持一个电平时间,在这个时间内,CP仍然是1,RS端的输入仍然可以进行输入,进行空翻(一次CP来临,输出状态发生多次变化,空翻次数取决于电平时间长短)

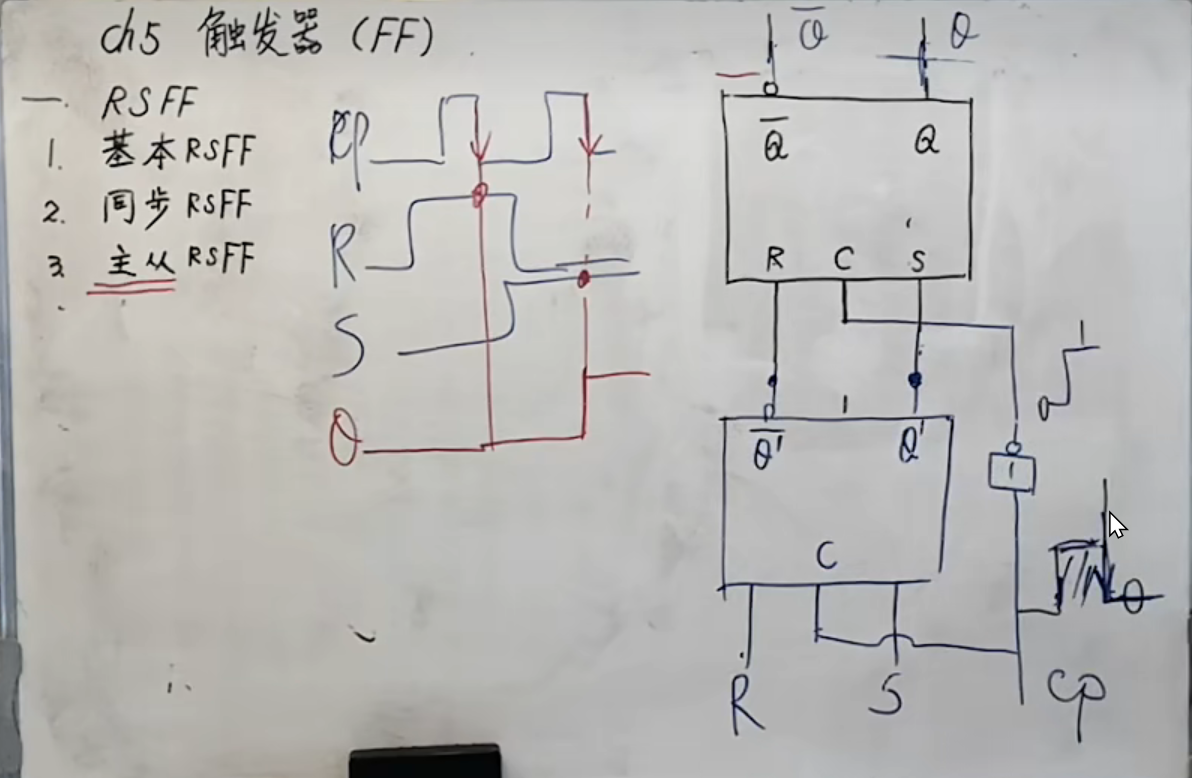

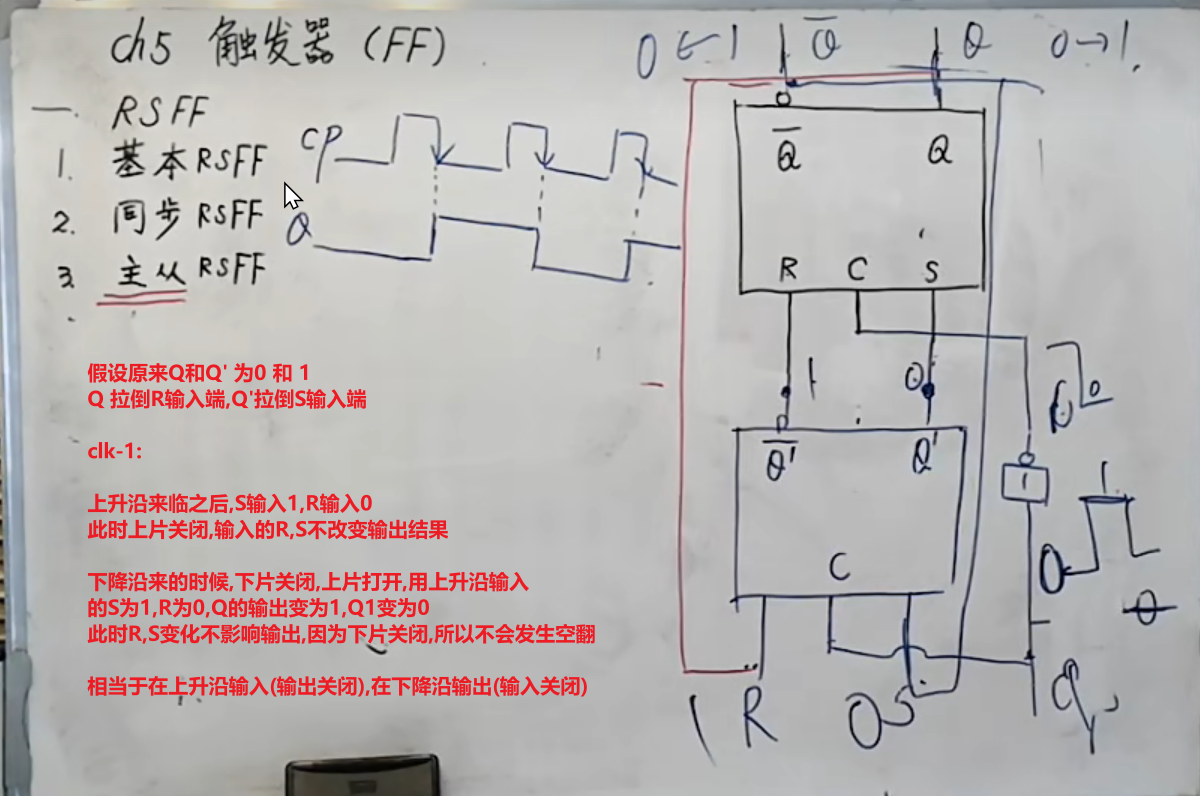

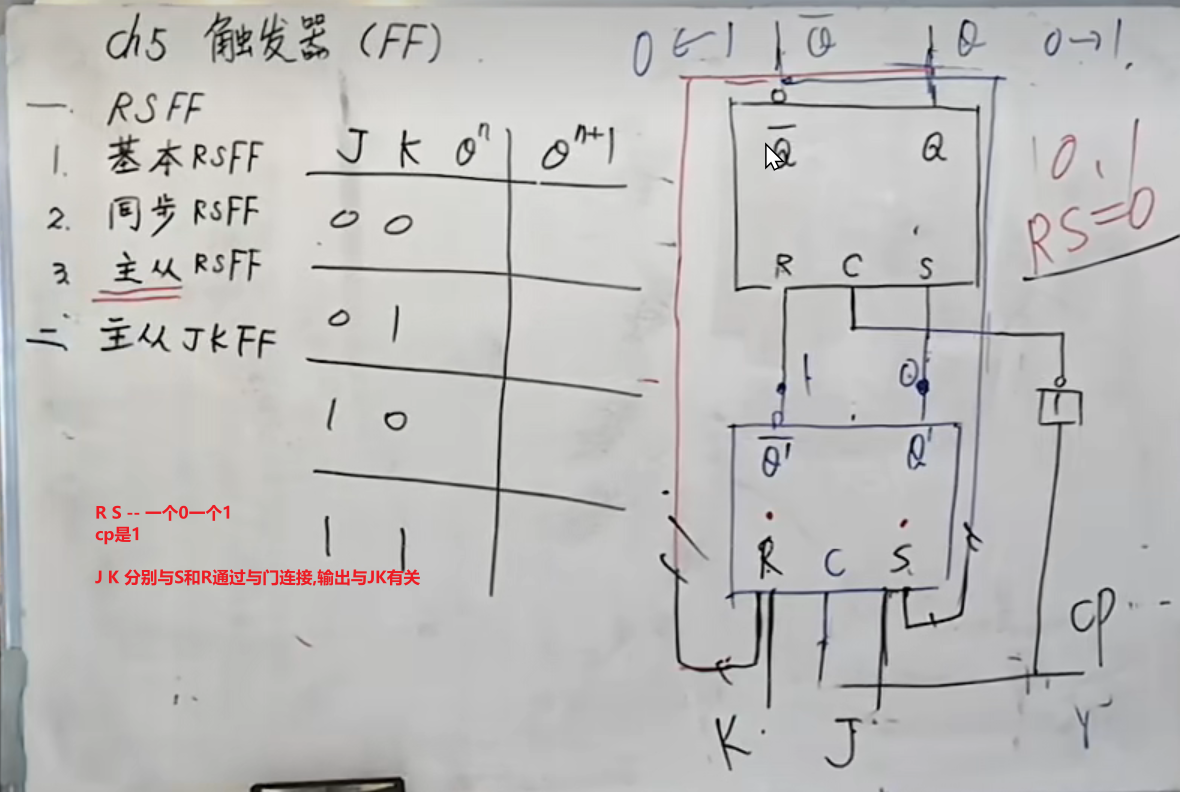

3.3 主从RS触发器

- 原来的状态是输入,可以借助卡诺图写出方程

为了解决同步RSFF的空翻,引入主从RSFF

- 使用两个同步RSFF组合得到主从RSFF,CP端连接的时候,要加一个非门

- cp为1的时候,下面的触发器打开,上面触发器关闭,信号不会影响最后输出;cp为0的时候,下面触发器关闭,RS变化不影响内部的状态,上面的触发器打开

- 最终输出的时刻,是在CP的下降沿的时候

- 主从RSFF实现计数式电路,不会出现空翻

RS触发器总会有一种情况不允许出现,在实际使用的时候可能出现问题

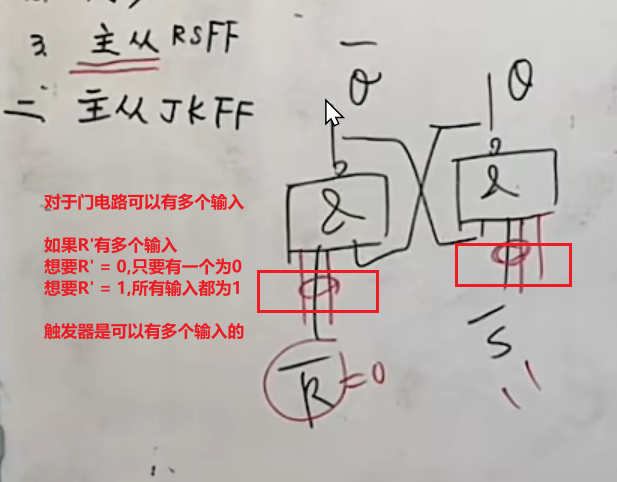

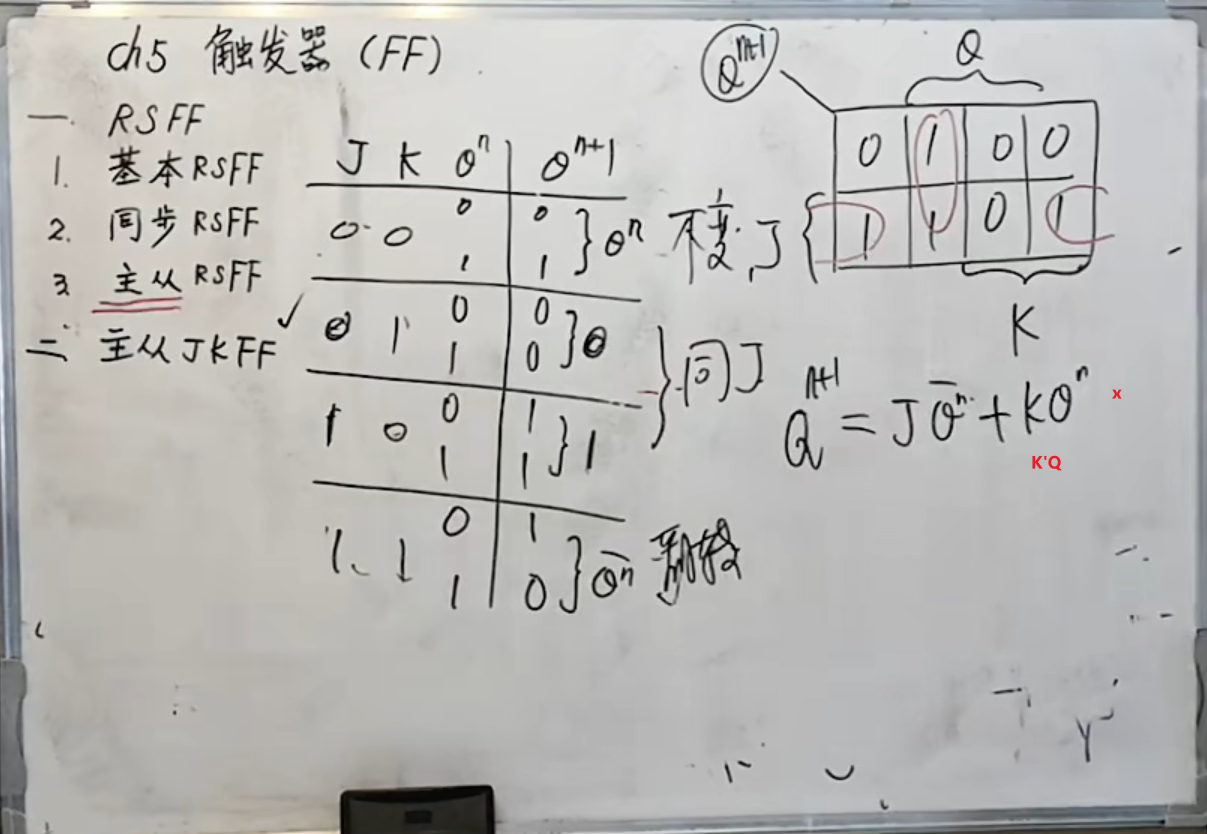

4.主从JK触发器

主从JK触发器是在主从RSFF的基础上演变过来的

触发器是可以有多个输入端的

- J,K都为0,经过与门之后,输入都为0,输出不发生变化

- J,K都是1,经过与门之后,输出结果只与R,S有关,相当于一个主从RSFF实现计数输出

- J为0,K为1,经过与门之后,S端等效输入为0,那么就不会置1,将置1的可能性封锁掉了,所有输出都为1

- J为1,K为0,经过与门之后,R端等效输入为1,那么就不会置0,将置0得可能性封锁掉了,所有输出为0

00不变,11反转,11,10同J

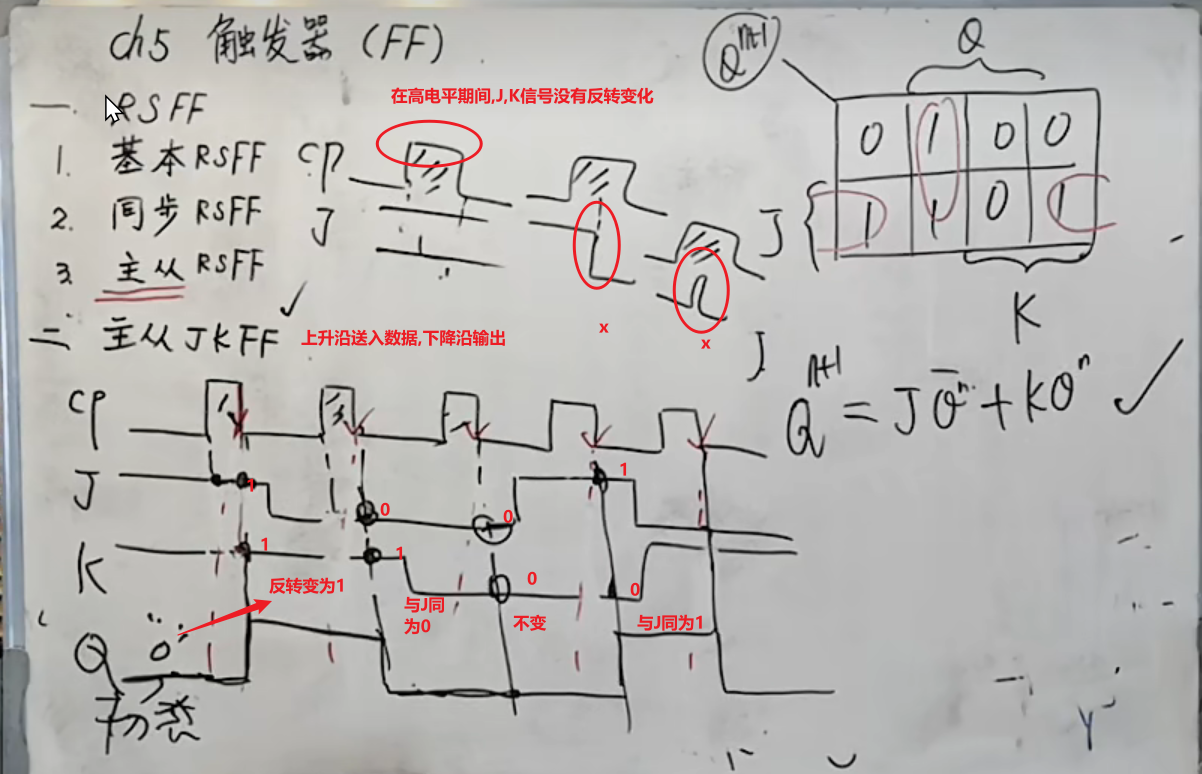

波形练习 - 在cp等于1期间J,K不发生变化(一次发生变化),如果发生变化,会出现问题

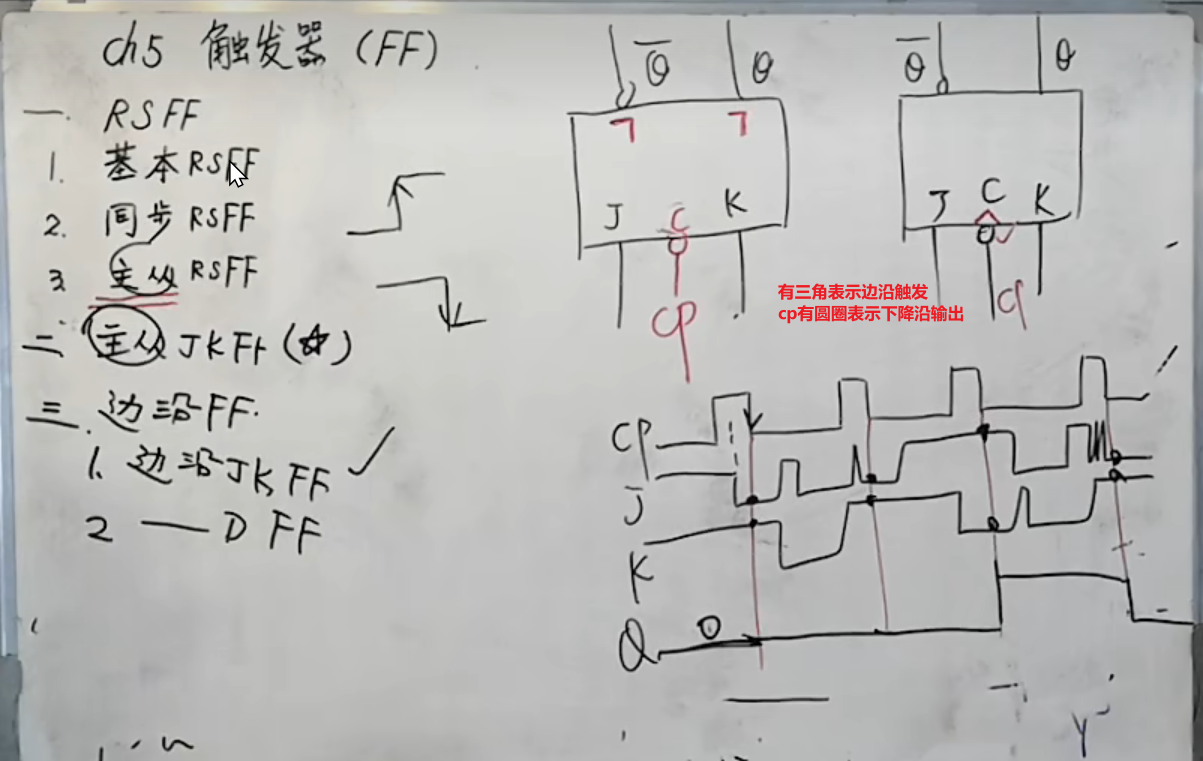

5.边沿FF

5.1 边沿JKFF

取决于cp的上升沿和下降沿,非常的可靠

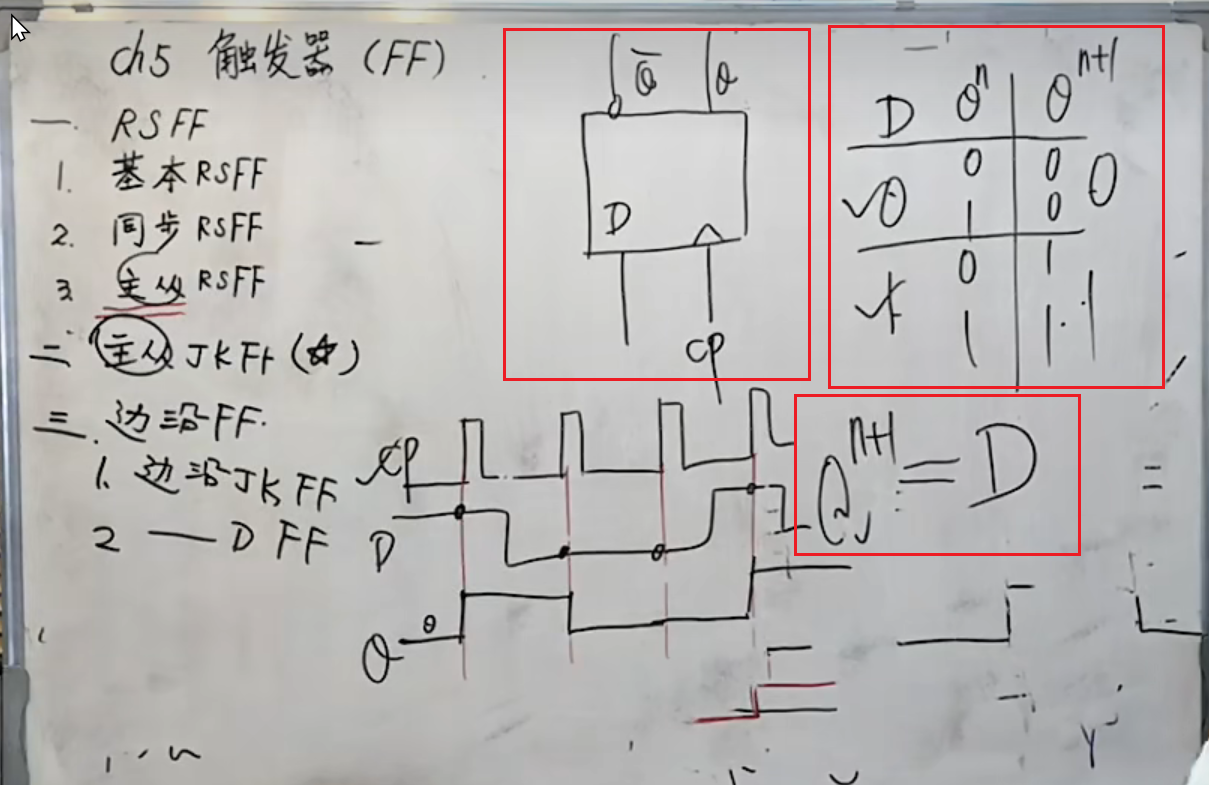

5.2D触发器

只有一个输入端,另外一个是CP,不管原来的状态是什么,脉冲来临之后,输出等于输入

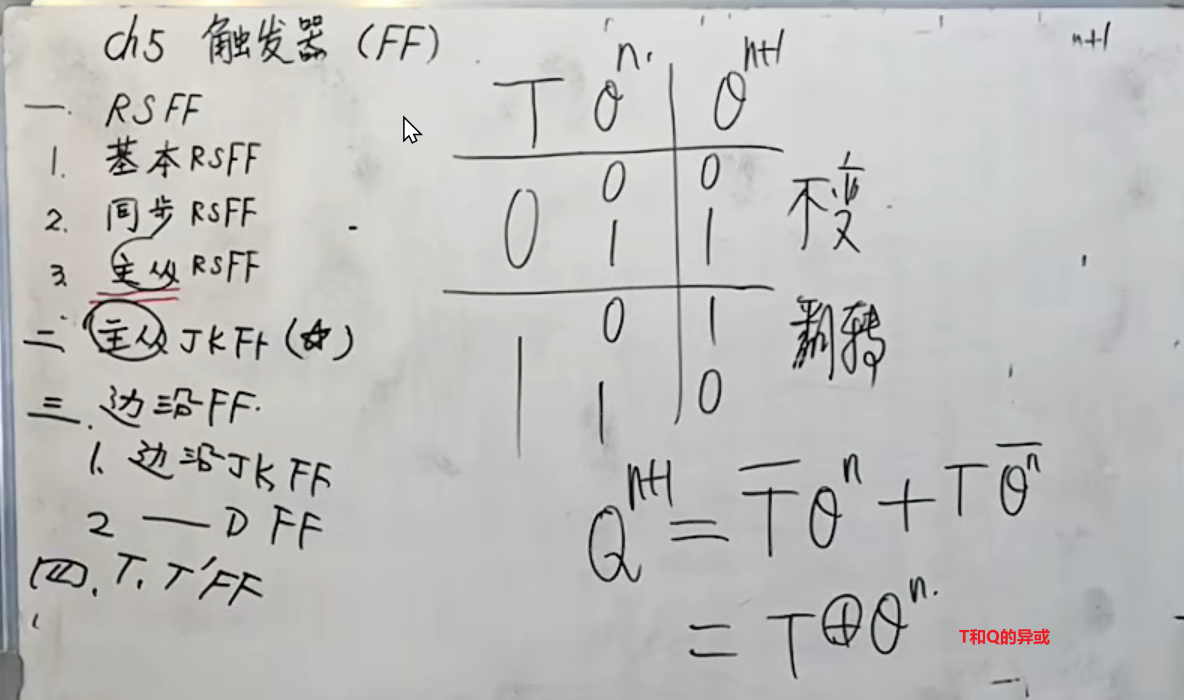

6.T触发器和T'触发器

T=1的时候的触发器就是T'触发器