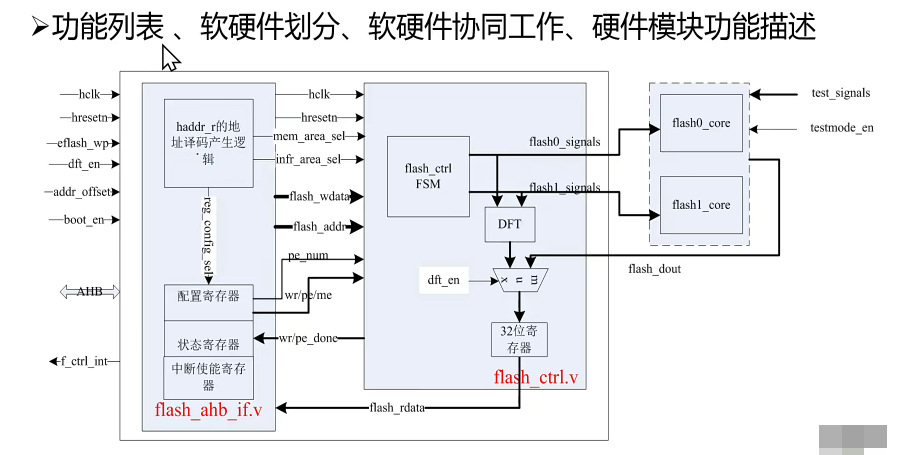

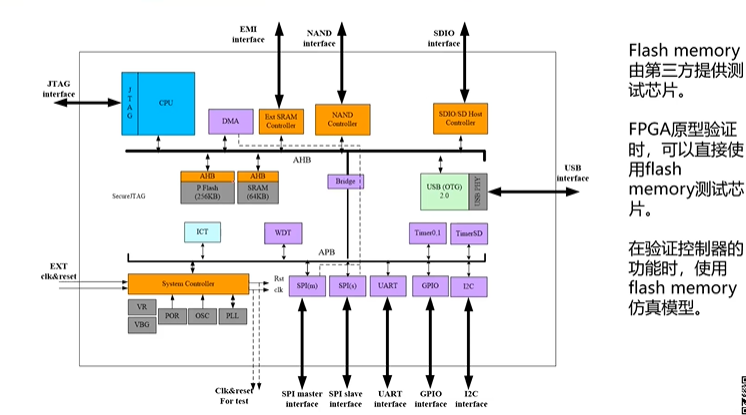

基于AHB_BUS的eFlash控制器设计-软硬件系统设计

eFlash软硬件系统设计

- 软硬件划分

- 划分好软硬件之后,IP暴露给软件的寄存器和时序如何?

- 文档体系:详细介绍eflash控制器的设计文档

- RTL代码编写:详细介绍eflash控制器的RTL代码

1.文档体系

1.1 架构设计文档

- 配置寄存器 -- CPU要写,需要进行读写擦操作,需要配置相应的寄存器,产生wr/pe/me信号

- pe_num -- 擦除哪一页,从配置寄存器中

- 状态寄存器 -- CPU要读,产生中断(interrupt)的时候CPU会读取状态寄存器

- 中断使能寄存器 -- CPU要写,CPU决定是不是能产生中断

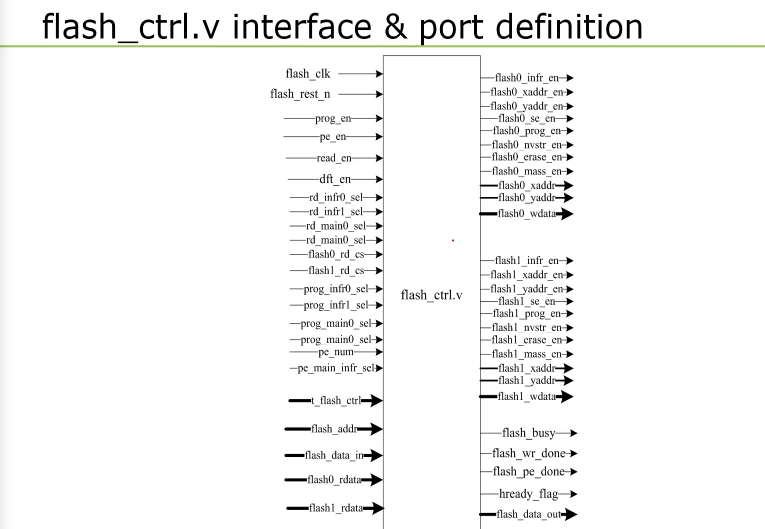

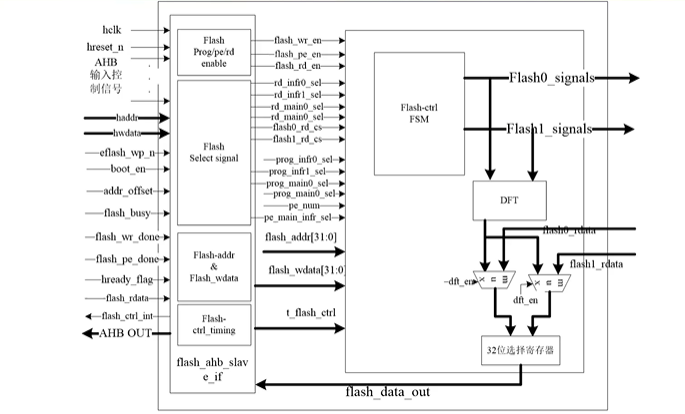

flash_ctrl.v输入 - flash_clk和flash_rest_en

- prog_en/pe_en/read_en/dft_en -- 操作指令

- 选择flash0或者flash1,选择information block或者main block

- 页擦需要知道pe_num -- 9bit

- t_flash_ctrl -- timing控制信号

- flash_addr和flash_data_in -- prog操作用到的的信号

- flash0_rdata/flash1_rdata -- read信号

flash_ctrl.v输出信号 - infr/xe/ye/se/prog/nvstr/erase/mass1/xadr/yadr/wdata -- 信号

- flash_busy -- 返回给状态寄存器

- flash_wr_done/flash_pe_done -- 返回给状态寄存器

- hready_flag -- 读的时候,通过hready_flag拉低延迟周期,达到读时间之后hready_flag拉高

- flash_data_out

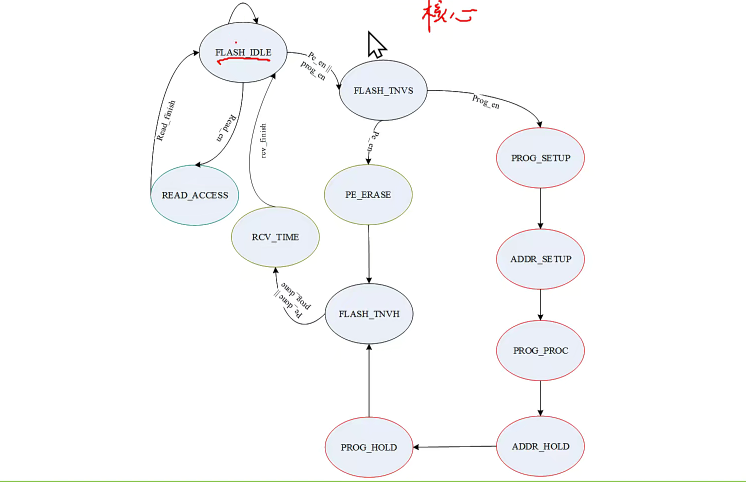

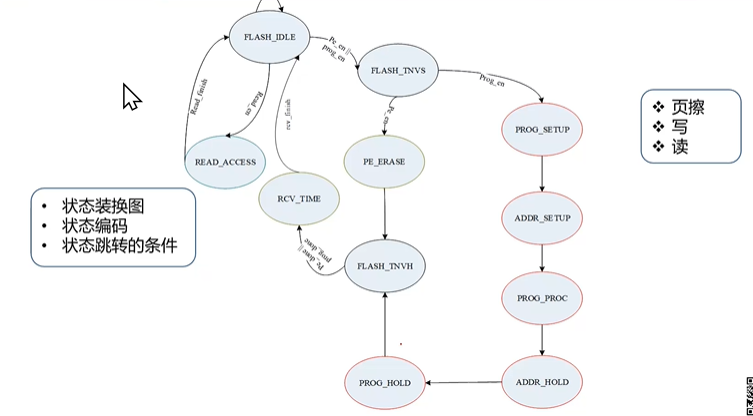

状态机

- 初始状态 -- FLASH_IDLE

- read_en起来之后 -- 进入readg_access,将xadr/yadr/xe/ye/se/infren等待准备好之后,读取数据,保存到寄存器中;在这个状态等待一定的时间,然后来read_finish信号,将上述信号拉低,读取结束;等待的时间一般超过read_access time(24ns)

- pe_en/prog_en都需要nvstr信号,都需要经过flash_nvstr状态,满足nvstr的建立时间之后,进入下一个状态,pe_en进入pe_erase状态;prog_en进入prog_setup状态

- pe_erase状态结束之后,进入flash_tnvh状态,之后进入recover_time状态

- 状态机就是时序图的翻译,其中的时间通过计数器计算时钟周期的个数进行控制

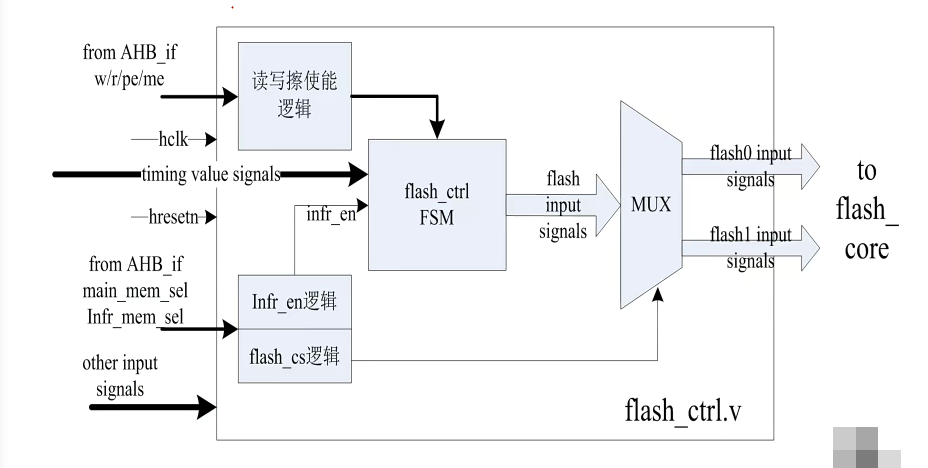

1.2 微架构设计文档

- 功能框图详细

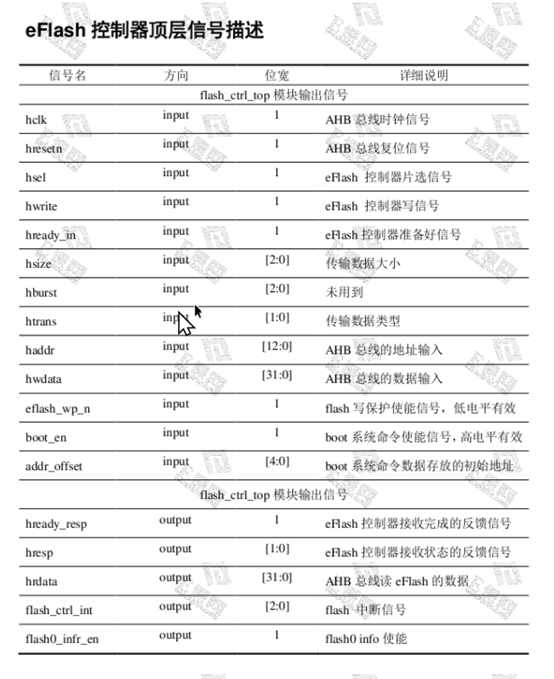

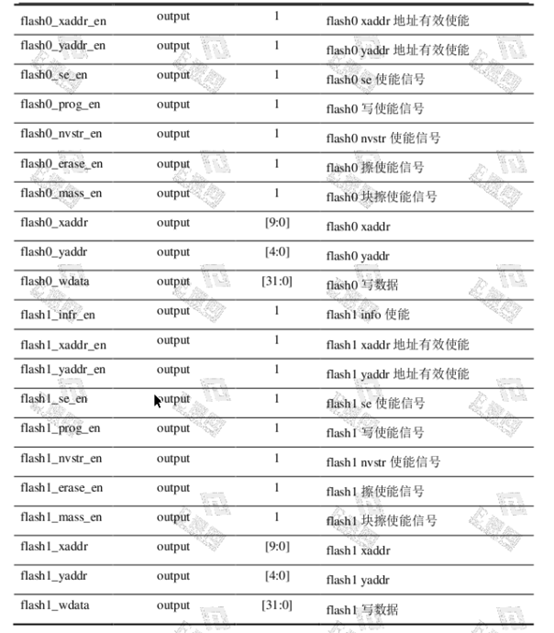

- 各个模块详细描述:模块框图,信号描述,模块功能定义

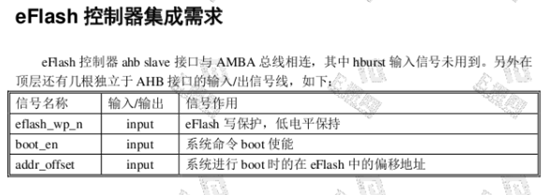

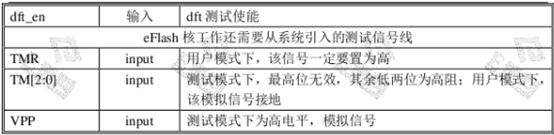

1.3 集成需求文档

2. Flash在SoC中的作用

- PFlash是由代工厂进行提供的,SoC的GDS(其中预留了PFlash的空间)和Flash在代工厂进行merge

- 在进行Netlist测试或者FPGA测试,PFlash本身不是以软核的方式提供的,是以GDS文件提供的形式,在进行FPGA测试的时候PFlash是没有的,FlashC与真实的Flash颗粒进行交互,可以通过FPGA测试

- PFlash -- program Flash,存储驱动和boot程序,CPU上电之后需要执行的程序

3. 3Flash在SoC系统中的偏移地址

- PFlash在所有IP中排在首位,其首地址是0x0000 0000,因为其中有boot程序所以放在第一IP

- PFlash_reg -- 寄存器空间pe和prog操作,擦除的地址和写的地址和数据存储在寄存器中,需要什么需要配置到寄存器中,就用使能信号进行控制

- CPU在上电之后,会访问0地址,所以要进行地址offset,将访问地址offset到boot区间,进行boot

- flash烧写bootloader时间较长,而且几乎不会变化,所以在出厂的时候就烧录好了

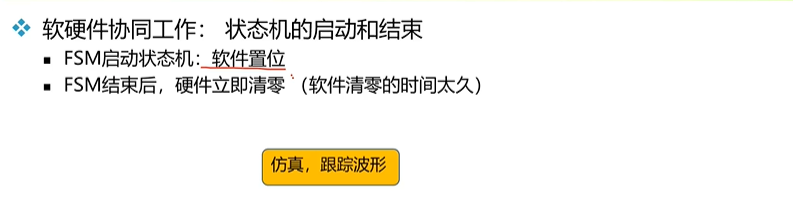

4.FSM:软件置位(置为1),硬件清零(置为0)

- 芯片是硬件执行一些指令,驱动Flash执行读写擦的操作

- 启动状态机的时候需要软件进行一些寄存器配置,然后发出启动状态机的信号启动状态机

- CPU如果要进行写操作,就将写使能寄存器写prog_en_r入1(其他时序寄存器配置完成),然后将这个信号1给Flash_ctrl,进行启动状态机,状态机完成一轮任务之后,如果不清除prog_en_r信号(置为0),则状态机一直识别其为1,就会一直运行状态机,在执行状态机完成一轮之后,需要清除prog_en_r

- 如果使用CPU进行prog_en_r清0,但是CPU不知道状态器什么时候接收到prog_en_r信号;如果想要CPU进行清0操作,需要让CPU等待FSM收到prog_en_r,就增加了一道时序约束

- 硬件清0,状态机启动之后,就任务是接收到了prog_en_r,状态机在接收到操作信号之后,可以进行内部存储操作使能信号,就不需要prog_en_r,可以将其清除;还可以在状态机运行后期,在从Trcv状态向IDLE状态跳转的时候,将prog_en_r清0,当FSM处于IDLE状态之后看到prog_en_r已经置为0了,就不会继续进行工作,知道CPU开启下一轮操作信号来

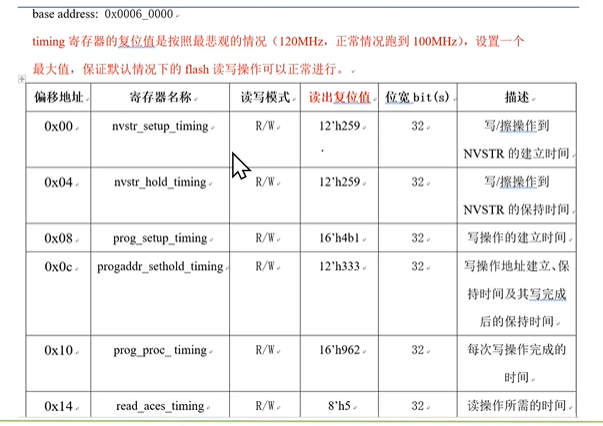

5.时序配置寄存器的默认值

- 按照最悲观的值配置时序寄存器

- 120MHz,一个周期是8.33ns,5000ns/8.33 = 600.2--> 601 -->十六进制259

- 读出复位值就是counter的计数值

6. 状态寄存器(硬件置位,软件清0)

- 任务完成后,IP产生中断给到CPU,CPU通过中断服务程序,处理响应中断

- 任务完成之后,IP返回的中断信号会被拉高,CPU在看到中断信号拉高之后,需要进入中断服务程序响应中断,CPU在处理完中断之后,需要将中断信号拉低,如果不处理中断信号,中断信号一直拉高,CPU一直处于处理中断的状态中,导致CPU死锁,不能处理其他业务,处理中断信号不能通过硬件,因为硬件不知道CPU何时处理完了中断,所以要通过CPU使用软件的方式处理中断信号,当CPU处理完成中断之后,将状态寄存器清0,中断消失

- 写1清0:当CPU向状态寄存器写入1的时候(并不是寄存器的值是1),就将状态寄存器清0

7.寄存器

- 在进行DFT的时候,将Flash颗粒bypass掉