基于AHB_BUS的eflash控制器设计-02

基于AHB-BUS的eflash控制器设计

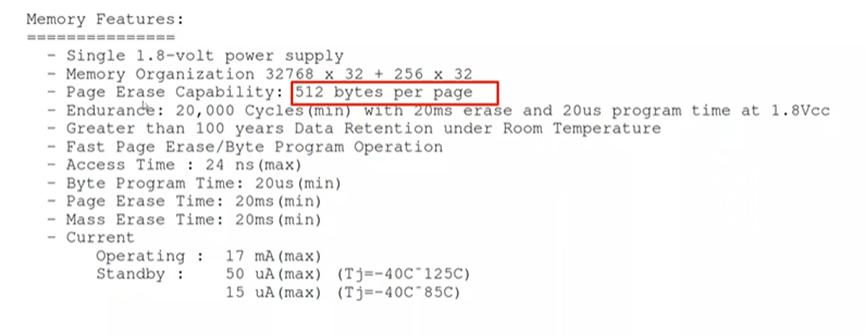

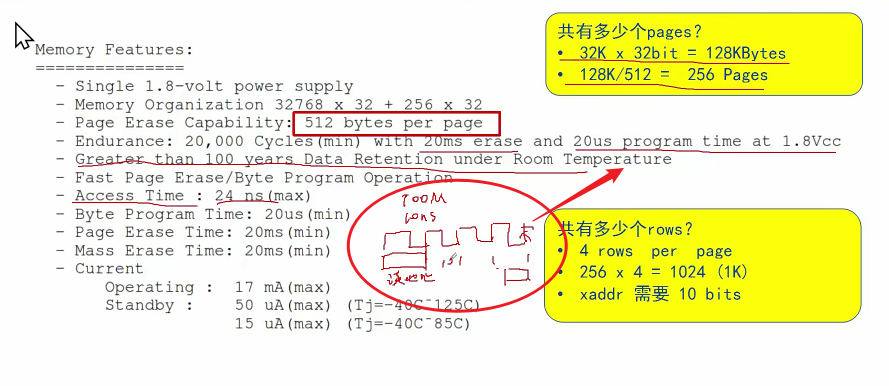

1.Flash Spec

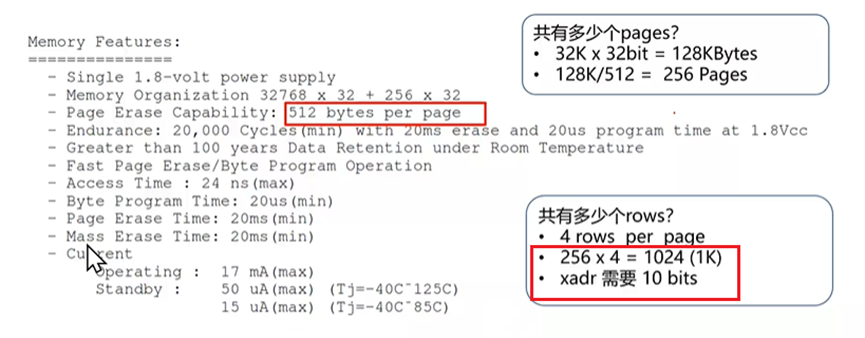

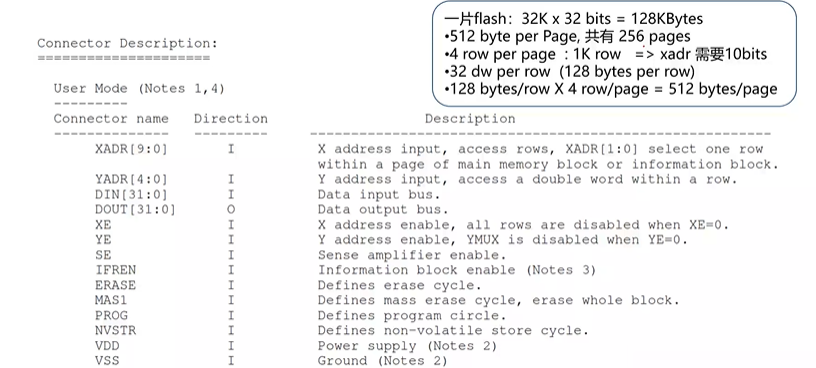

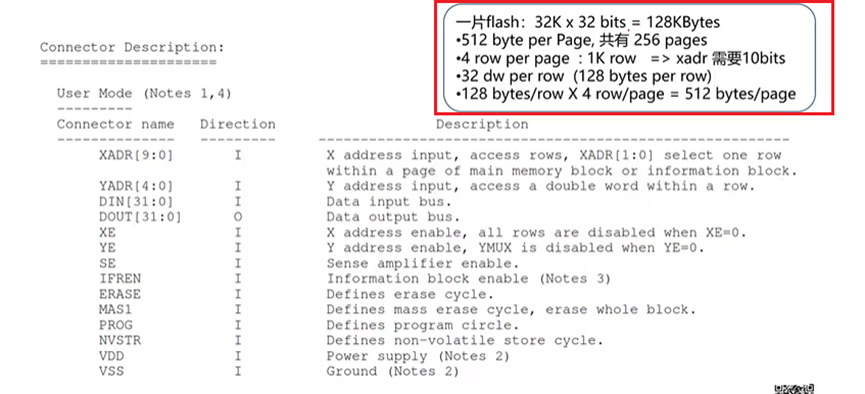

1.1 地址映射

- XADR是10bit?因为一共有1024行

- 每一行128byte容量,每次读取的粒度就是一个double word-32bit-4byte,所以一行有32个dw。

- 如果要读取一个dw的数据,除了需要知道其存在与哪一行,还需要知道它存在于哪一列。所以需要一个纵坐标地址YADR,32个dw每行,所以需要5bit的地址。

- 地址映射:首先将memory分成page,page分成row,row分成double word。

- 如果是information block,其容量为256*32bit(256个dw),一行有32dw,所以需要8行,地址表示为YADR的五位加上XADR的低三位一共8bit地址,表示寻址256个dw

- XADR表示选中某一个行,YADR表示选中某行中的32bit,如果存储容量变为64K*32bit,XADR变为[10:0]的11位,YADR仍然是[4:0],每行存储的容量不变

- XADR表示选中行,如何通过XADR得到page地址,XADR中的[9:2]表示page地址,[1:0]表示每个page中的行

- 两片存储体选择,在最高位添加一位进行选择

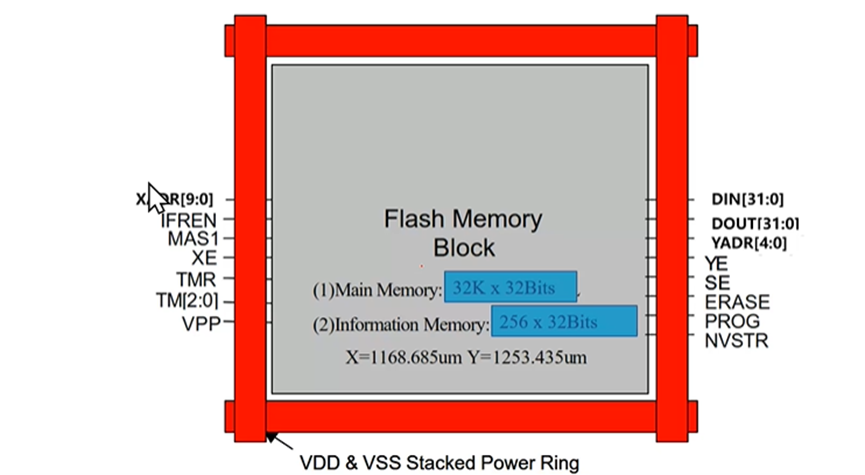

1.2 信号

- eFlash没有clock,所以信号要自己生成

- XADR—寻址的是行,10bit,低两位表示page中的哪一行,[9:2]表示选择的page,[1:0]表示 选择page中的哪一行

- YADR -- 一行中有32个dw,所以使用5bit

- DIN [31:0]—写数据

- DOUT [31:0]—读数据

- XE—拉高表示XADR是有效的,使能每一行的数据,地址驱动到端口上之后需要在enable的作用下确定是否开启行选择

- YE—拉高表示YADR是有效的

- SE—灵敏放大器的使能信号,读数据的时候,读某行某列中存储单元的数据,存储在晶体管中,驱动能力不够,需要灵敏放大器,将信号读到的数据送到输出端

- IFREN—拉高表示访问的是information block,拉低表示访问的是main block,通常可以设置为1

- ERASE—按页擦除

- MSA1—按块擦除

- PROG—数据写入,程序烧录

- NVSTR—非易失性操作(erase和program)

- VDD—电源

- VSS—地

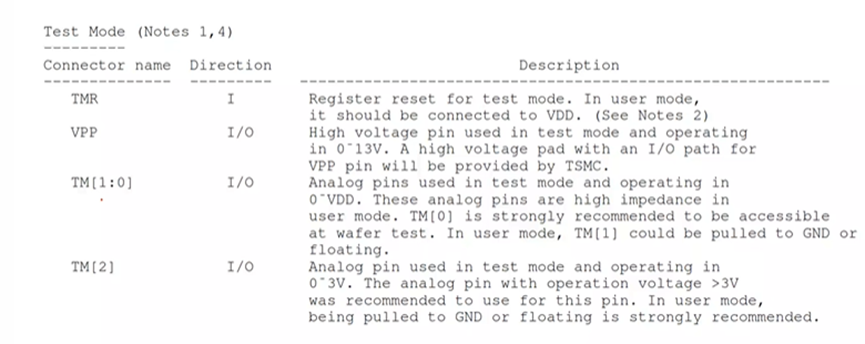

1.3 测试信号

上述都是function mode下的信号,它依然会有测试mode的接口,它的测试更多的是通过基台进行输入激励进行测试。

1.4 电流\电压

- Standby的时候,电流以微安形式存在,在工作状态下的时候,电流以毫安形式存在,在不同的模式下,电流相差一个数量级。不同情况下,电流不同,功耗不同。

- SRAM是一维的寻址,eFlash是二维地址。

- Word是多少位的(32位或者是16位),是根据不同的系统确定的。

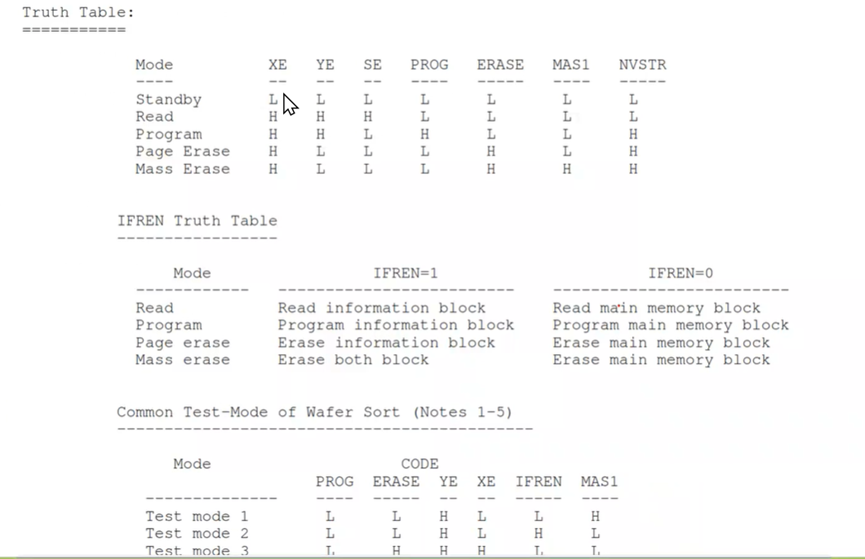

1.4 读写擦信号

- Standby—所有的信号都拉低,可以认为eFlash没有被片选到,此时的功耗是最低的

- Read—SE需要拉高(SE信号只有在读的时候拉高),读的时候需要知道dw的位置,XE,YE都需要被拉高;不是擦除和写入操作,所以PROG和ERASE拉低;不进行eFlash内部数据的更改,所以NVSTR拉低。

- Program—Read和Program的访问单位都是32bit,PROG需要拉高,XE,YE需要进行拉高;当前对于eFlash进行内容操作,非易失性操作NVSTR需要拉高。

- Page Erase—ERASE信号拉高,XE信号拉高,NVSTR信号拉高

- MAS1 Erase-- ERASE信号拉高,MAS1信号拉高,XE信号拉高,NVSTR信号拉高。进行Page Erase和MAS1 Erase的时候,以页为单位,以行为粒度进行擦除,所以YE拉低。

- IFREN—为1的时候,操作的是Information block,为0的时候,操作的是main block。

- Test mode信号主要通过基台进行测试,不需要进行内建自测试

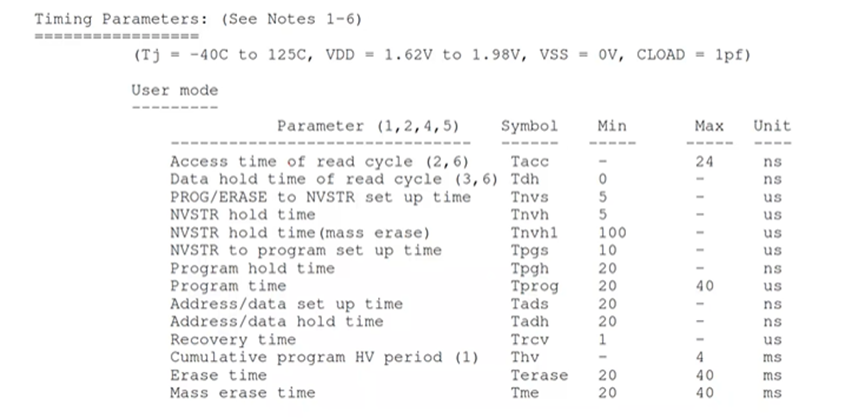

1.5 时序参数(Timing Parameter)

- 设计—》配置寄存器—》将这些参数写成灵活可变的,方便进行修改/更新换代

2.时序说明

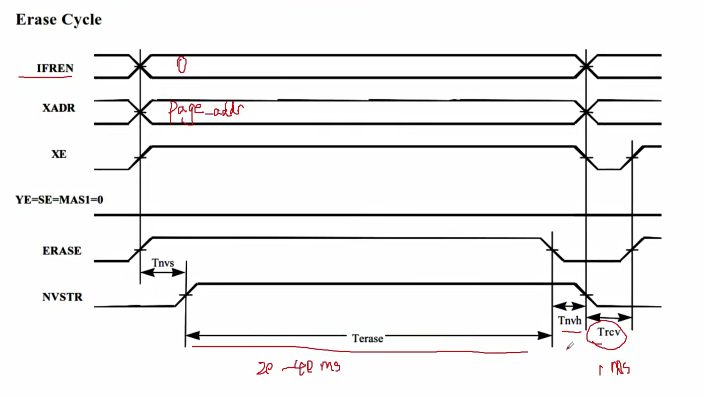

2.1 擦除时序

- 将IFREN信号拉起来,表示擦除那一部分(information block还是main block)

- Page擦除,需要将4个row对应的地址XADR驱动到总线上,不需要考虑YE

- XADR是有效的

- SE是拉低的

- ERASE信号需要拉高,在实际进行擦除的时候ERASE和NVSTR信号同拉高(进行与操作),才会进行擦除。

- 时序约束:PROG/ERASE to NVSTR setup time-Tnvs,NVSTR信号上升沿到达之前,ERASE信号需要保持的时间。上述表中给出Tnvs=5us,如果100M时钟频率,一个周期是0.1us,那么需要维持50个cycle的Tnvs时间。

- Terase = 20-40ms,通过计数器counter进行计数,当达到Terase时间之后,撤销ERASE信号

- 撤销ERASE信号之后,还有一个时间约束,NVSTR需要保持一段时间,Tnvh,之后才能撤销NVSTR

- 撤销NVSTR信号之后,紧接着有一个Trcv,在这段时间内不能进行任何的操作,用于系统恢复

2.2 eFlash时序是异步设计

eFlash是没有时钟的设计,异步设计。SRAMC是同步设计,在时钟的上升沿或者下降沿进行采样操作。

异步设计规范的是不同信号变化的时间间隔,谁先拉高,谁后拉高,两个信号之间信号间隔多久。具体信号保持多久需要使用计数器进行。

如何实现擦写的时序?FSM+counter

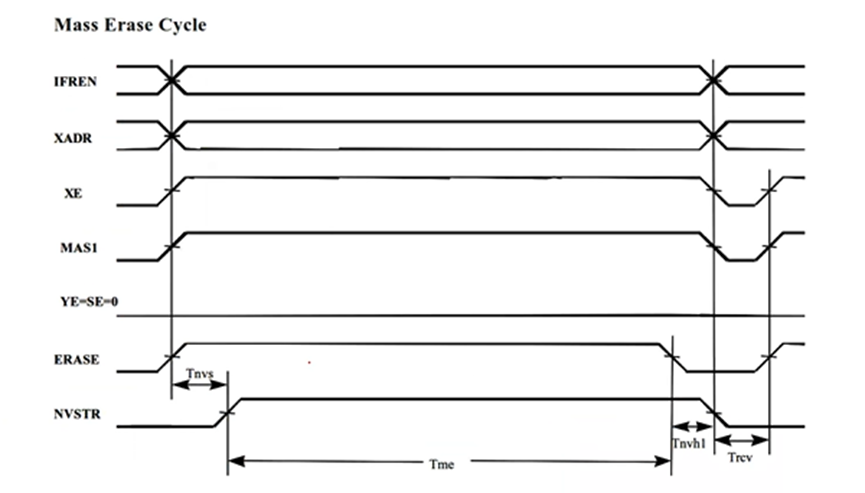

2.3 块擦除(Mass Erase Cycle)

- MAS1—信号需要进行拉高

- Tme和Terase信号可能是不同的(Page Erase和Mass Erase擦除的时间可能是不同的)

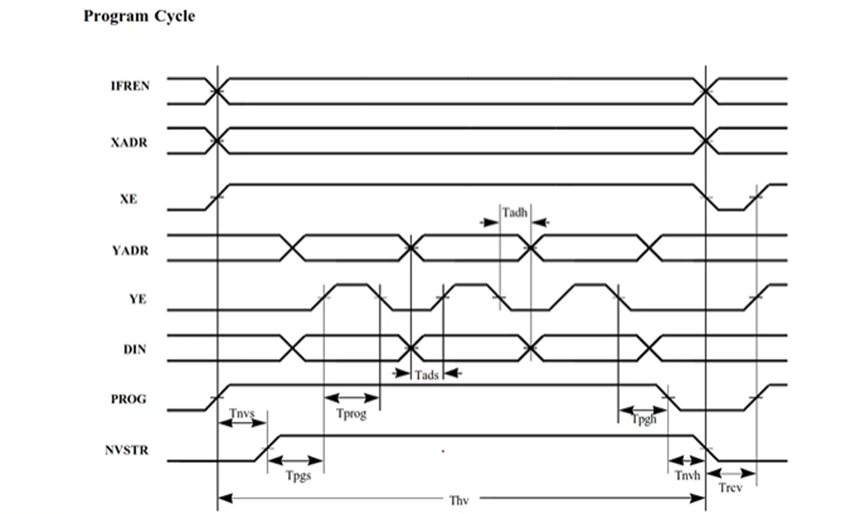

2.4 写时序(Program Cycle)

进行程序的烧录,也就是写时序

- IFREN—编程哪一部分

- XADR,XE需要进行拉高

- Y地址控制之前,PROG信号拉高,表示当前正在进行编程,在进行编程的时候可能对于一行当中的几个dw进行操作;编程操作更改了eFlash中的内容,需要NVSTR拉高。

- NVSTR信号拉高之前,PROG信号需要保持一段时间,满足NVSTR建立时间Tnvs

- Tnvs满足之后,经过一个Tpgs,之后就可以正常编程。Tpgs就是第一个NVSTR经过Tnvs之后到YE上升沿之间的时间,需要PROG保持稳定。

- YE拉高之前,需要将数据准备好,DIN并不是与YE同时拉高,在YE拉高之前DIN需要稳定一段时间,满足Tads。

- YE写一笔数据至少拉高Tprog时间,才能将数据写入。

- YE撤销之后,DIN和YADR需要保持一段时间,满足Tadh。PROG信号撤销之后,NVSTR需要维持一段时间Tnvh。

- NVSTR撤销之后,在之后的Trcv时间内不能进行操作。

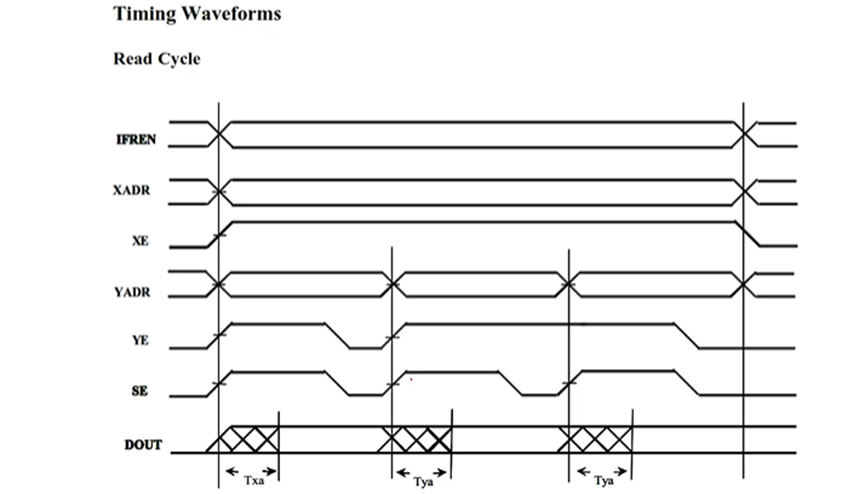

2.5 读时序(Read Cycle)

- IFREN—拉起

- XADR,YADR,XE,YE,SE,信号拉高

- 经过Txa之后,才能访问到读数据

- Txa是首次XADR之后,到首次读取数据的时间间隔;Tya是非首次XADR,切换列数据读取的时间

2.6 时序的控制

使用状态机控制

2.7 Flash模型编译仿真

- 拿到Flash模型之后,可以编写testbench进行测试,将激励打到Flash,对Flash进行读写操作,对比结果。

- Tiiming check—eFlash对于时序要求比较高,如果时序不满足要求,仿真的时候会警告,数据写入不了,所以将timing check关闭

- nospecify –关闭延迟模型

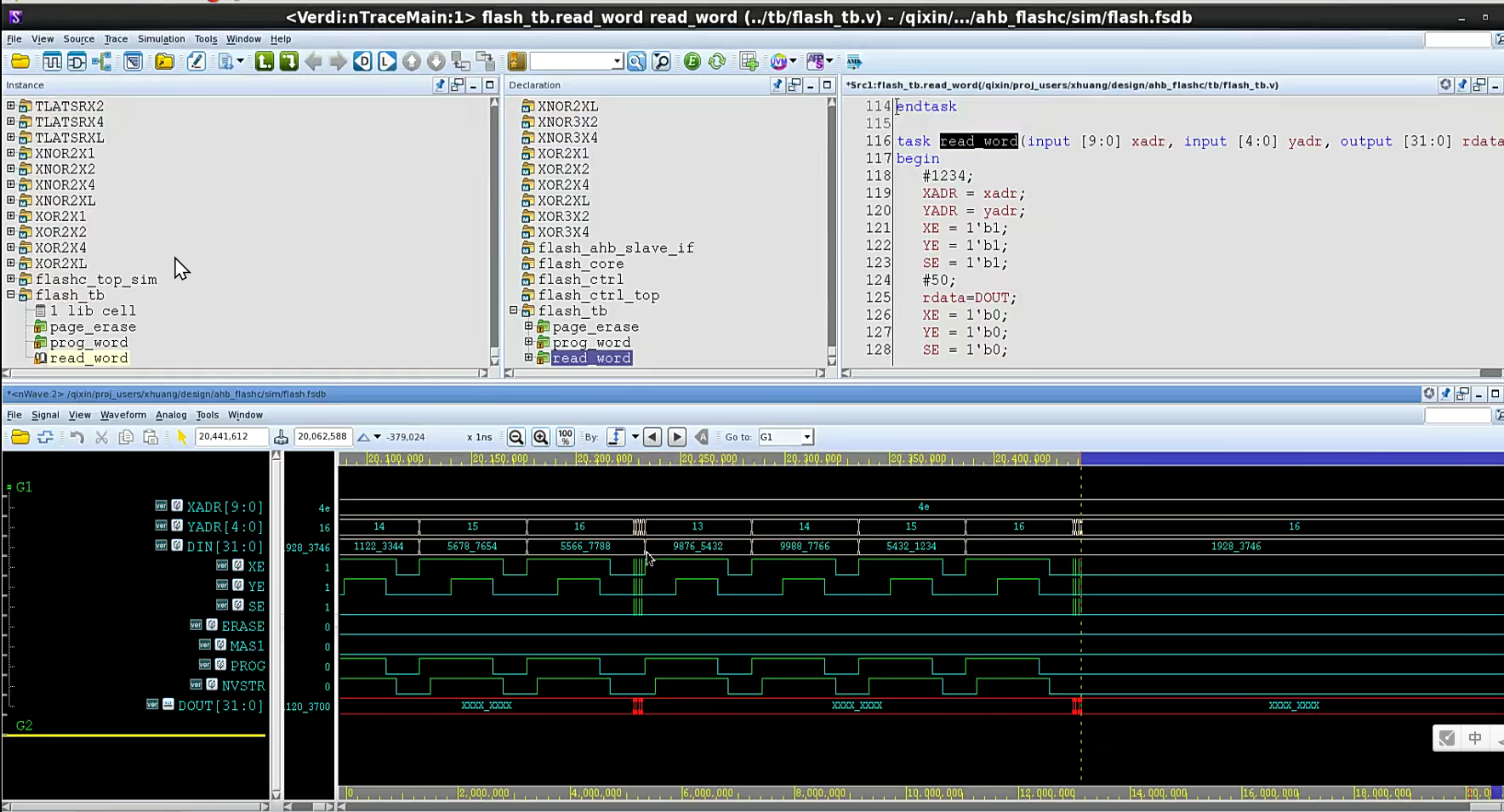

3.对于eFlash存储体的仿真

# 在Makefile设置一个verdi选项,产生fsdb文件

make run_rtl_verdi -- 产生fsdb波形文件