基于AHB_BUS的eFlash控制器设计-01

基于AHB-BUS的eflash控制器设计

SRAMC是单周期的读写,控制比较简单,没有状态机也没有软硬件的协同

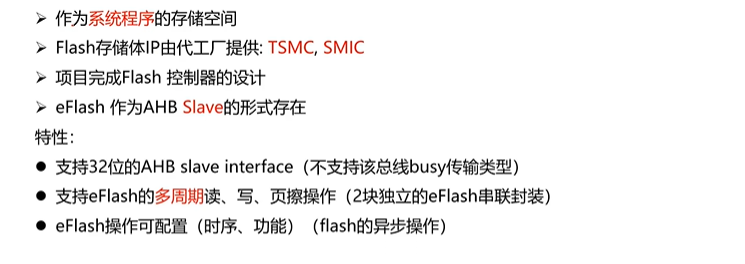

eflash是非易失性的存储器,可以进行读写擦除,它也是一个基于AHB_slave的模块

目录

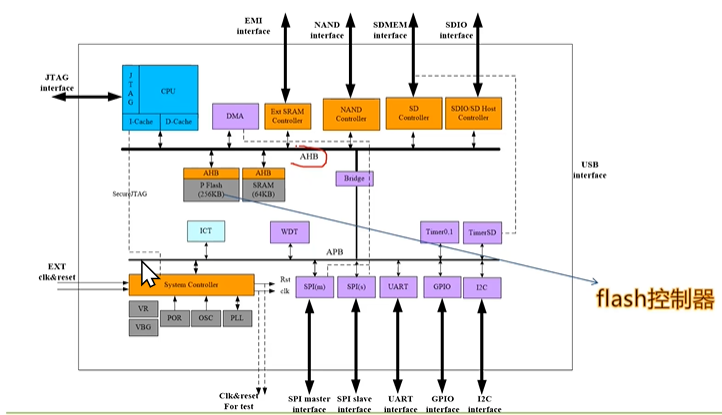

SoC内部内嵌了一个embeded eFlash,是集成在SoC中的

- Flash工艺

- 设计需求

- flash

- 文档体系

- 代码编写

- 仿真验证

1.Flash工艺

1.1 Logic vs Flash

Logic:在RTL完成之后,进行逻辑综合生成的standcell,就是Logic,掉电之后数据消失

Flash:由固核的方式,进行设计的时候如果想要集成一个Flash,可以直接进行调用,后期代工厂会进行合并;可以将其认为是一个黑盒子,其中的逻辑和布局布线都是做好的

1.2 易失性数据和非易失性数据

- 易失性存储体:电源掉电之后,数据丢失。SRAM上电的时候其中是没有数据的,通过上电之后CPU或者DMA将数据搬移进去,进行SRAM的初始化。DRAM用于内存,也是易失性数据存储体,需要定时进行刷新和充电,只有这样数据才能不断的进行保存。(s-静态的,d-动态的)

DRAM经常用于内存,因为其存储容量大;SRAM经常用于缓存,访问速度比较快 - 非易失性存储:掉电之后,数据并不会进行丢失。比如NorFlash,NandFlash,SSD,u盘,移动硬盘,机械硬盘。

- 非易失性存储体很多都是可移动的,想要将非易失性的存储体集成到SoC上就得到了embeded Flash-eFlash,eFlash集成在SoC中,其中可以存储一些上电之后的引导程序(这些程序几乎是不变的,出厂的时候由基台进行烧录在里面),boot程序。

2.位置

- 给CPU进行服务的,CPU上电之后需要一些引导程序,让CSoC处于待工作状态进行工作

- 黄色的是控制器,与AHB进行通信,从Flash读取数据

3.eFlash

- 可以存储boot loader程序和实际运行的程序,上电之后CPU读取boot程序,初始化SoC

- Flash由代工厂进行提供,可以提供RTL代码(软核),与工艺是深度绑定的

- 项目完成eFlash控制器的设计,eFlash的存储体已经有了,需要控制器对与eFlash进行读写擦除操作,实现eFlash的应用

- eFlash是以ahb_slave的形式存在的,设计一套控制器让CPU能够访问eFlash

- eFlash多周期的读写和页擦,其中的读写逻辑和结构比较复杂;SRAMC支持单周期的读写访问

- 支持两块eFlash的串联,如果当前需要eFlash的容量比较大,但是代工厂提供不了这么大的,需要将两块eFlash进行拼接起来

- eFlash操作是可配置的,flash的异步操作

- 支持eFlash中的boot区间的擦写保护,如果当前的eFlash正在进行boot操作,此时不能够进行写和擦除访问,否则如果在boot的时候更改了boot程序或者被覆盖了,会导致整个SoC的功能出错。所以在boot_en拉高的时候,进行屏蔽掉外部的读写擦信号。同时也可以防止代码的出错,误删,误擦等。

4.知识点

- AMBA总线

- 阅读Flash datasheet控制器的能力

- 利用行为级模型进行仿真

- 关于Boot概念

- DFT概念

- 文档体系(设计文档体系,验证文档体系)

- 底层驱动概念

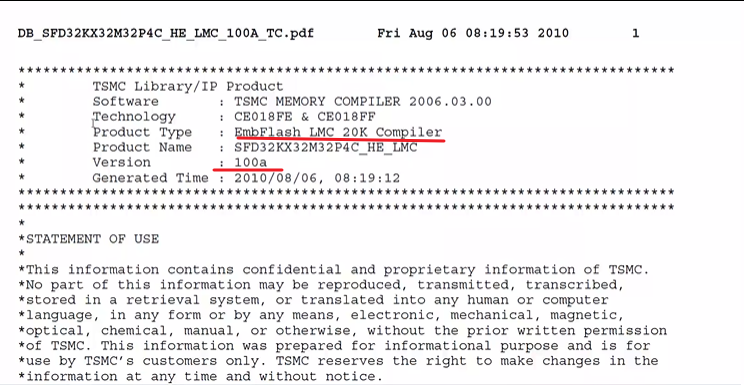

5.Flash

- 由代工厂提供的

- 提供各种文件(仿真,时序),一般不提供GDS,需要在工厂做merge(我们在GDS中预留空间)

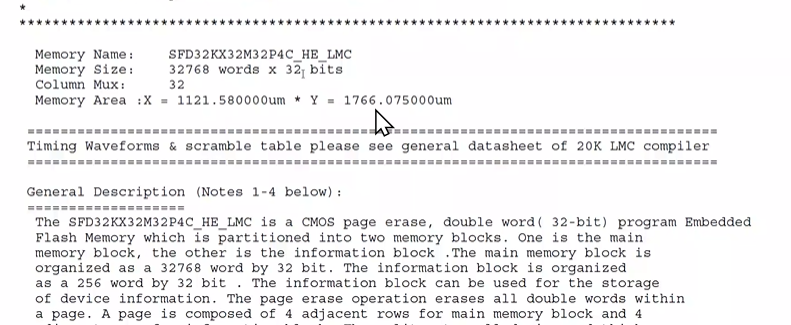

- 256k容量的eFlash--两块128kbyte的eFlash

- eFlash读写位宽需要匹配AHB总线的读写位宽,都是32bit,所以128kbyte的eFlash深度要达到32k,

- 128Kbyte = 32K * 32bit

- 每页有512byte,32 * 1024 * 4(32bit) / 512byte = 256Page

- 每页有4行,每行128byte

- double word = 32bit = 4byte = 每行有32个dw

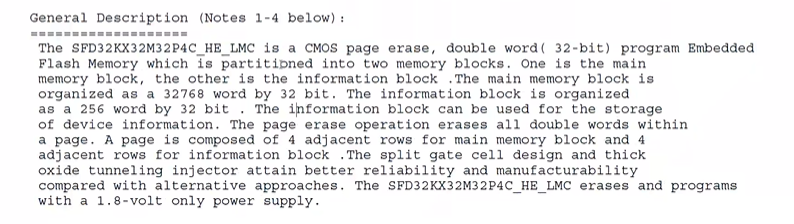

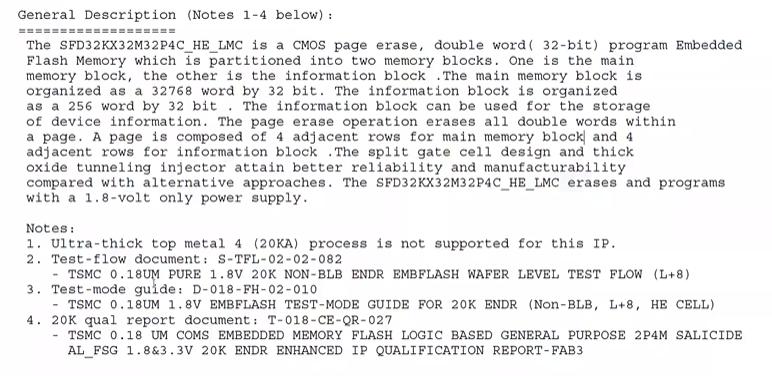

6. Flash Spec

- 版本号很重要,不同版本的时序和接口可能会有区别

- 面积大小,需要在版图中预留两块的空间

- 每块eFlash分为main memory,存储主要程序;information memory,存储器件的信息(空间多大,是哪个厂家的)。

- page的概念--一个page有4个row,每行128byte,擦除的时候是以page为单位的

- 如果时钟频率是200M--时钟周期5ns,需要5个cycle读到数据

- 进行读取操作的时间比进行写入程序的时间短得多,page擦除和mass擦除(整块擦除)时间慢;

- 读的延迟小,写的延迟比较大的时候,不能用于CPU这种对于数据访问(读写)的模块,但是可以用于进行程序读取的模块(只进行读,不进行写)

标签:

IC

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具