07-逻辑仿真工具VCS-Post processing with VCD+ files

逻辑仿真工具-VCS

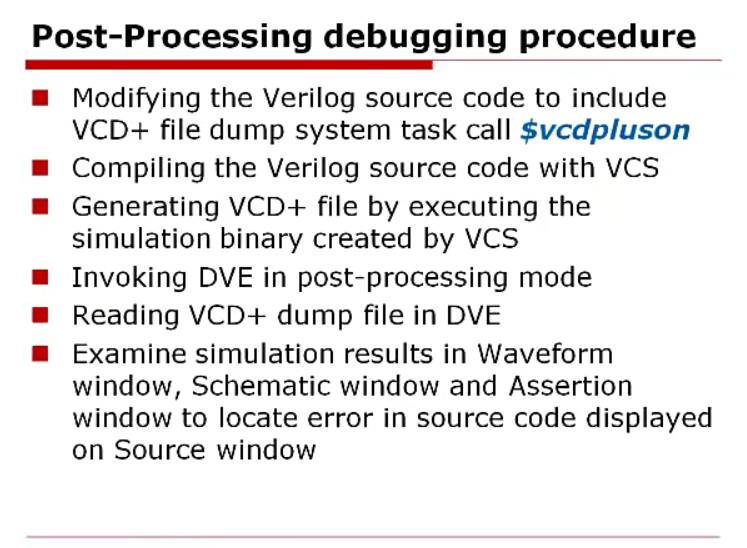

- 编译完成不会产生波形,仿真完成之后,生成波形文件,通过dve产看波形

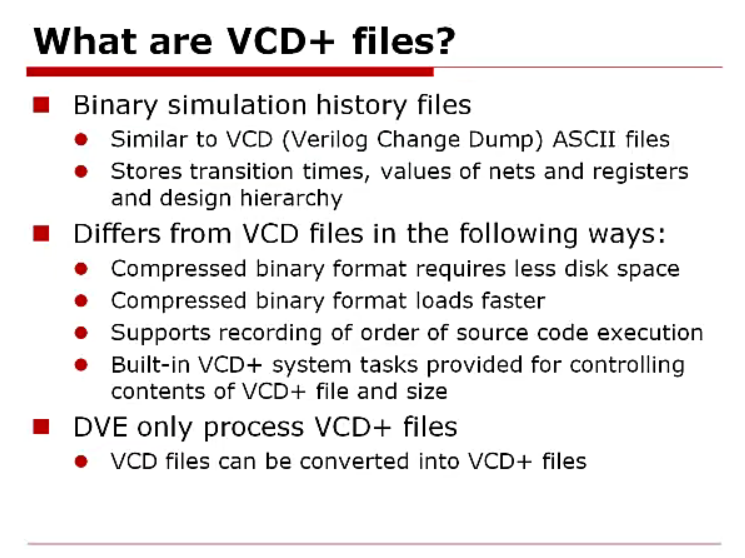

- vcd是波形文件的格式,但是所占的内存比较大,后面出现了vpd(VCD+)波形文件

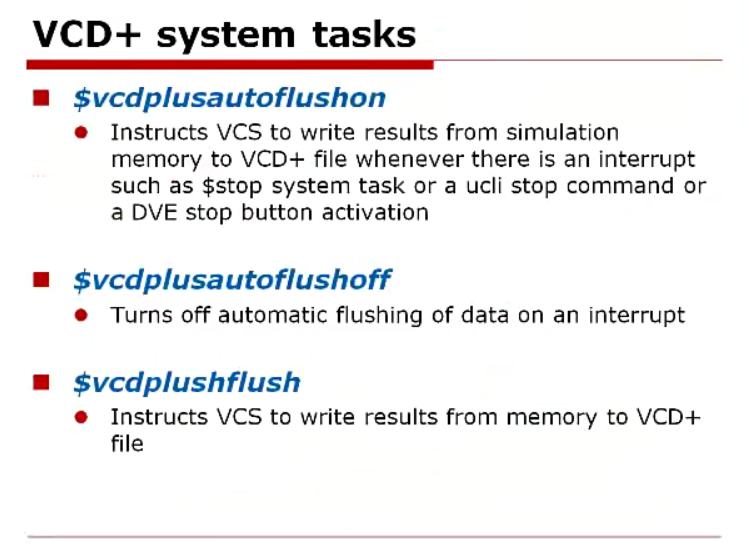

- 将一些系统函数嵌入到源代码中,VCS不会自动保存波形文件

- Dump波形,就是将仿真波形记录下来

1.后处理考虑的因素

- 在设计的初期或者验证平台搭建初期保存波形,随着项目进行就不会保存波形文件

2.什么时候进行post-processing

3.什么是VCD+

- DVE只支持VCD+文件,

4.波形产生函数

-

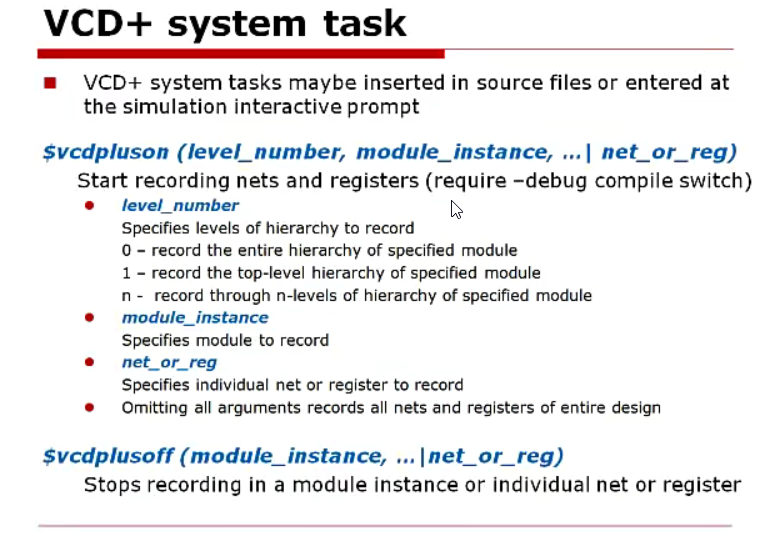

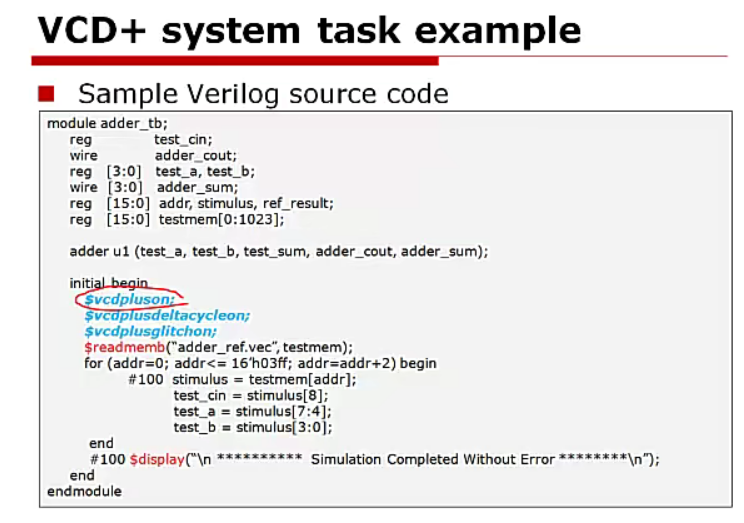

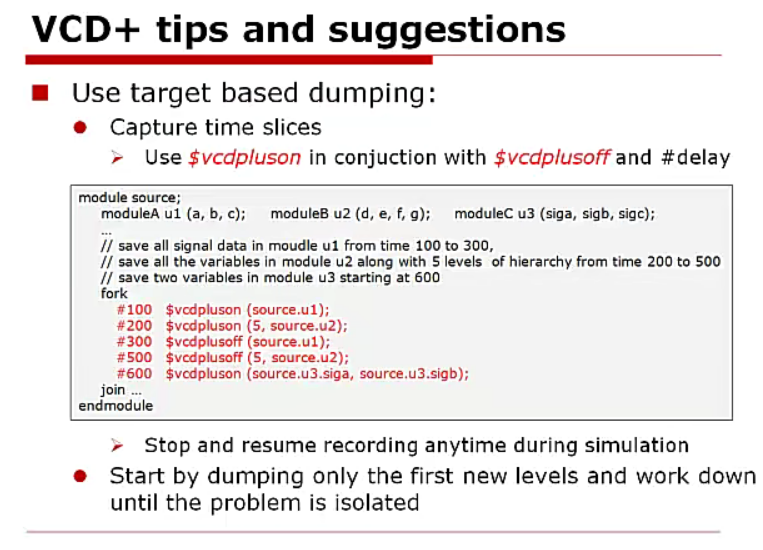

在verilog中代码,嵌入$vcdpluson()函数dump波形

-

不带参数,将所在的module波形以及包含的子模块的波形都保存

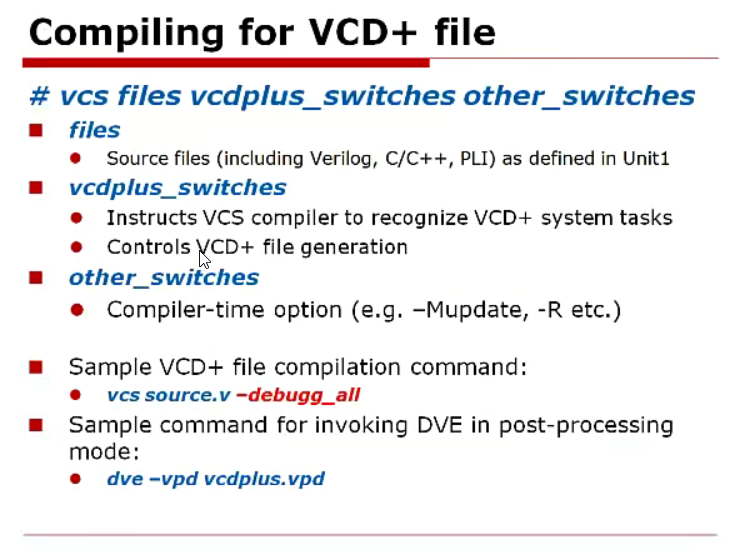

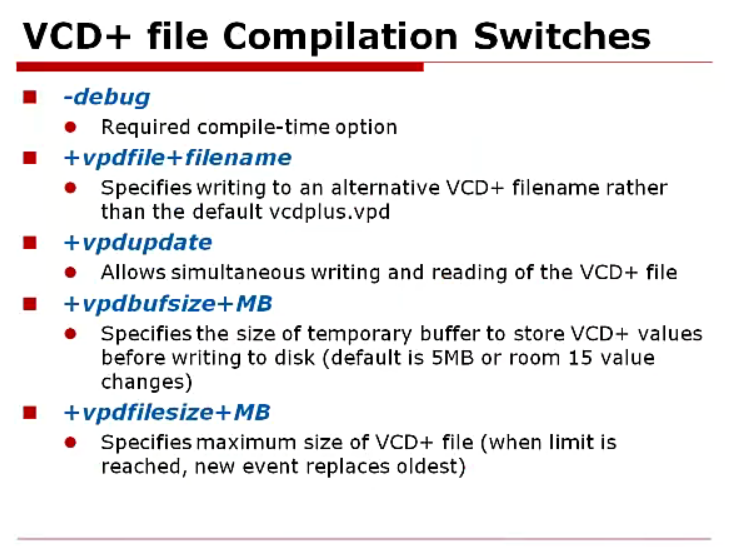

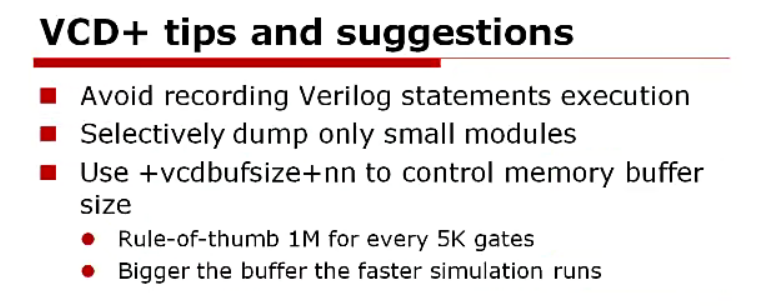

5.编译选项

- +vpdfile+filenames -- 重命名产生的波形文件

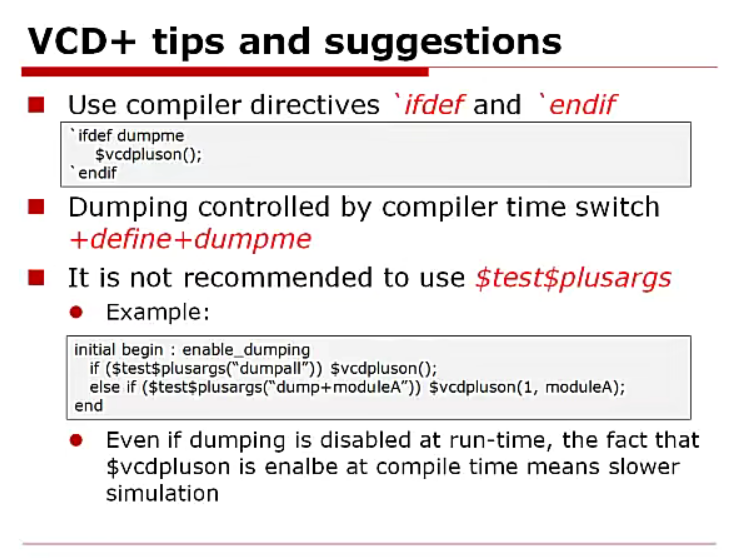

- `ifdef 条件编译

- $values$plusargs

6.使用Makefile进行VCS后处理

Makefile文件

# 产生的二进制可执行文件

OUTPUT = simv_fsm_moore

# 进行宏定义,用于条件编译

ALL_DEFINE = +define+DUMP_VPD

# vpd file name

VPD_NAME = +vpdfile+${OUTPUT}.vpd

# compile command

VCS = vcs -sverilog +v2k -timescale = 1ns/1ns

-debug_all

+vcs+flush+all

${ALL_DEFINE}

${VPD_NAME}

-o ${OUTPUT}

-l compile.log

# simulation command

SIM = ./${OUTPUT}

${VPD_NAME}

-l ${OUTPUT}.log

# start compile

com:

${VCS} -f file_list.f

# start simulation

sim:

${SIM}

#start clean

rm -rf ./csrc *.daidir ./csrc *.log *.vpd *.vdb simv* *.key *race.out*

file_list.f

-timescale = 1ns/1ns

// Macro define

// +define+INC_COUNTER

// Source file

./rtl/fsm_moore.v

//testbench

./tb/fsm_top.v

./tb/hello.c

- make clean -- 删除当前目录下产生的仿真文件

- make com -- 执行编译

- dve & -- 打开图形化界面-->file-->找到xx.vpd文件

- dve -vpd xxx.vpd & -- 打开图形化界面,并且将波形文件加载进去

// verilog

initial begin

`ifdef DUMP_ME

$vcdpluson(); // 不加参数,dump所有波形

$vcdpluson(1,fsm_top); //只记录top层的波形

`endif

end

- VCS默认是不会记录数组波形的

- 使用$vcdplusmemon(); dump数组的波形

dump数组的波形

// 在top层中定义了mem

reg [7:0] mem[0:15]

// 使用$readmemh()函数进行初始化

initial begin

$readmemh('./data/src.txt',mem); // 将src.txt文件内容加载到mem中

for(i = 0;i<16;i = i+1) begin

$display("mem[%2d]" = "%8h",i,mem[i]); // 打印数组的内容

end

end

src.txt内容

@0000

7

6

4

7

a

b

@0009

11

12

13

// 使用 $vcdplusmemon() dump数组的波形

initial begin

`ifdef DUMP_ME

$vcdplusmemon();

`endif

end

7.Skills

initial begin是并行的,执行顺序位置,可以通过宏确定执行语句的文件及行数

__FILE__,LINE- 执行仿真之后,由于有上面的宏,并且显示出文件路径以及执行的行数

initial begin

$display("Hello Verilog!",`__FILE__,`__LINE__)

end

initial begin

$display("Hello Verilog!",`__FILE__,`__LINE__)

end

initial begin

$display("Hello Verilog!",`__FILE__,`__LINE__)

end