06-逻辑仿真工具VCS-Debug

逻辑仿真工具VCS

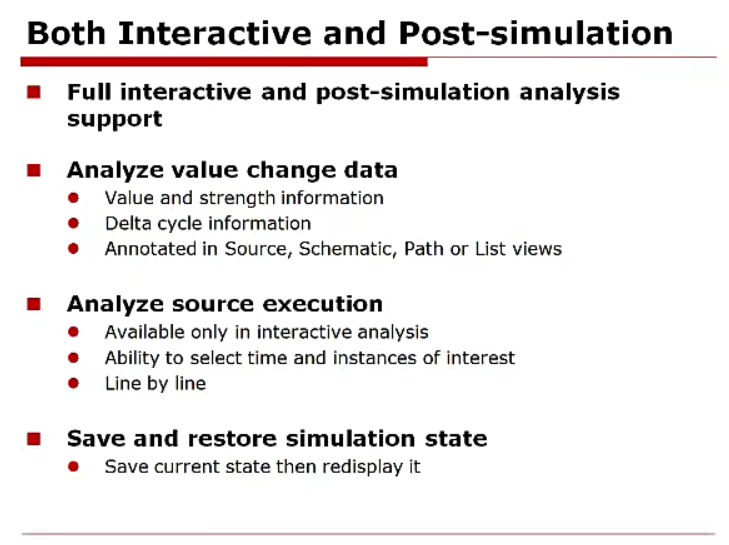

- verdi只进行debug进行使用,不进行编译,只进行产生波形之后的debug

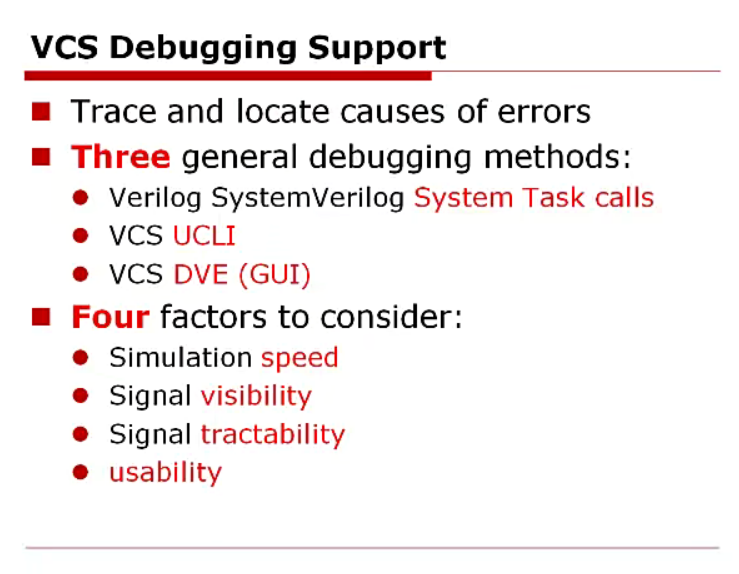

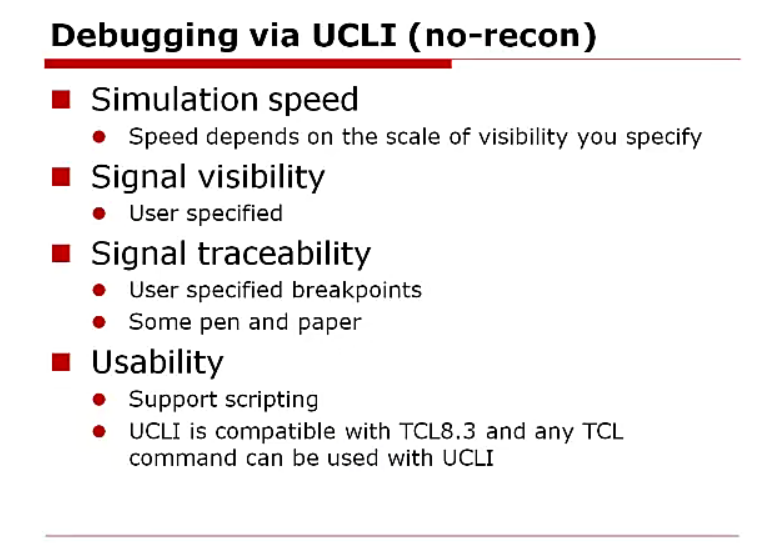

- 仿真速度和代码质量有关系,选项也会影响仿真速度,行为级>RTL>门级

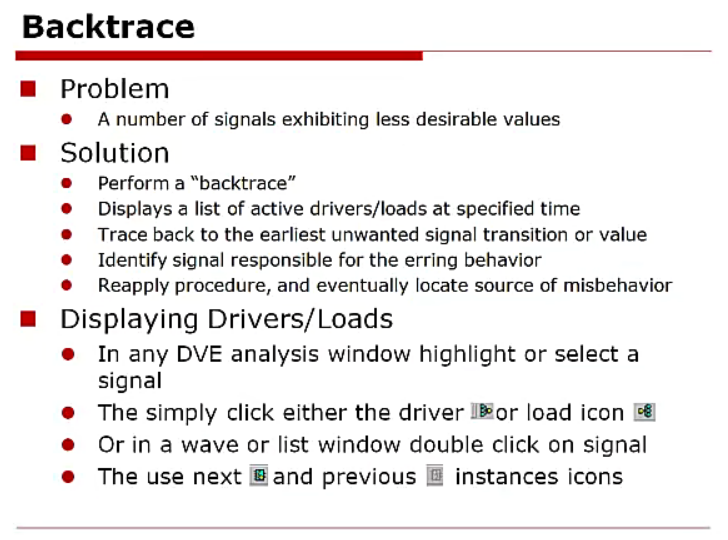

- 信号的可见性和可追踪性

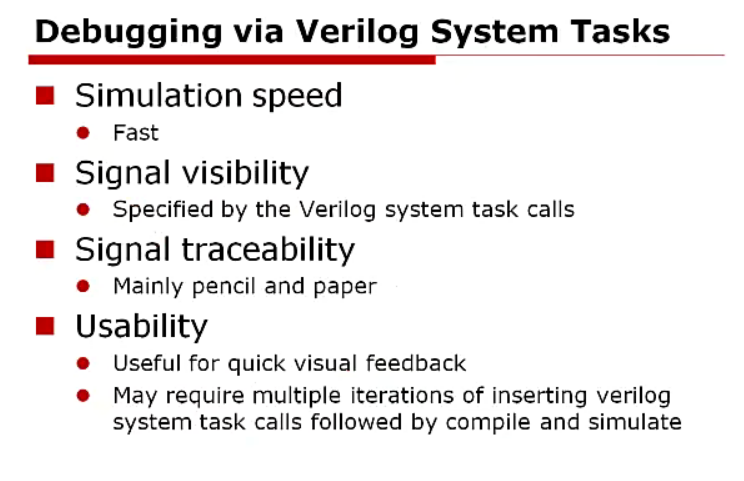

1.系统函数Debug

- display() -- 在active region;$monitor() -- 在monitor region执行

- $time -- 仿真时间(不是CPU时间)

- $readmemh()读取十六进制文件!

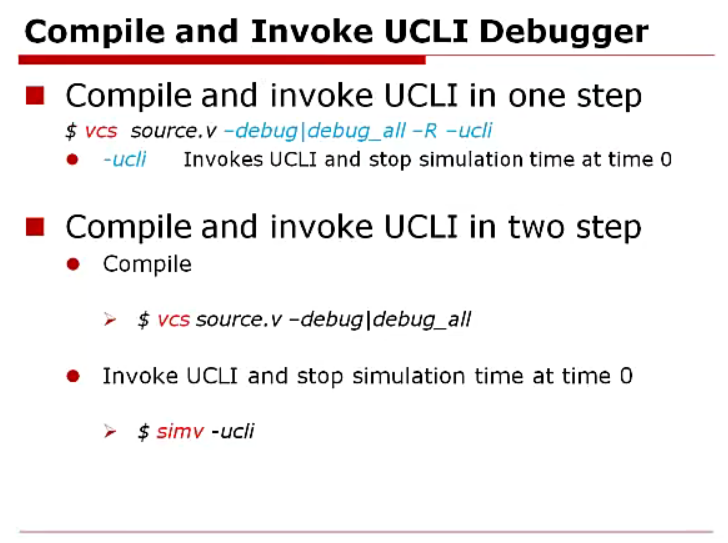

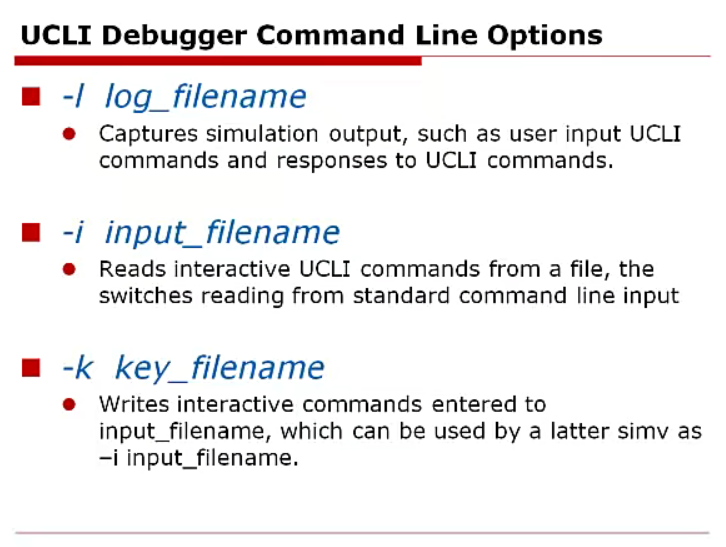

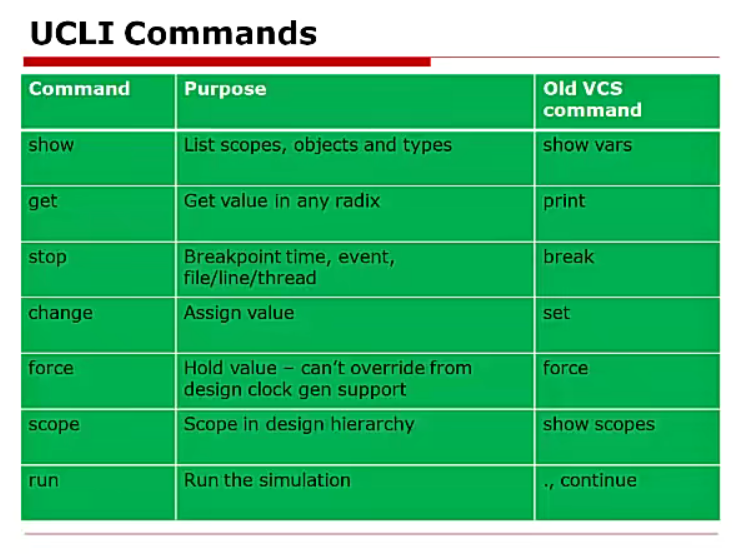

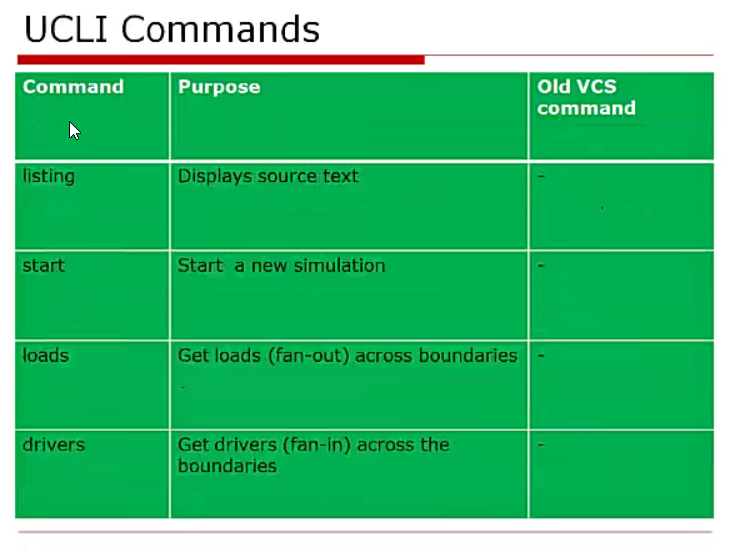

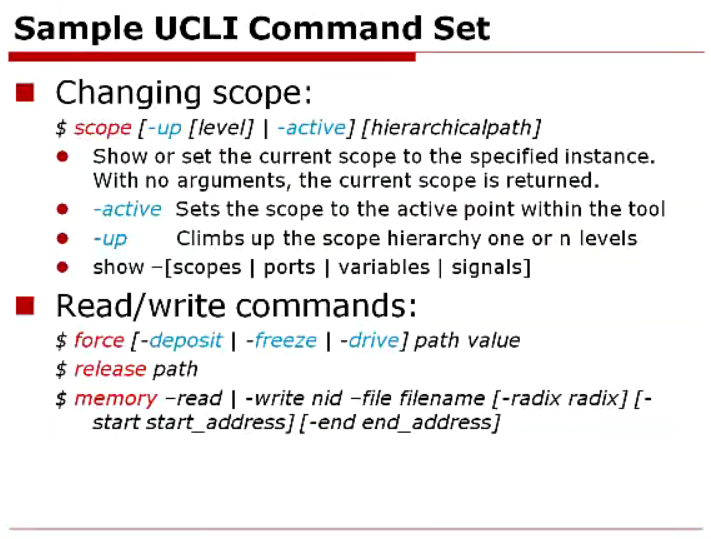

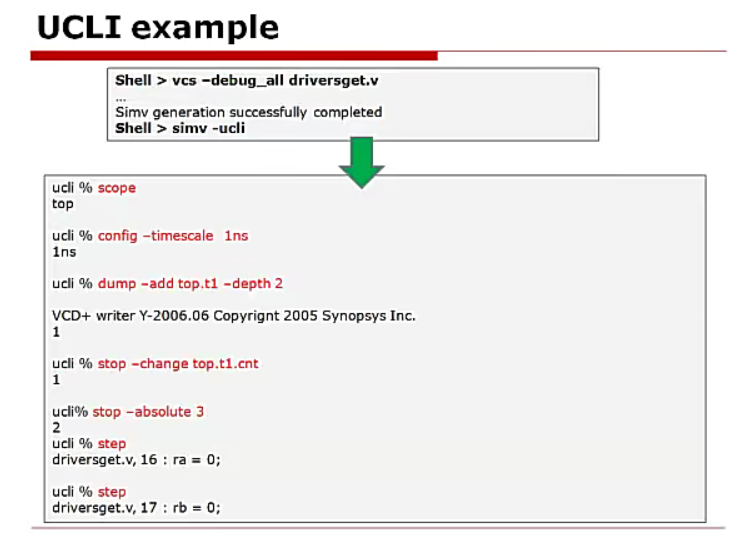

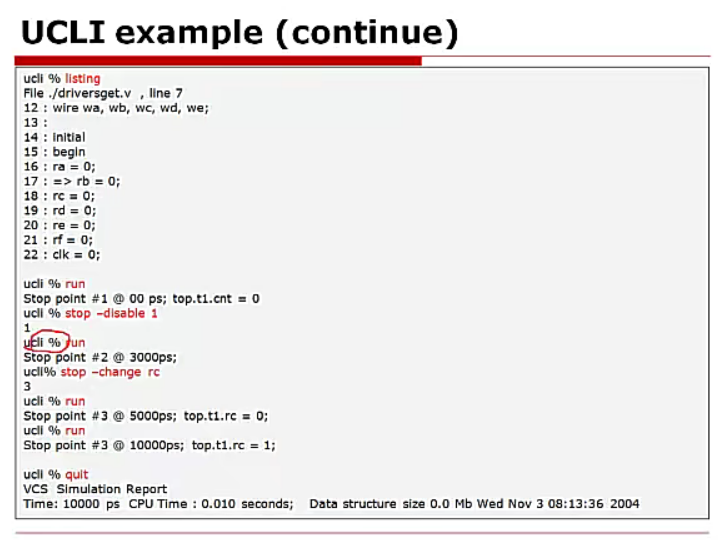

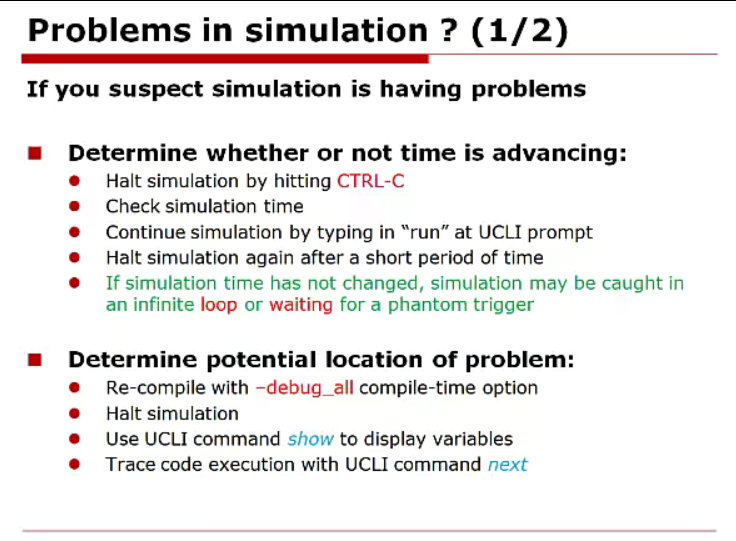

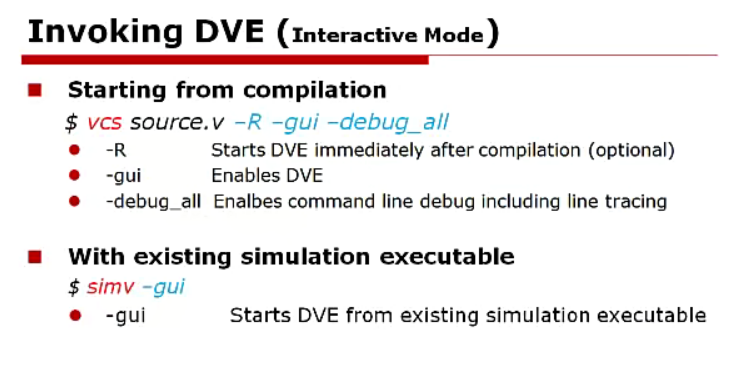

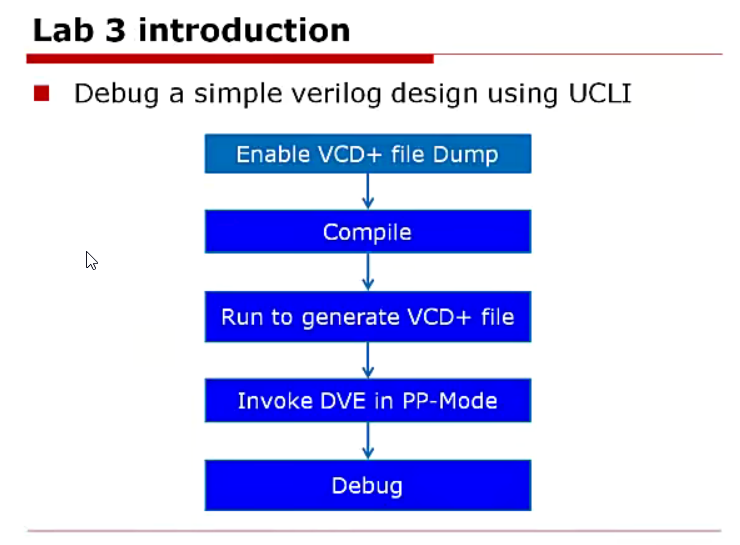

2.命令行Debug(基本不会使用)

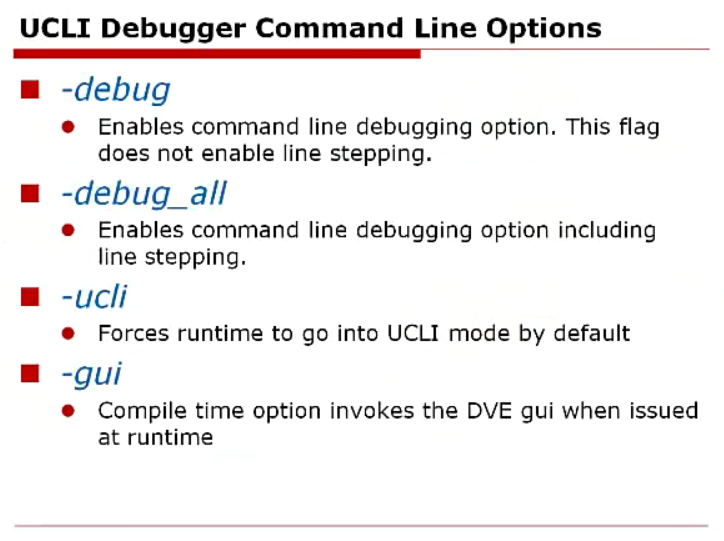

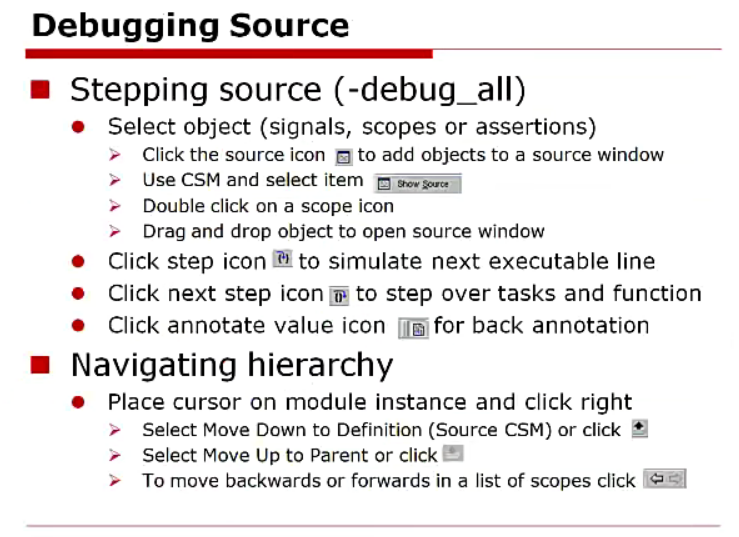

- -debug打开部分开关

- -debug_all打开全部开关

- -debug_pp在保证打开最多开关的情况下,对性能影响最小

- ctrl+c -- 仿真出现死循环卡住的时候

- 通过kill命令杀死进程

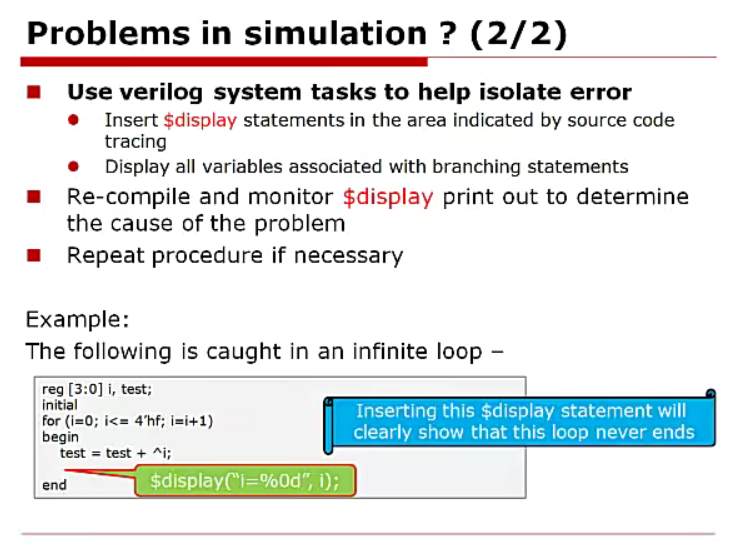

- 在循环的时候可以加上$display(),在死循环的时候知道仿真停在哪里

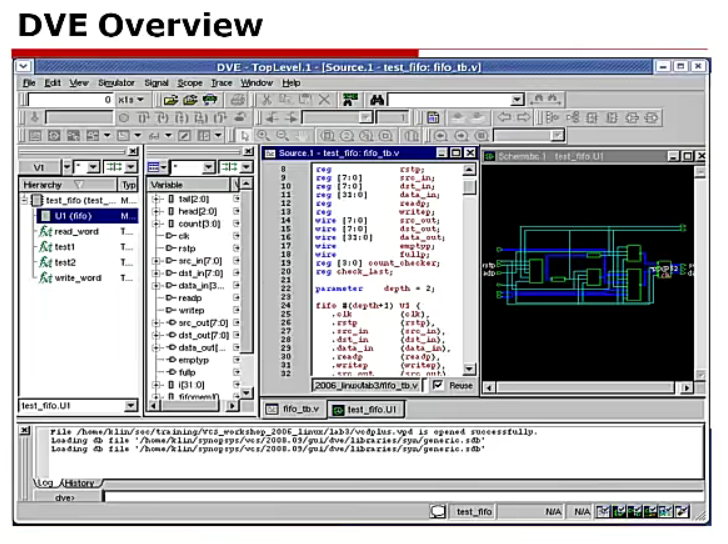

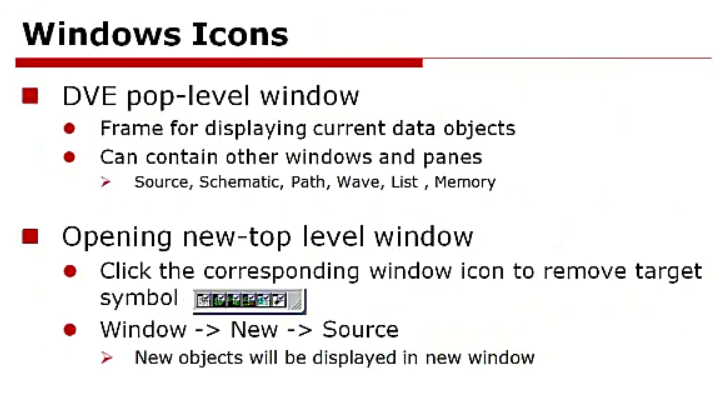

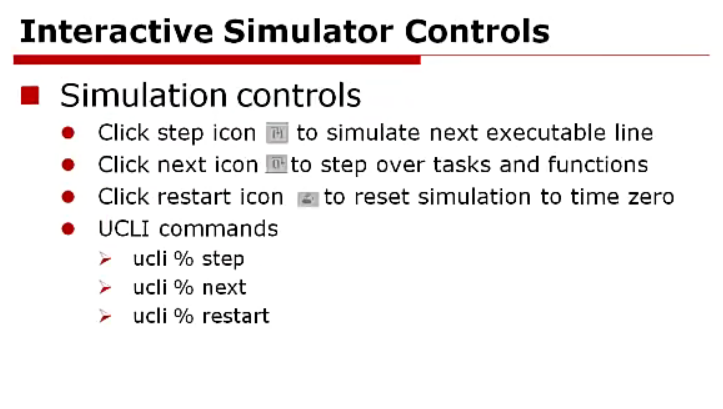

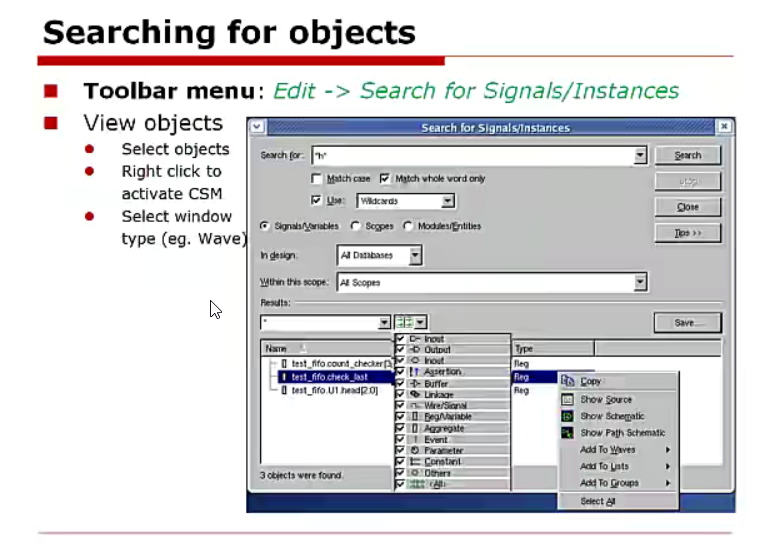

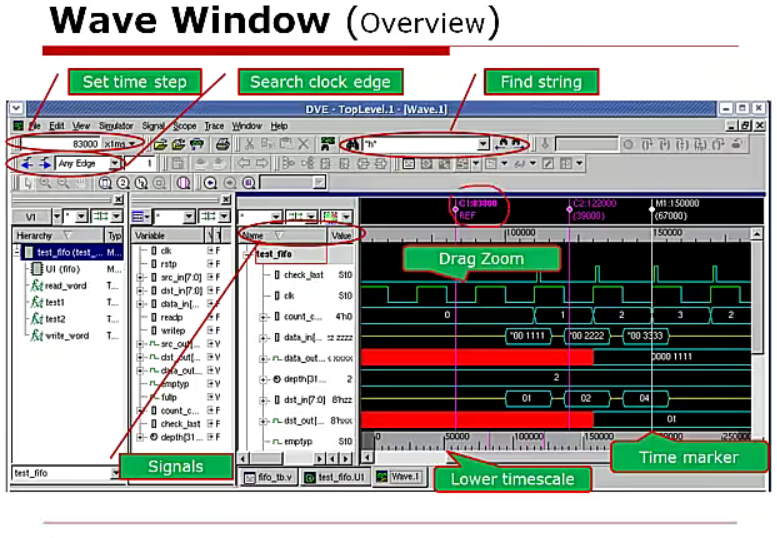

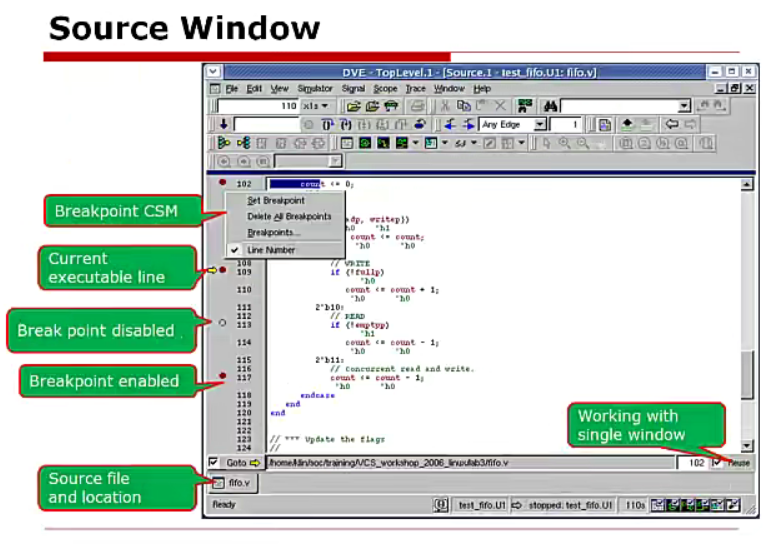

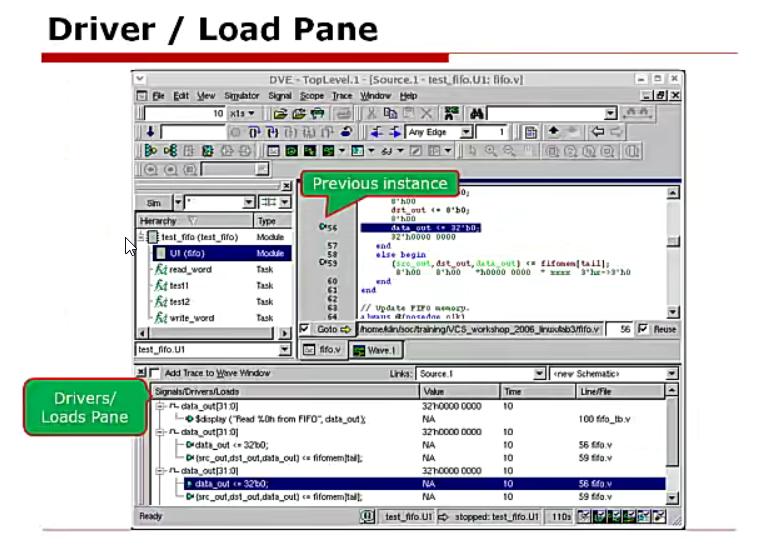

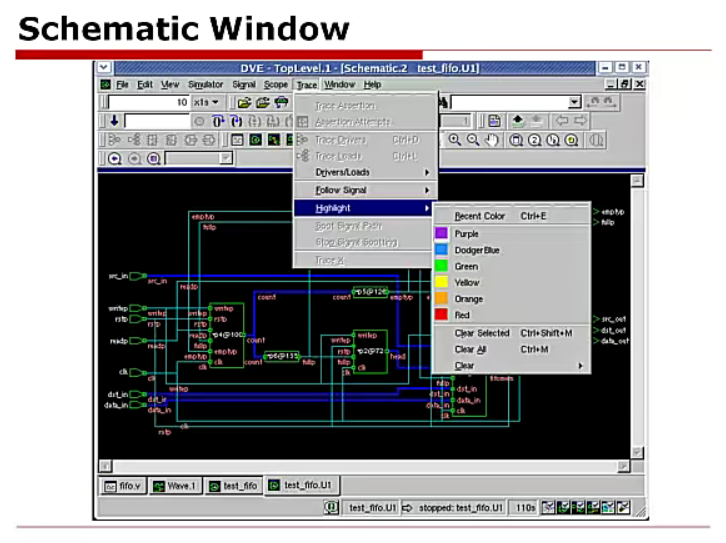

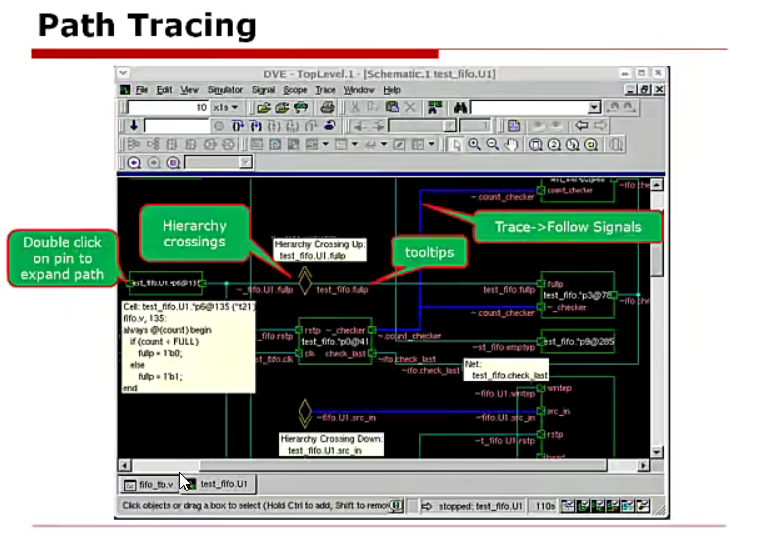

3.DVE Debug

- verdi使用的波形文件格式是fsdb

- # - 管理员权限;$ - 普通用户权限

- & 后台执行

- ctrl+o -- 打开波形文件

在Verilog中调用C语言程序

- 先写好C代码(.c文件)

#include <stdio.h>

// 调用dpi必须有的文件

#include "svdpi.h"

void hello(char*str){

printf("%s\n",str);

}

- 在verilog中调用

import "DPI" function void hello(string str); // 导入函数 返回值 函数名(参数)

initial begin

hello("Hello SystemVerilog");

end

- 编译的时候将c代码加入

vcs xx.v xxx.v xxx.c ...