基于AHB_BUS SRAM控制器的设计-02

AHB-SRAMC Design

片选信号决定哪几个memory被选择和功耗

- sram_addr和sram_wdata都是可以通过AHB总线的控制信号得到的

1. sram_csn信号理解

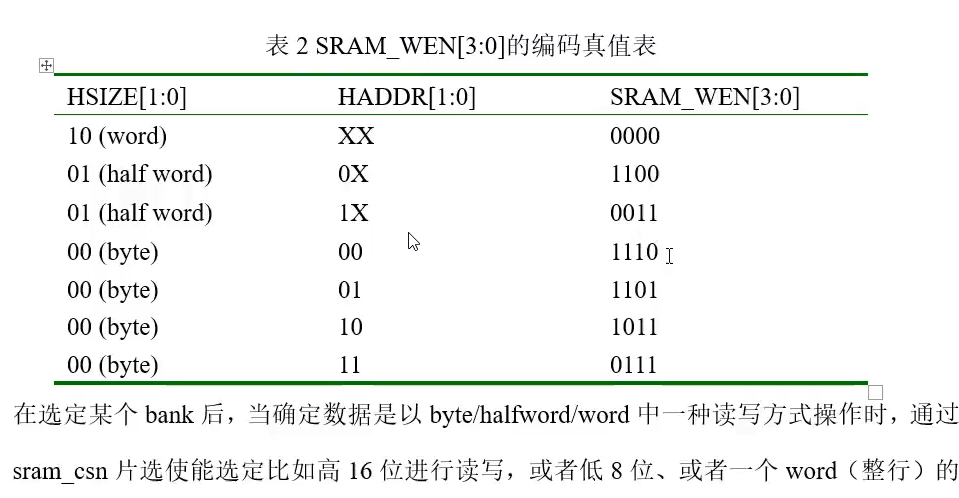

- hsize--表示当前传输的数据宽度,决定写的数据是多少位的

- halfword--传输的时候haddr受限于hsize,访问总线的时候haddr是和size对齐的,halfword是2byte为单位的,地址取值只能是0,2,4,6,8,10....(halfword -- 16bit -- 2个字节 -- 每两行存一个halfword)

- word-传输的时候,地址对齐4byte,0,4,8,12,16

- byte传输--访问地址addr是任意的

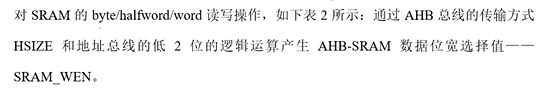

- word传输,haddr低两位是不用看的;halfword传输,低一位不用看,因为不会产生01,11的情况

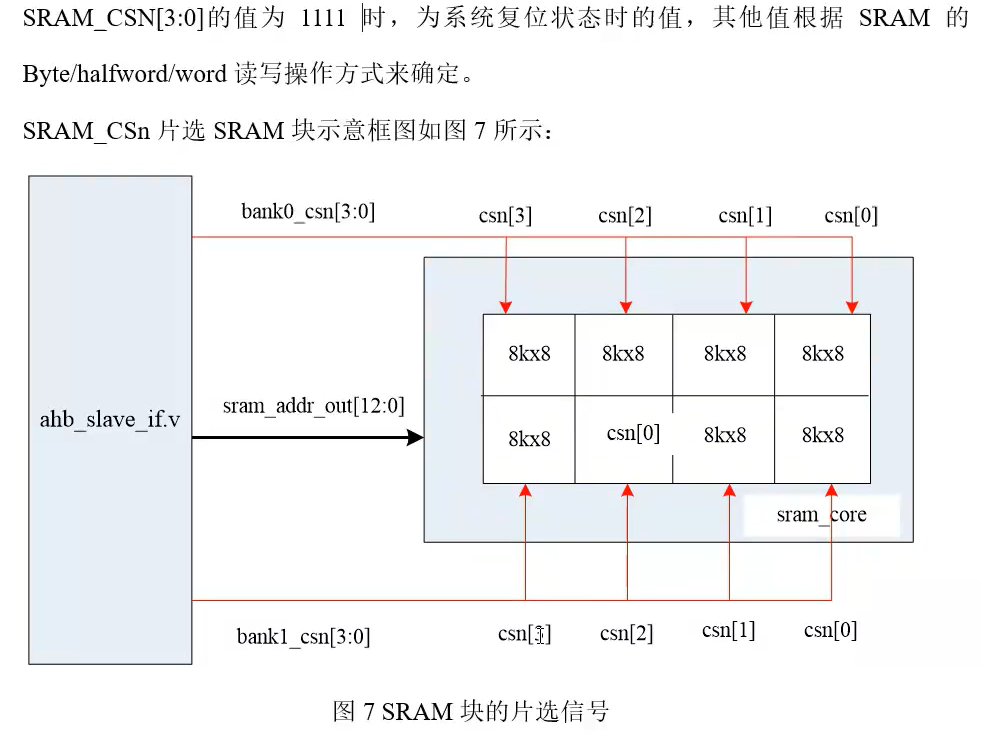

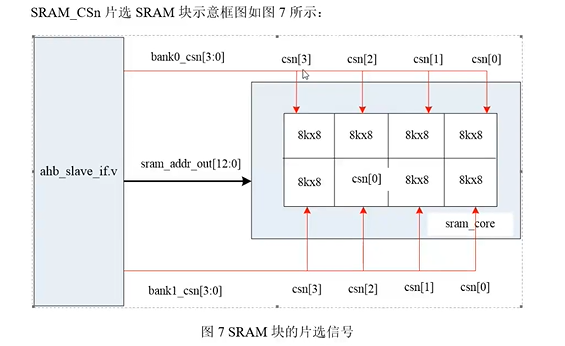

- sram_csn--0表示选中,1表示不选(使用的是独热码)

- sram_csn--是根据hsize和haddr产生的,是低电平有效的,0表示写,1表示读

2.bank选择及片选信号生成

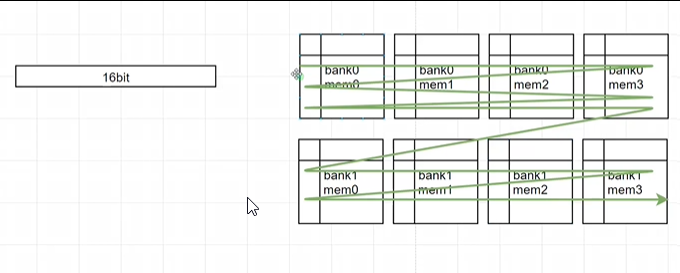

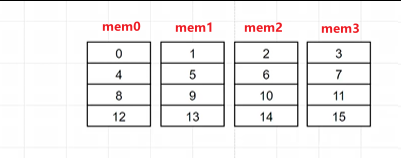

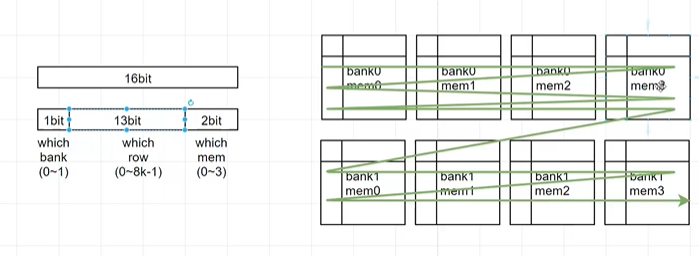

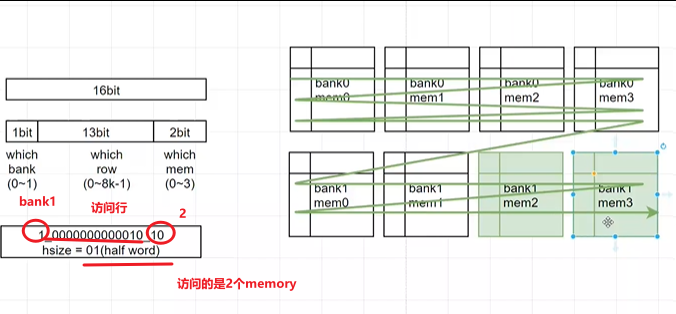

64k深度--需要16bit地址(2^16=65535),地址遍历的时候,是按照一行一行的方式进行寻址的,整体上走的是z字形

地址分配

- 采用低位地址交织的方式排布bank中的数据

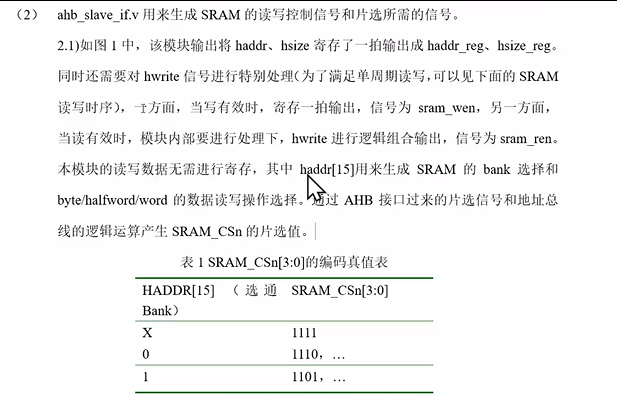

- 采用16bit地址的最高位,表示地址落在bank0还是bank1

- 采用16bit地址中的低两位,表示地址是memory中的哪一个

- 知道memory的容量,知道寻址的地址宽度,将地址宽度分为多个区间,不同区间表示选择哪个bank和哪个memory,这样就可以生成片选信号

- 上图中的信号都是根据十六位的地址得到的,根据地址最高位得到选择哪一个bank,根据hsize,选择读取和写入的mem

- 系统复位或者是没有任务的状态都是1111,四个memory都不选

总结

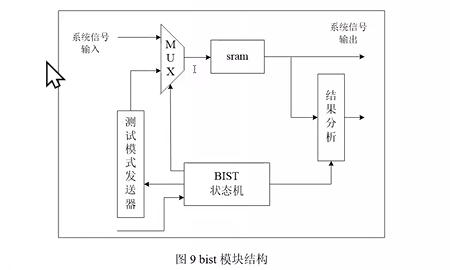

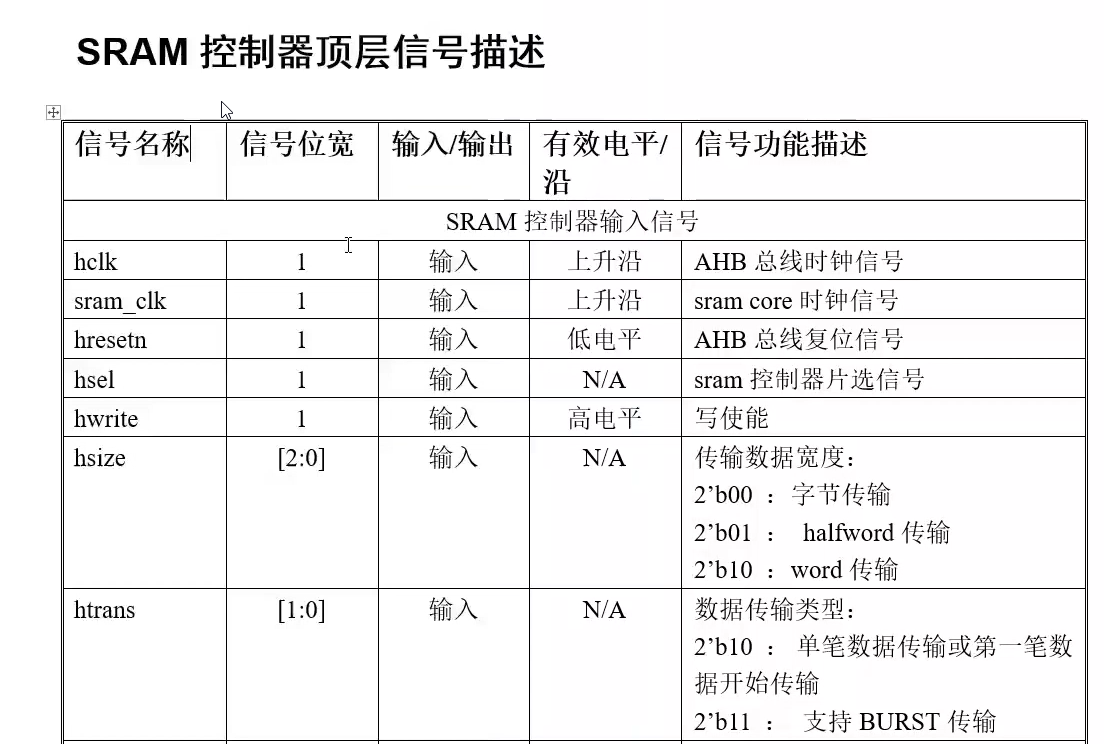

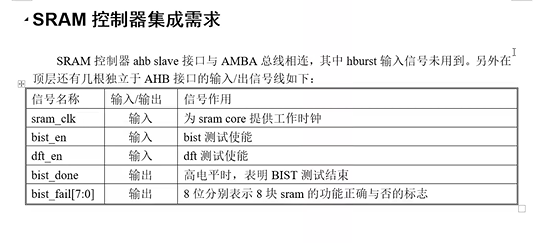

3.基于AHB总线的SRAM控制器功能集成需求文档

SRAM是集成在SoC中的,需要有一个文档告诉别人SRAM的接口

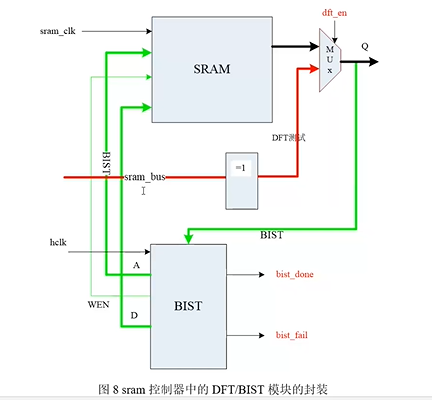

hclk和sram_clk是相反的关系

标签:

IC

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· ollama系列1:轻松3步本地部署deepseek,普通电脑可用

· 按钮权限的设计及实现

· 25岁的心里话