15-Verilog Coding Style

Verilog Coding Style

1.为什么需要Coding Style

- 可综合性 - 代码需要综合成网表,如果写了一些不可综合的代码,会出现错误

- 可读性,代码通常有多个版本,所以需要保证代码的可读性

- 保证代码质量,方便后续的综合以及后端的布局布线

2.头文件

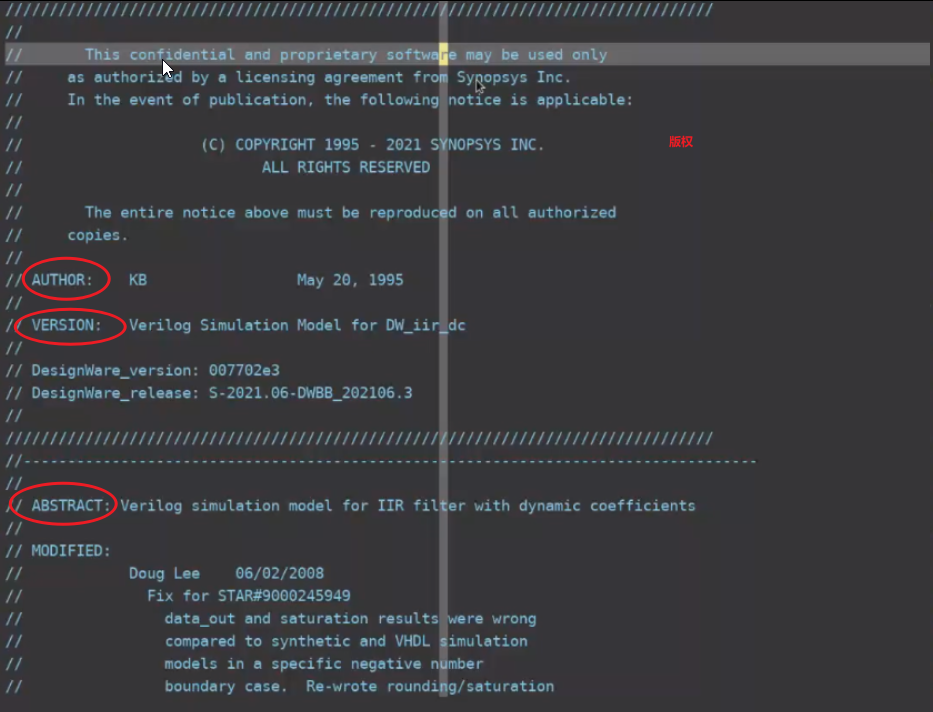

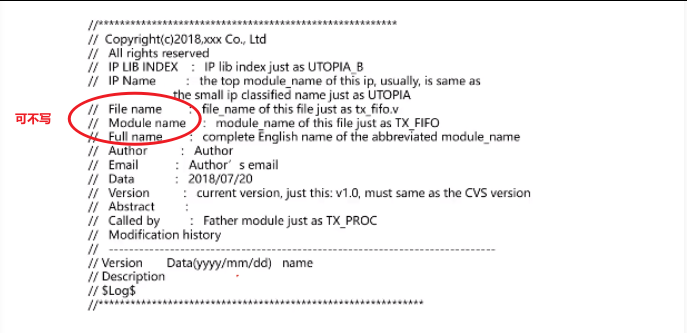

使用统一的文件头,其中包括:

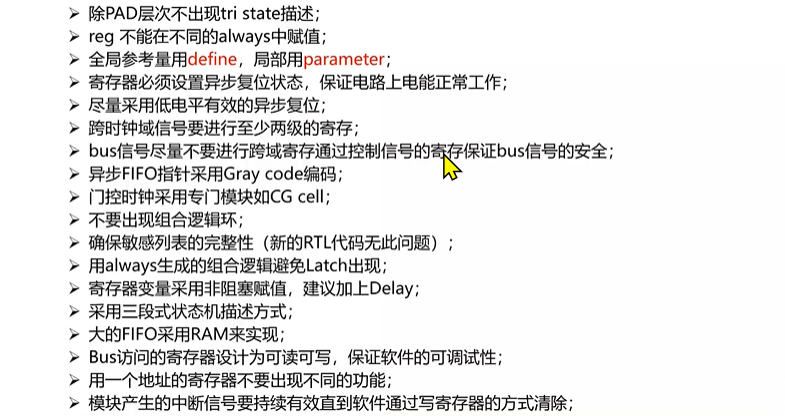

- 作者名

- 模块名

- 创建日期

- 功能概要(功能列表,mode 1... 2... 3...)

- 更改记录(通常在initial阶段和stable阶段之间更改代码,更改feature需要记录,修改bug不需要进行记录)

代码有三个版本,initial版本代码只需要跑完少数用例-->后端进行预综合-->进行迭代代码;stable(代码验证比价充分)-->过了95%的测试用例;final版本代码,完成100%的测试用例,此时不可修改RTL,如果需要更改走ECO流程 - 版权等必要信息

- 不同公司有自己的代码风格

3.module整体结构

- 统一的module结构便于项目成员的理解与维护

module module_name(

parameter xxx = xxx,

)(

input [xxx:xxx] reg/wire/logic variable_name,

....

);

// Define Parameter

// instance module

// ...............

//**********************************************

// main code

// ...............

endmodule

- 使用*进行分割区域

4.排版

- 缩进

- Input,output,reg,wire 0缩进

- always,task,function 0缩进

- 输入输出信号的宽度定义与关键字之间,信号名与宽度之间要用空格分开;所有宽度定义对所有信号名对齐

- 每个信号,变量和端口类型的声明占用单独的一行

5.命名风格

简洁\清晰\有效是基本的信号命名规则

- 端口,信号,变量名的所有字母都小写;函数名,宏定义,参数定义用大写

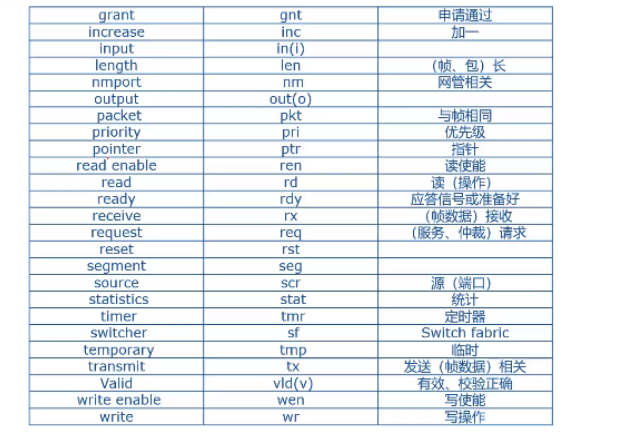

- 使用简称,缩略

- 基于含义命名(避免以数字命名的简单做法),含义可以分段(最多分三段),每一小段之间使用"_"进行分隔,如tx_data_val

- 命名长度一般限制在20个字符以内

- 低电平有效,加后缀"_n",比图rst_n

- 无条件寄存的寄存信号在原信号上加ff1,ff2.....如原信号data_in,寄存一拍data_in_ff1,寄存两拍data_in_ff2

- 不能用"_reg"作为最后的后缀名,因为综合工具会给寄存器自动加上_reg,如果命名中使用"_reg"作为后缀名则扰乱了网表的可读性

6.表达式书写

-

适当使用()

如果一个表达式的分组情况不是很明显,加上括号有助于理解,提高代码的可读性

-

赋值语句

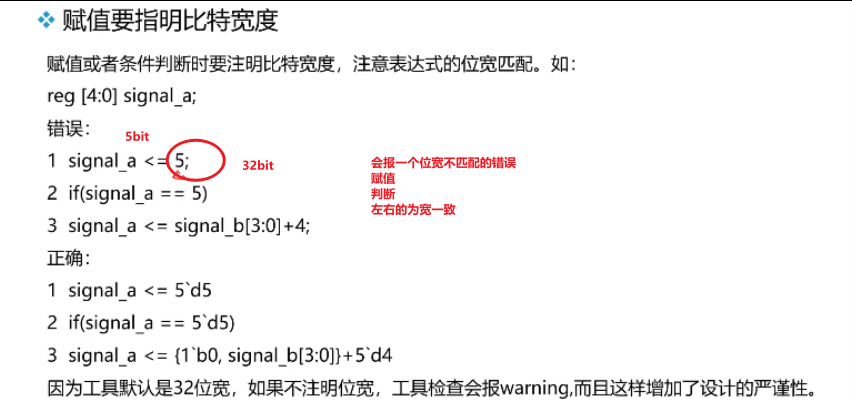

- 书写变量的时候习惯性加上位宽

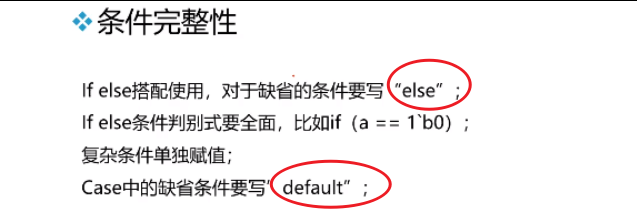

- 条件完整性

- 写条件语句的时候不要忘记写else和case语句中的default

- 如果赋值语句比较复杂,注意条件的拆分

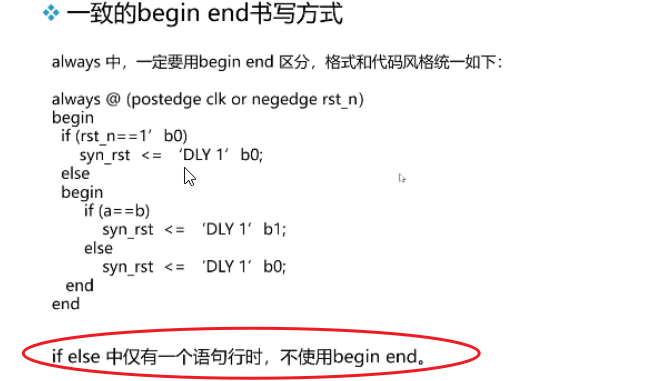

- 条件结构书写

- if-else语句具有优先级,会被综合成多级mux

- case语句的条件没有优先级,会被综合为平行的mux

-

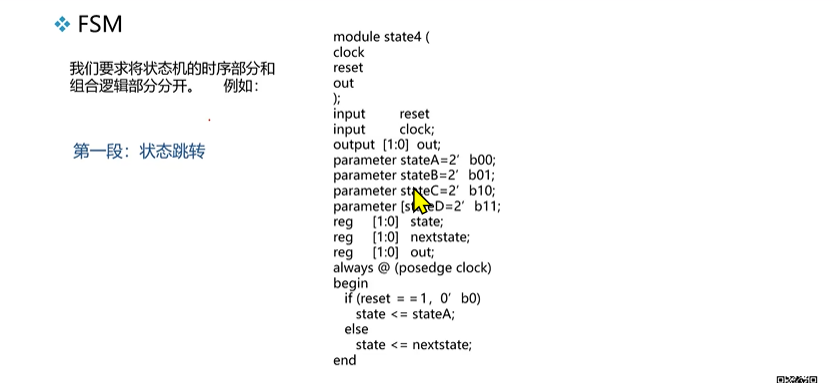

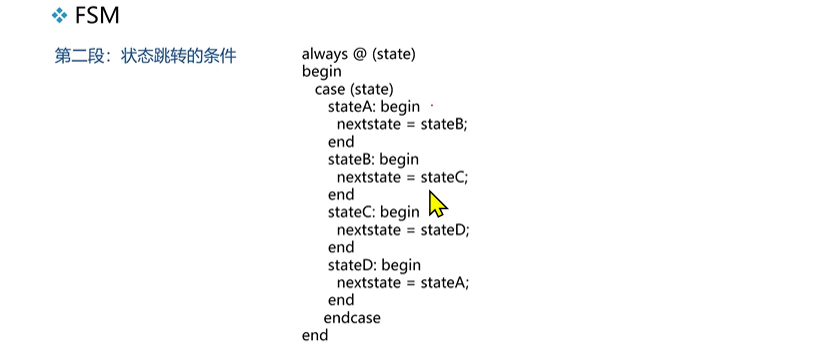

状态机的书写

-

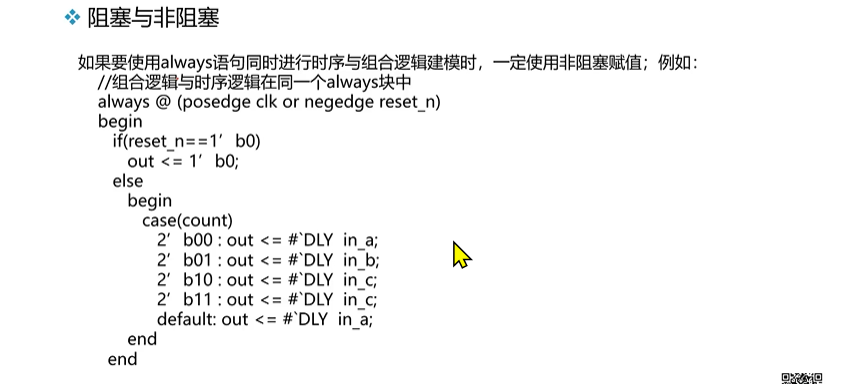

阻塞赋值和非阻塞赋值

-

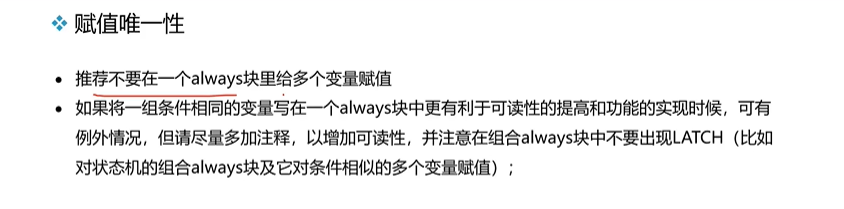

赋值唯一性

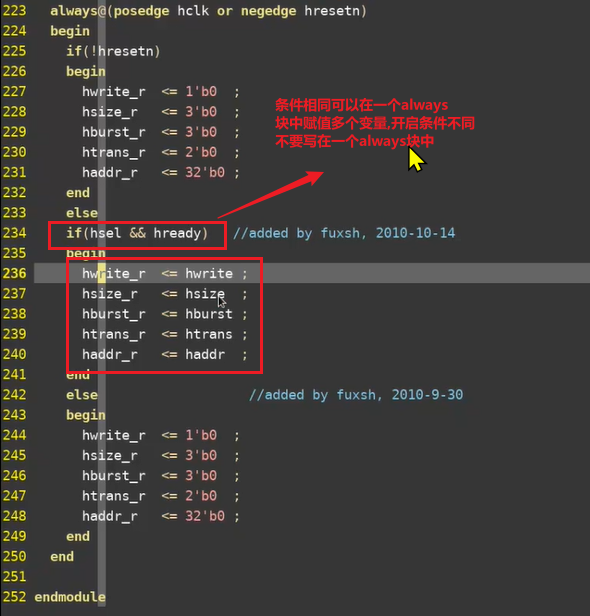

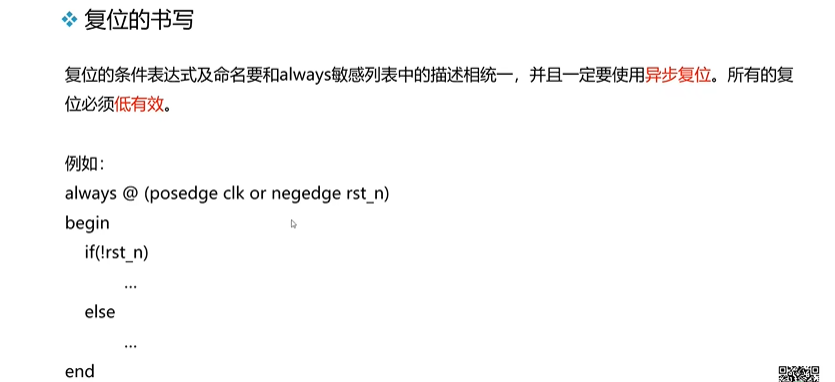

- 条件相同的语句写在一个always块中,条件不同写在不同的always块中

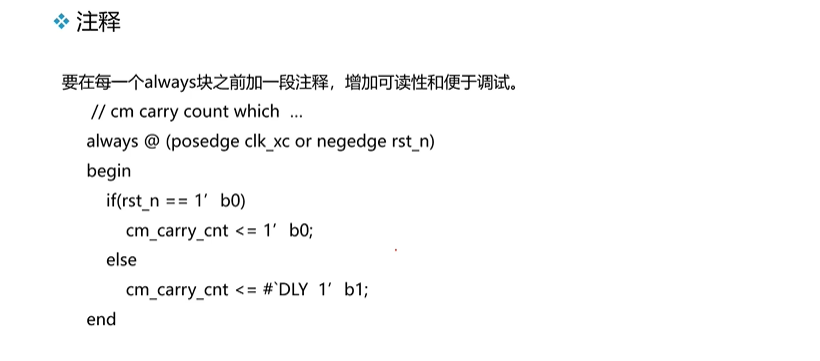

- 注释书写

7.可重用设计

8.设计规则