基于AHB_BUS SRAM控制器的设计-01

基于AHB Bus SRAM控制器的设计

1.课程目标

- 接到一个需求要设计SRAM或者I-cache等,需要问后端要一个Memory

- Memory Compiler是由后端工程师完成的,Memory Compiler类似于DesignWare进行配置(输入参数,输出需要的SRAM)

- 文档体系非常重要,需求文档\架构文档\微架构文档\Design Spec

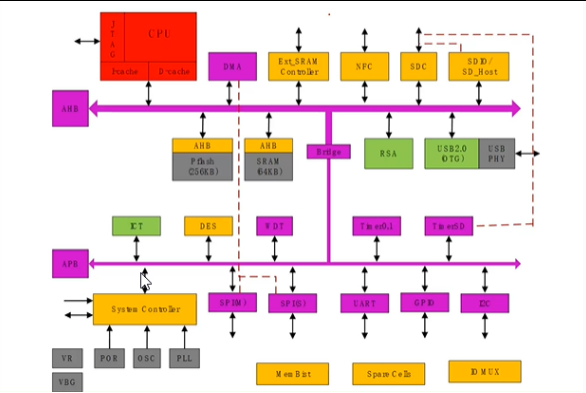

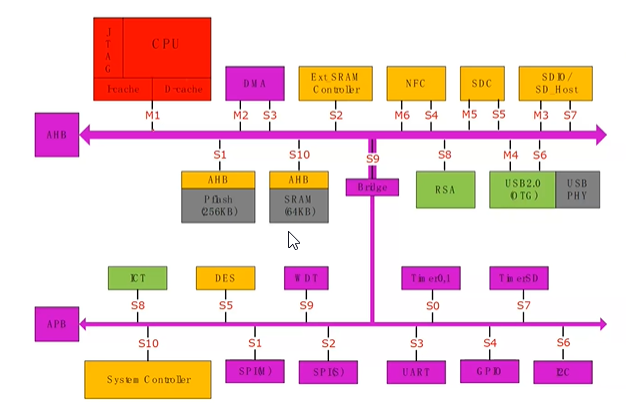

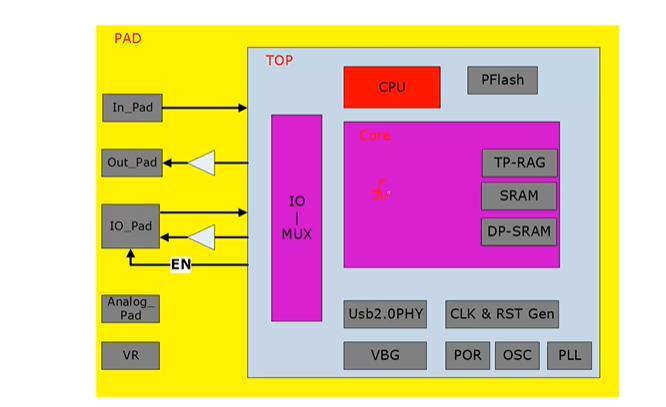

2.AHB-SoC芯片架构图

- CPU负责SoC的调度,CPU赋予SoC可编程的特点,CPU是执行程序的(程序员)

- DW IP(DesignWare IP)是非常通用的IP(输入参数,可以得到相应的IP),功能简单,UART,GPIO,I2C.....可能是购买IP送的

- My IP就是自研IP,Ext_SRAM controller逻辑复杂一些

- PFlash是非易失的,SRAM是易失的

- Soft IP提供的是RTL代码,需要自己进行综合,然后进行后端设计

- Hard IP固核

- IO MUX就是进行引脚的复用

- Mem Bist是后端的内容,进行内建自测试

- APB总线上只有一个master就是Bridge,其他模块全部都是slave

- System Controller也是slave,其中有一些寄存器,需要控制时钟开启和关断需要slave接口

- CPU是一个master

- DMA既是Master又是slave,DMA需要有两个master接口,一个用来读,一个用来写;DMA需要有slave接口,CPU通过slave接口配置其中的寄存器

- SD Host需要使用slave接口进行配置,知道当前工作在哪种工作模式下;需要master,如果从外部数据暂时存储到FiFo中,通过SD Host将FiFo中的数据,存储到内部的SRAM中

- MemBist模块进行内建子测试,会产生测试信号进行测试

- Boot:上电之后,系统有些组件需要进行配置(初始化)才能使用,这个过程就是boot

- 中断程序:module发送中断给CPU,CPU通过中断处理程序处理中断

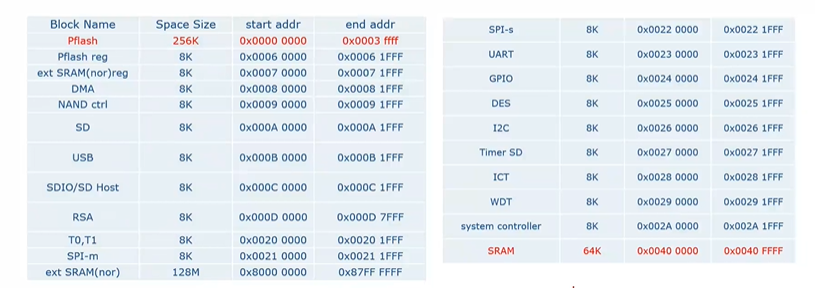

3.各个功能模块的地址空间

4.AHB-SoC芯片架构图

4.1 PAD

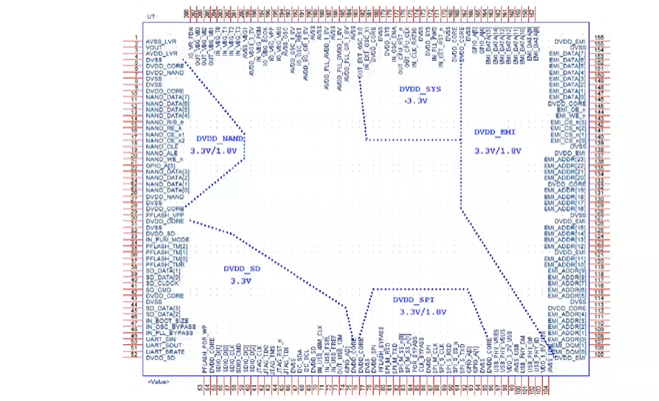

4.2 Power & Pin

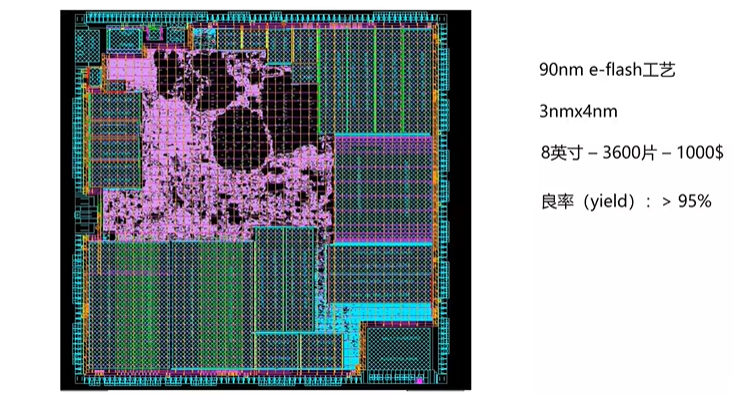

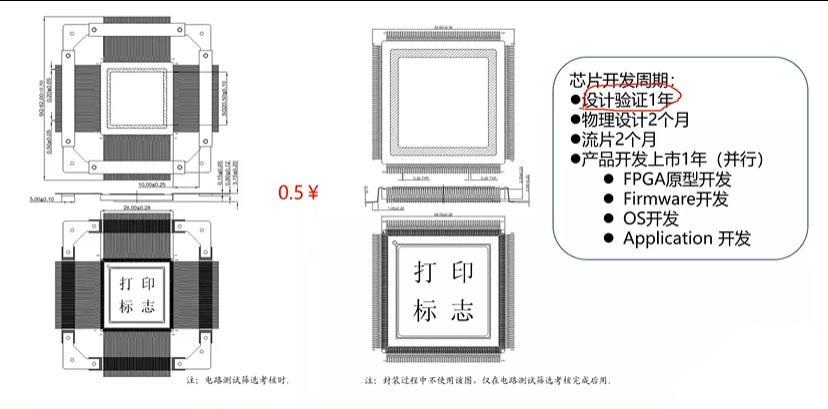

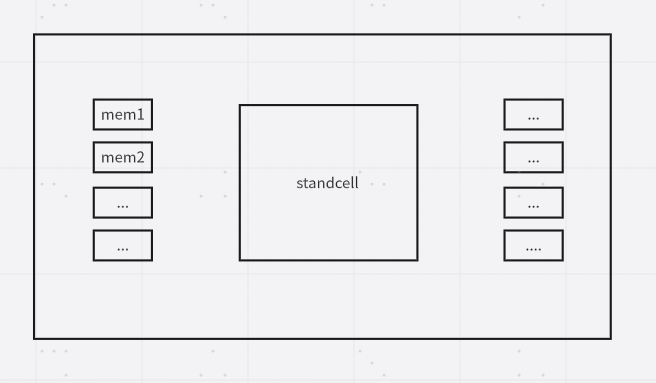

4.3 Layout

- 周边类似砖块的是固核,摆放位置影响时序;memory通常摆在四周

4.4 Package

5.AHB-SRAM控制器的系统设计需求

- 需求(市场\算法\产品)-->架构(架构师)-->拆解module

- SRAM作为系统的缓存,CPU的I-cache(接口)和D-cache需要通过总线访问存储体,比如需要通过总线访问指令的存储体,所以在SoC中需要有一个地方存储代码和运算的数据,数据量少,可以存储在寄存器中,如果数据量多可以存储在memory中

- SRAM是由Memory Controller生成的,不需要由自己完成,我们需要完成的是SRAM控制器,控制SRAM的读写

- SRAM作为AHB Slave的形式存在

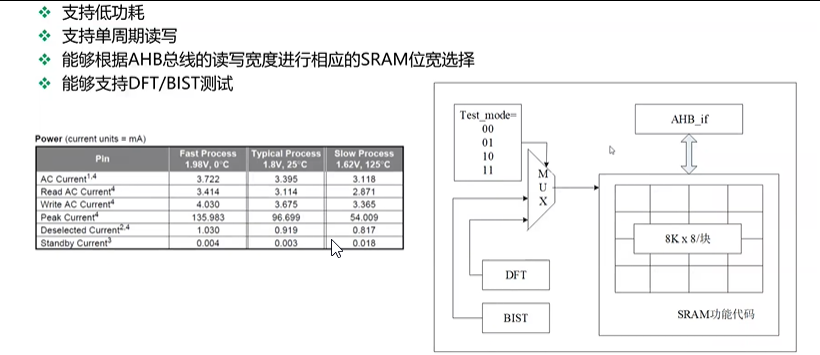

5.1 特性

- CPU中的一些load&store,就是数据的加载和存储,有三种形式byte,halfword,word

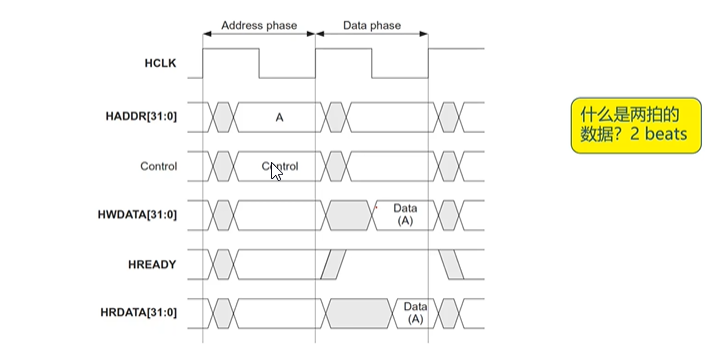

- SRAM单周期读写,体现在总线上,AHB有延迟访问的特性,SRAM在T0时候读取SRAM,在T1的时候就将数据返回,这样总线的利用效率高,缺点是系统的时序不太好

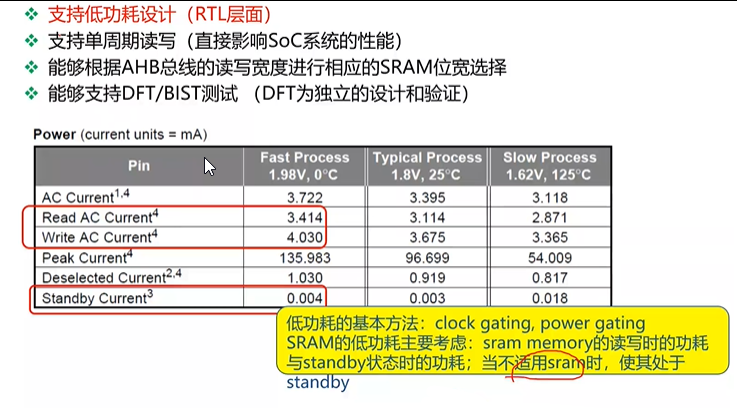

- 低功耗设计,经常使用clock gating,power gating,在开启寄存器的时候加使能信号控制

- SRAM的低功耗主要考虑:sram memory的读写时的功耗与standby状态时的功耗,当不使用sram时,使其处于standby

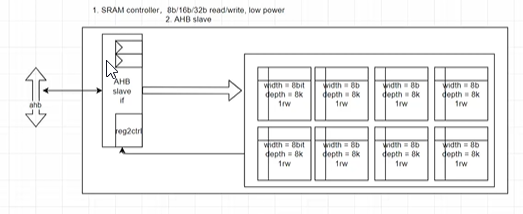

5.2 思路整理

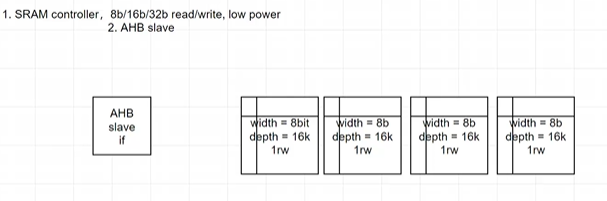

-

首先是一个AHB slave-->需要AHB_Slave_Interface

-

需要SRAM,将SRAM划分为很多个bank,根据架构中的SRAM是64kbyte的,所以,每个bank的width = 8bit,depth = 16k

-

每个memory在一个时钟内,只需要进行读或写操作即可

-

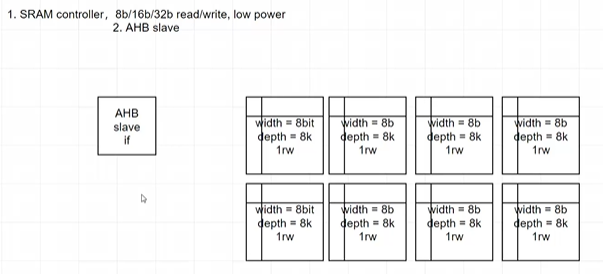

将memory的初步规格反馈给后端,如果后端人员返回信息延迟交大或者depth太大,生成不了;或许会将每个bank进行拆分,深度变为8k

-

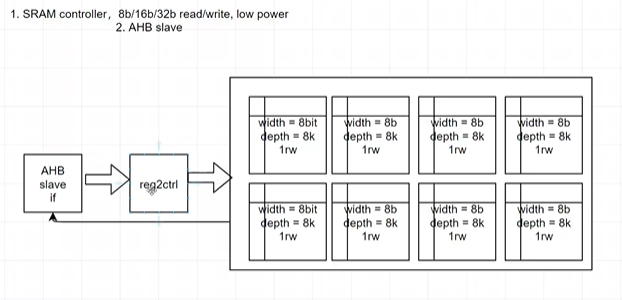

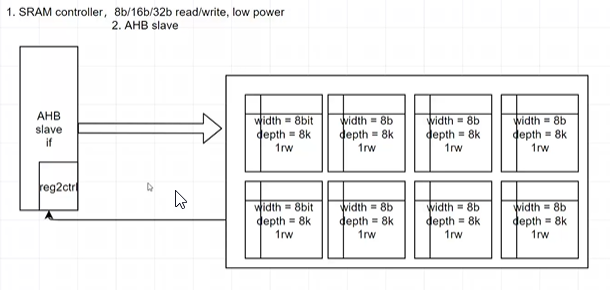

现在可以将AHB的的读写时序转换为SRAM的控制信号,可以单独设置一个模块,可以将AHB的配置信息转换为对于memory的控制信息

-

可以将reg2ctrl集成到AHB_Slave_Interface中

-

AHB_Slave_Interface中也有一些寄存器,需要进行配置一些状态,通过接口模块与AHB总线进行交互

Note:memory并不是划分的越小越好,memory划分的越小,面效比越差,实现总的SRAM占的面积越大

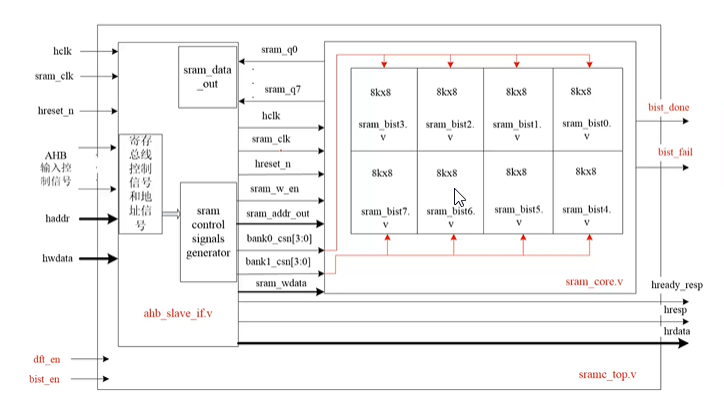

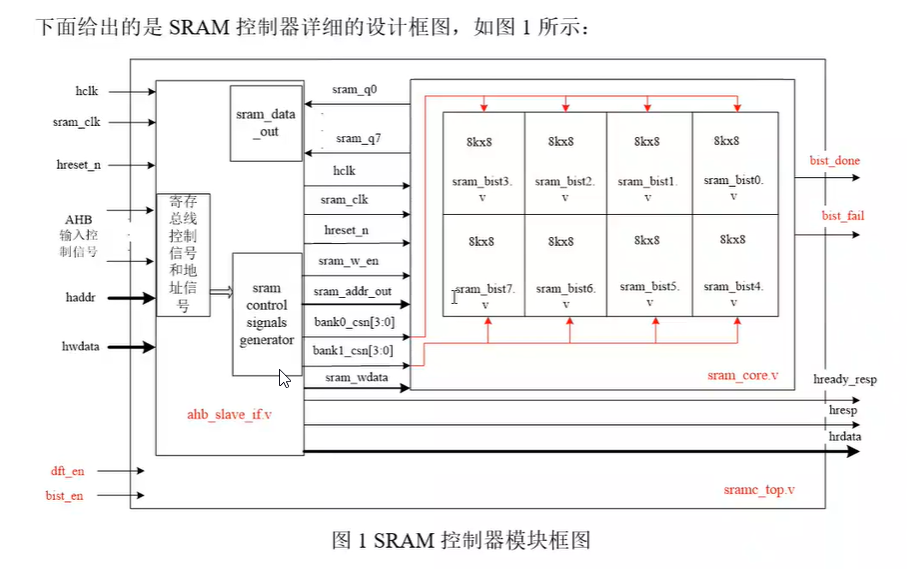

- 寄存总线控制信号和地址信号,ahb的信号需要进行打拍处理

- sram control signals generator -- 产生sram控制信号

- sram_data_out--sram中输出数据的集合(8片mem)

- 8k是深度,8是宽度

SRAM协议相关的接口

5.3 SRAM存储体生成

- Memory compiler -- 输入规格(深度\宽度\主频等参数),生成一个符号的模型

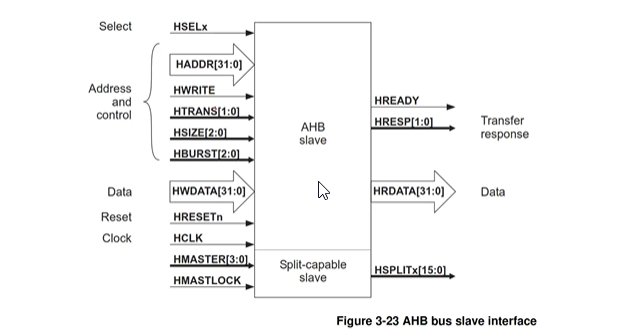

5.4 AHB Slave接口

- split信号在这里是不需要使用的,因为是单周期的读写

5.6 AHB 时序接口

5.7 SRAM接口

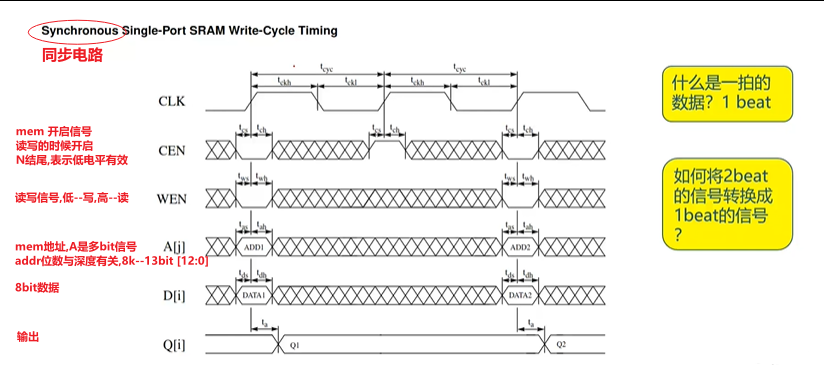

*sram接口时序类比于FiFo,sram是同步电路,读写都是通过时钟驱动的

- tckh -- 高电平占时间;tckl -- 低电平占时间

- CEN -- memory开启信号(只有在读写的时候开启),低电平有效的信号是以n为结尾的

- WEN -- 指示读写信号(低电平为写操作,高电平为读操作)

- A[j] -- 地址(读写数据的地址),与memory的深度有关,8k地址是13bit

- D[i] -- Data_in,8bit

- Q[i] -- 数据输出(和寄存器的命名很像)

如何将2beat信号转化为1beat逻辑?

6.设计文档体系

- 架构设计文档

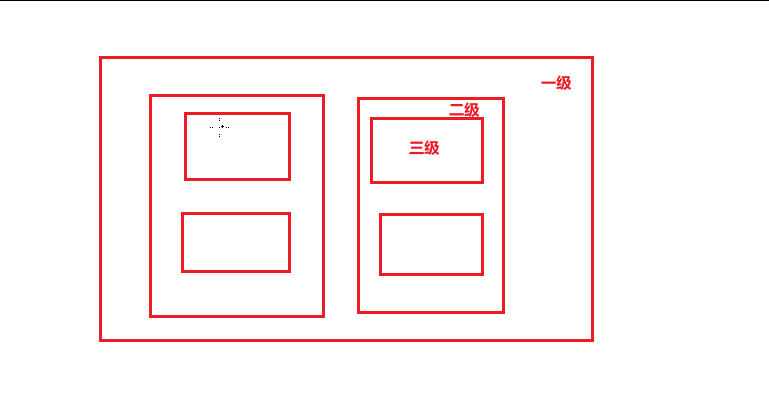

描述架构,表述模块的初级划分,尽量能够划分到二级模块或者三级模块,顶层模块可以看作是一级模块,其中直接集成的模块为二级模块

- 微架构设计文档

包含所有module的划分,而且要和RTL代码中的模块划分一致;一般根据微架构设计文档进行RTL Coding; - 集成文档

集成时的接口

6.1 架构设计文档

- 功能列表

从需求的基础上,在硬件的基础上进行硬件的扩展,保证功能列表比较全 - 软硬件划分

有的模块在不同的模式下需要使用软件进行寄存器配置,配置寄存器

在进行一些IP设计的时候,IP需要进行不同模式下的工作,就需要配置一些寄存器,需要配置哪些寄存器,地址范围是多少,配置顺序是怎样的,就需要通过软件进行配置;CPU通过I-cache读取指令配置寄存器 - 软硬件协同工作

明确哪些工作是软件做的,哪些工作是硬件做的 - 硬件模块功能描述

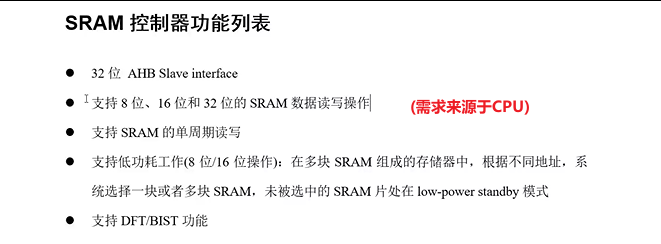

6.2 SRAM控制器功能列表

- CPU的load和store指令,支持byte,word,halfword的操作

- 支持单周期的读写(如果读写的access time超过一个周期就不能支持单周期读写),前提已经确认过读访问时间和写访问时间

- 支持低功耗工作,本身是做设计的基本要求,将存储体划分为多块bank

6.3 SRAM控制器软硬件模块划分

无,AHB的读写请求可以直接转换为SRAM的读写访问,一次就可以完成指令,不需要与软件进行配合

6.4 SRAM控制器的软硬件协同工作描述

无

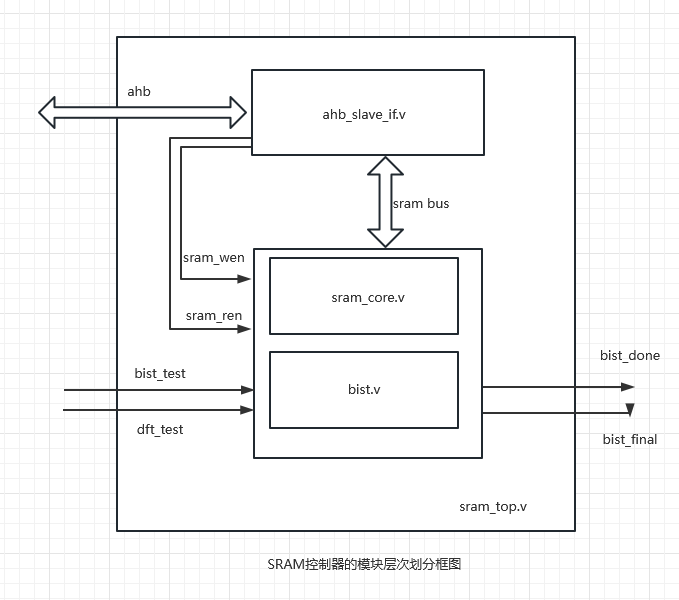

6.5 SRAM控制器模块功能描述(硬件模块)

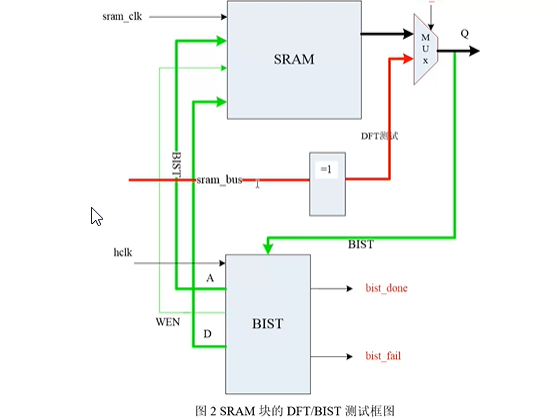

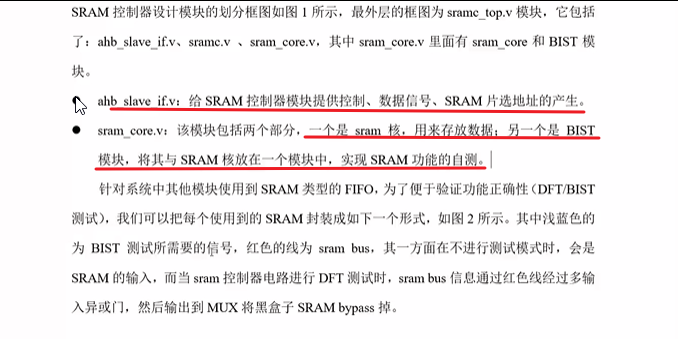

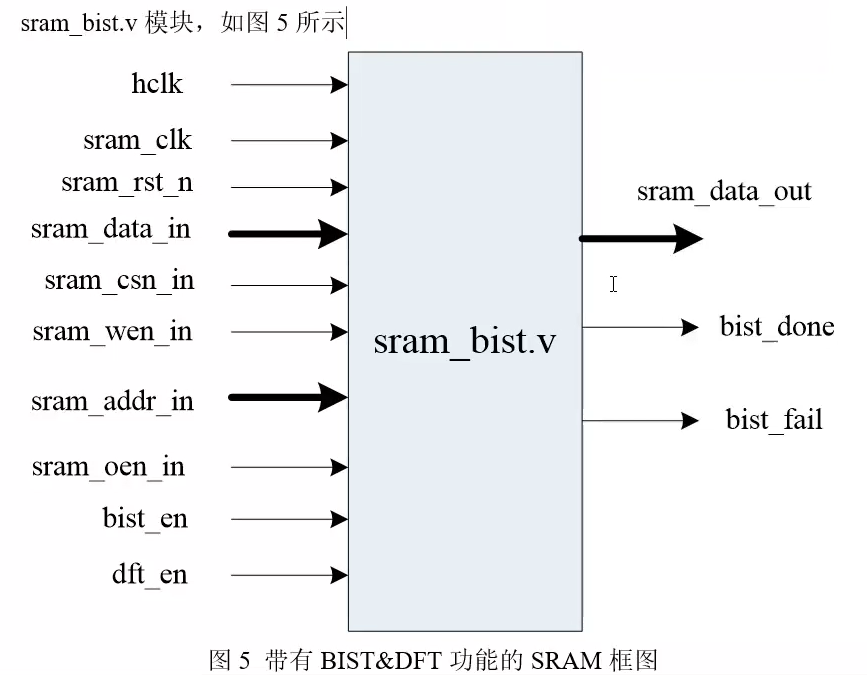

- bist是不需要进行体现在模块划分框图中的

- 需要将大概的信号连起来

- bist和dft:芯片中会有一些memory和standcell,如果没有dft和bist接口,流片回来如何确保芯片的功能是正确的?直接通过function进行测试,测试范围不够完全(流片回来之后,功能可能还没有开发完成,function模式进行测试,测出来的覆盖率是不好的,有一定的潜在风险),需要通过dft进行测试筛选,dft可以测试core中的器件是不是好的,dft可以将寄存器进行连接(可以使用mux),输入激励之后,可以对寄存器之间的组合逻辑进行测试

- bist是内建自测试,在硬件内部产生激励和结果,进行测试

- bist适合对于standcell进行测试,memory通常都是大块固核,固核也有时钟驱动,但是读写时序和扫描链的差异比较大,如果想要memory可测,可以将memory接到顶层,灌激励,速率较低

- bist测试针对与mem测试,dft针对于standcell或者组合逻辑和时序逻辑(器件)进行测试

- 在芯片内部集成硬件,这个硬件可以输出激励给memory,还可以从memory接收输入并进行比较结果是不是正确

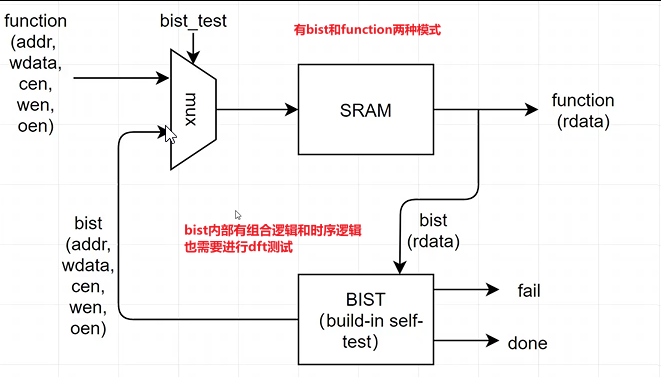

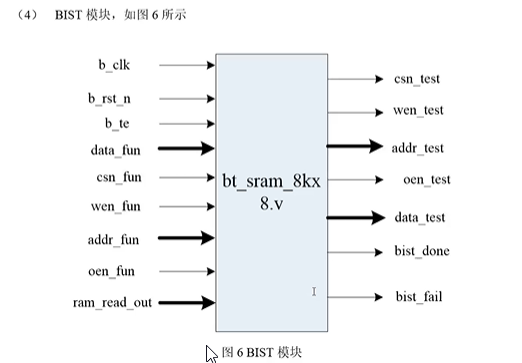

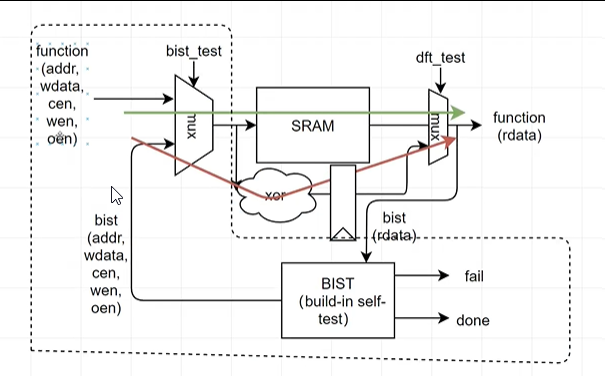

Bist测试(built in self test)

function模式下,SRAM正常被总线访问

ADDR

CEN -- 片选使能

WEN -- 写使能

OEN -- 输出使能

wdata -- 写数据

bist模式下,bist模块发出信号对SRAM进行访问

ADDR

CEN -- 片选使能

WEN -- 写使能

OEN -- 输出使能

wdata -- 写数据

function模式下的信号和bist模式下的信号进行mux

在bist_test信号的使能下输出给SRAM

SRAM会有输出,这个输出会给到function的rdata和bist的rdata

bist模块接收到rdata之后,会将rdata进行比对,比对完成之后会输出

比对结果,bist_fail和bist_done

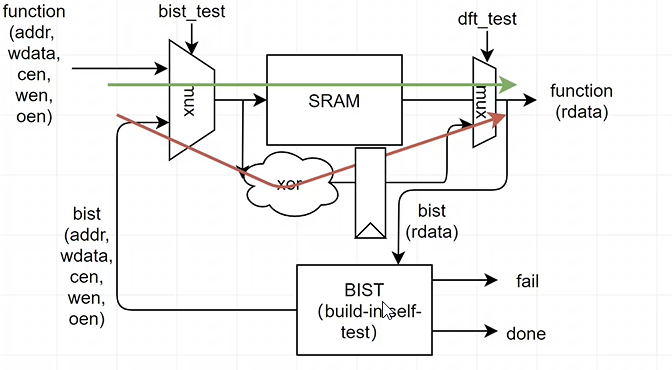

bist模块也是由一堆组合逻辑和时序逻辑组成的,这些组合逻辑也需要进行dft测试

bist模块产生的信号(输入和输出)都是要和SRAM进行打交道的

在dft模式下,SRAM是不会正确的进行开启和关闭的,SRAM开启需要CEN,WEN,OEN信号的配合,在dft模式下,这些信号根据覆盖率进行驱动,信号在SRAM中是走不通的

在dft模式下,走跳过SRAM的路径,在SRAM周边做一些逻辑,比如使用异或门,在输入的mux信号做一个旁路,经过一个打拍处理(避免出现组合逻辑环),然后输出在dft-test信号下输出bypass路径的输出

- 插入寄存器,避免组合逻辑环(存在一条路径,不经过任何时序逻辑,从输入到输出再到输入),插入寄存器可以打断组合逻辑环

- 有组合逻辑环在进行综合的时候会失败

6.6 附

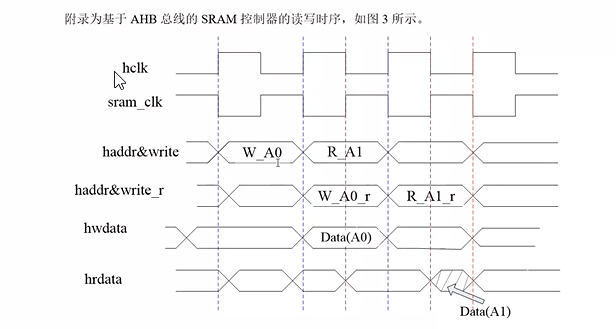

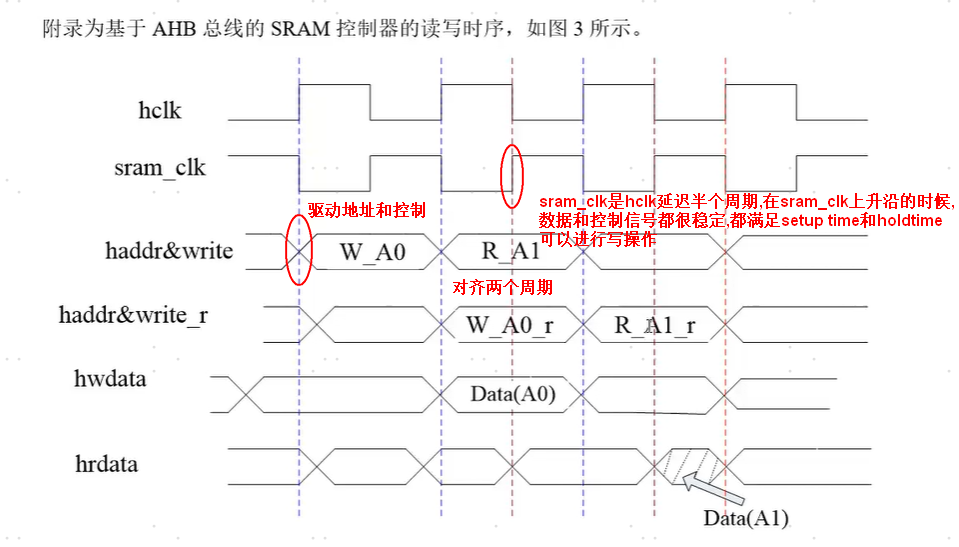

- sram_clk可以看做是hclk向后延迟50%占空比(半个时钟周期)

- 对于写数据操作,将AHB总线的address phaze打一拍,将address phaze和data phaze进行对齐,对齐之后,可以拿到写使能,写数据和地址,进行写操作

- 对于读数据操作,将AHB总线的address phaze打一拍,将address phaze和data phaze进行对齐,对齐之后,进行单周期操作,在当前周期就可以得到读数据

- 利用AHB中线的数据打拍操作和sram_clk是hclk取反,进行单周期的操作

7.微架构设计文档

- 功能框图

- 各模块详细描述

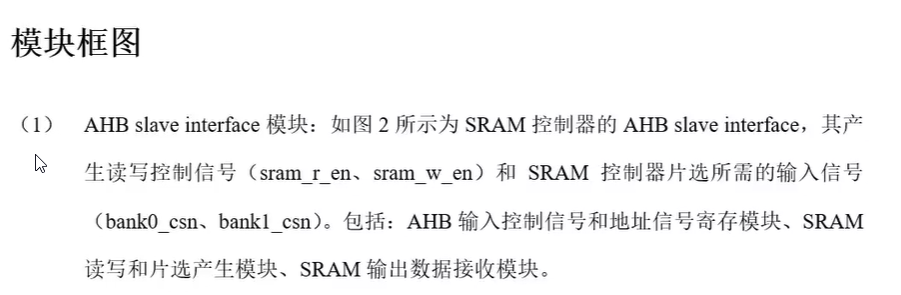

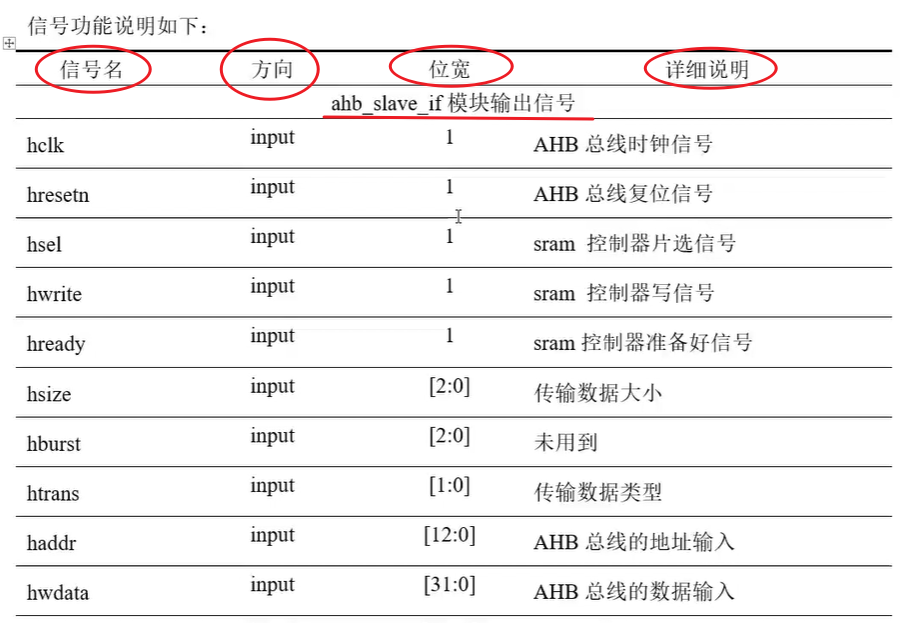

- 模块框图

- 信号描述

- 模块功能定义

7.1 SRAM控制器架构框图

- 列出信号线的位宽

- AHB控制信号转换为SRAM控制信号,如果信号转换比较复杂可以单独设置模块

- SRAM输出信号

- 子模块可以细化架构图

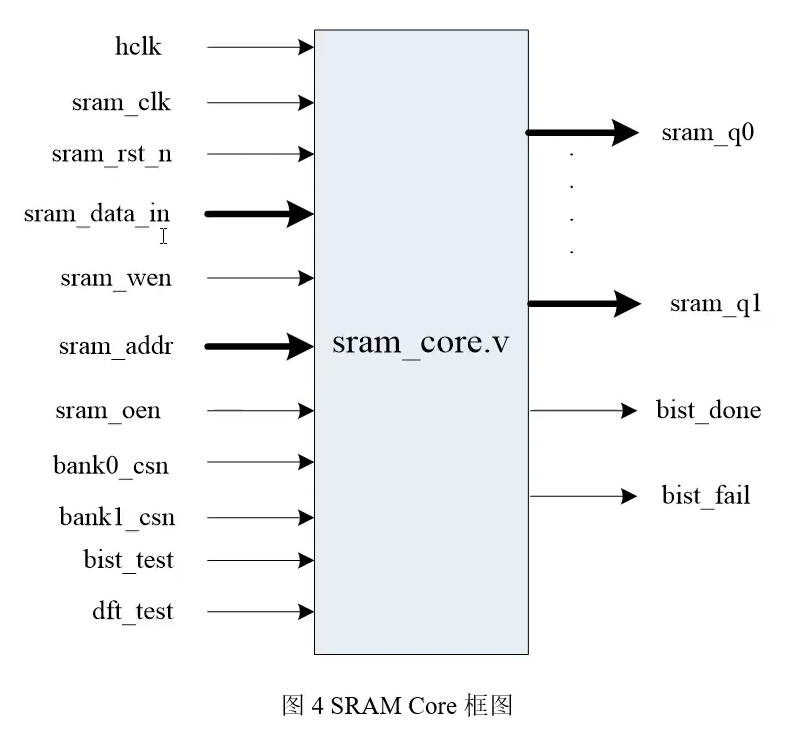

- bank0(4个mem),bank1(4mem),进行低功耗设计和降低深度

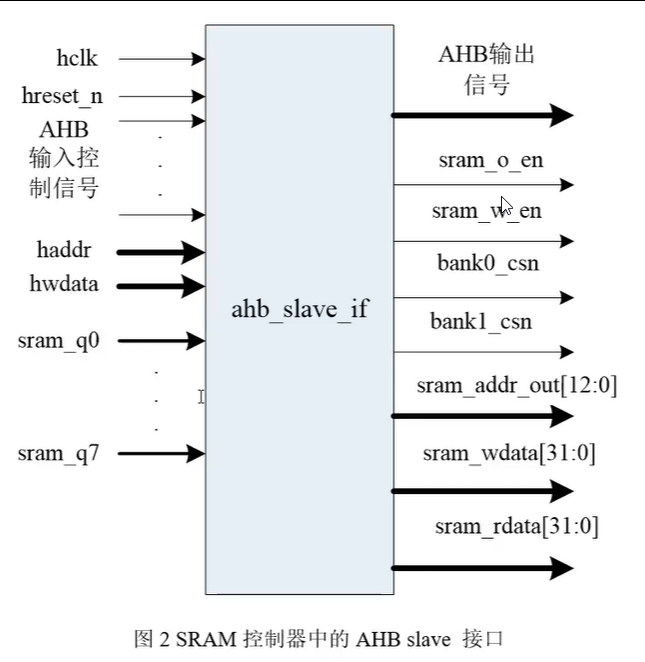

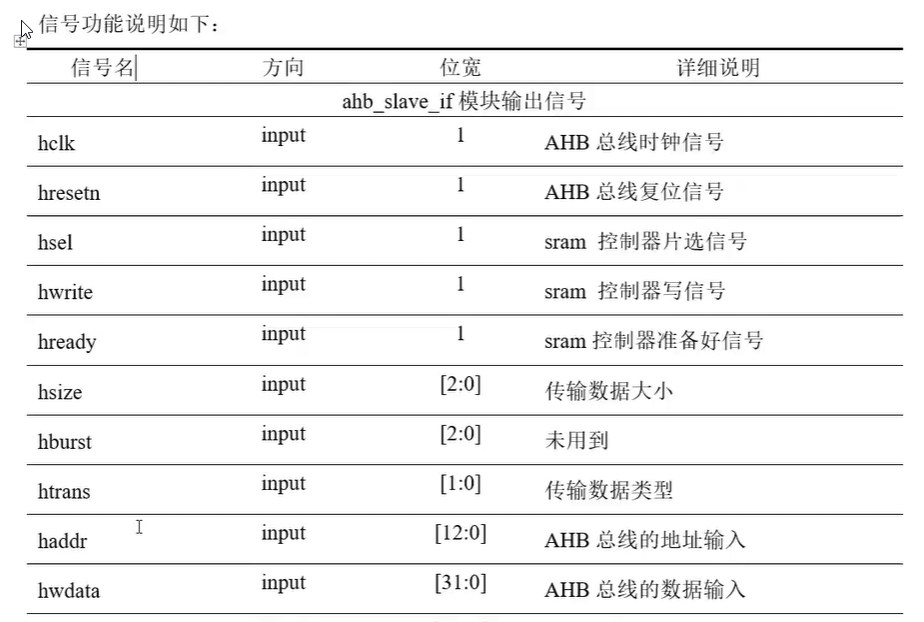

7.2 SRAM控制器各个模块详细描述

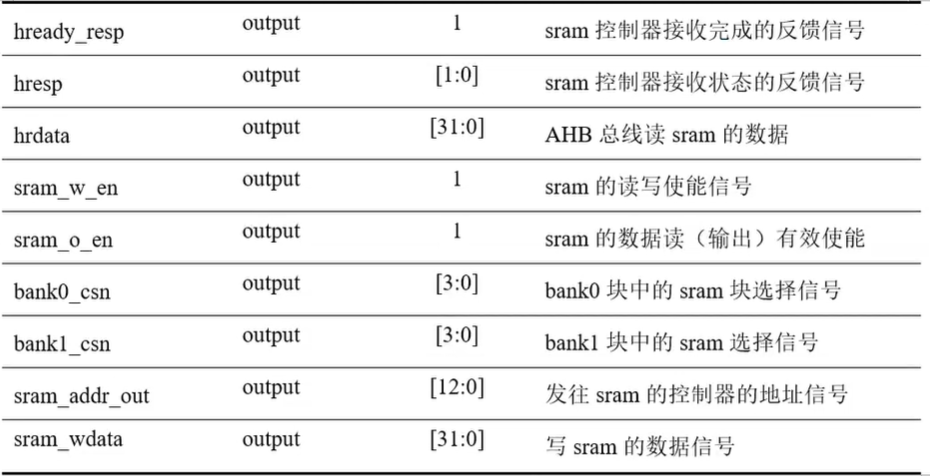

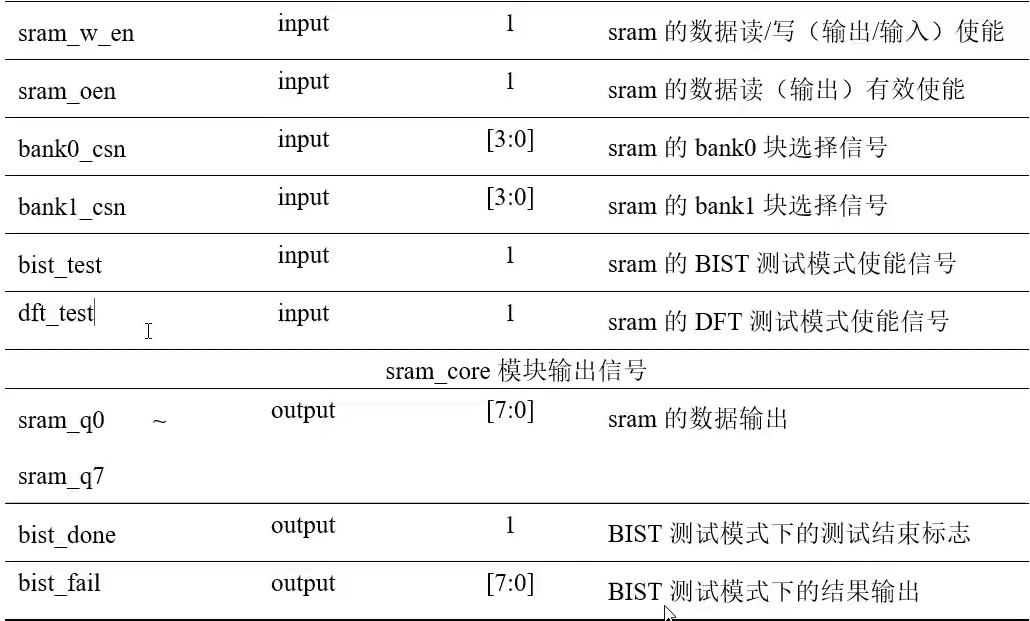

信号描述(不同公司有不同的命名规范)

1. AHB相关的信号

- 信号描述可以按照模块相关性进行描述,也可以按照输入输出方向进行描述

- 指明地址位宽,SRAM地址位宽,位宽与深度有关,8k寻址使用13bit;深度为8k就表示要有8k个地址,使用13位二进制进行表示

- 在描述AHB_Slave_Interface中,SRAM输出是AHB_Slave_Interface输入

- sram_w_en--读写信号

- sram_o_en--这个信号拉高,才能进行输出

- bank0_csn\bank1_csn--每个bank有四个memory,所以是4bit位宽,选择bank0或bank1中的memory

- sram_addr_out--总线发送到sram中的地址信号,8k--13bit,广播到8个mem中,每个mem接收到的地址都是一样的

- sram_wdata--写sram的数据信号,广播到bank0和bank1,根据选择bank0和bank1写入选中的bank0或者bank1

2. SRAM相关信号

- SRAM接收AHB_Slave_Interface的输出

- bist_test和dft_test和顶层模块相连

- 输出信号有bist_fail,bist_done,sram_q0-sram_q7

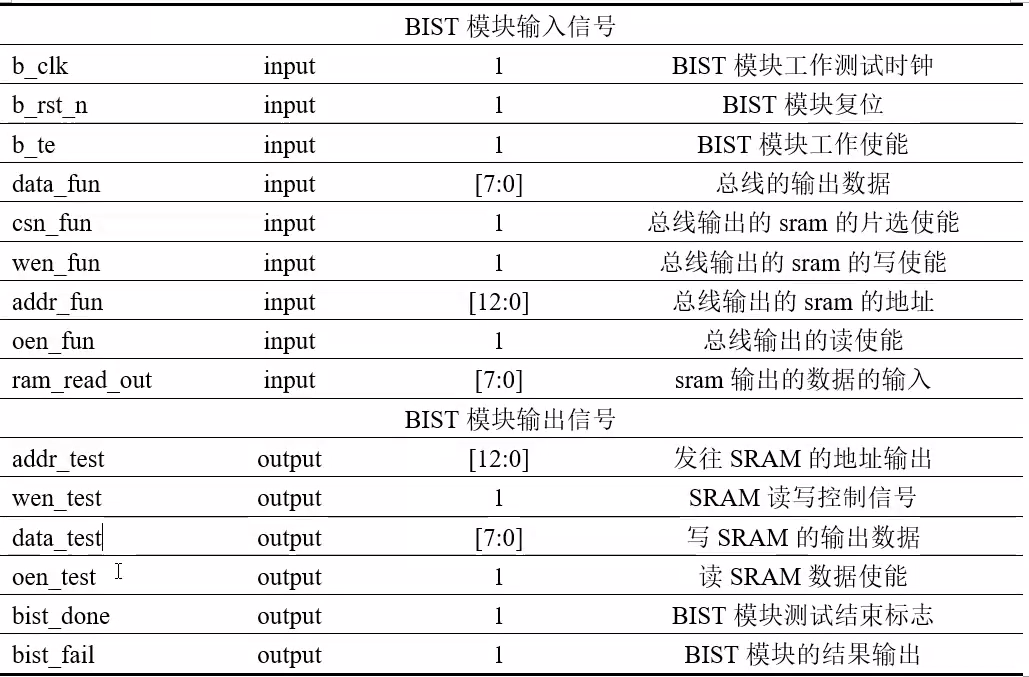

3. sram bist接口

- 包含sram实体和bist产生逻辑

4. bist module

- 产生bist逻辑,bist本身是如何产生激励的逻辑

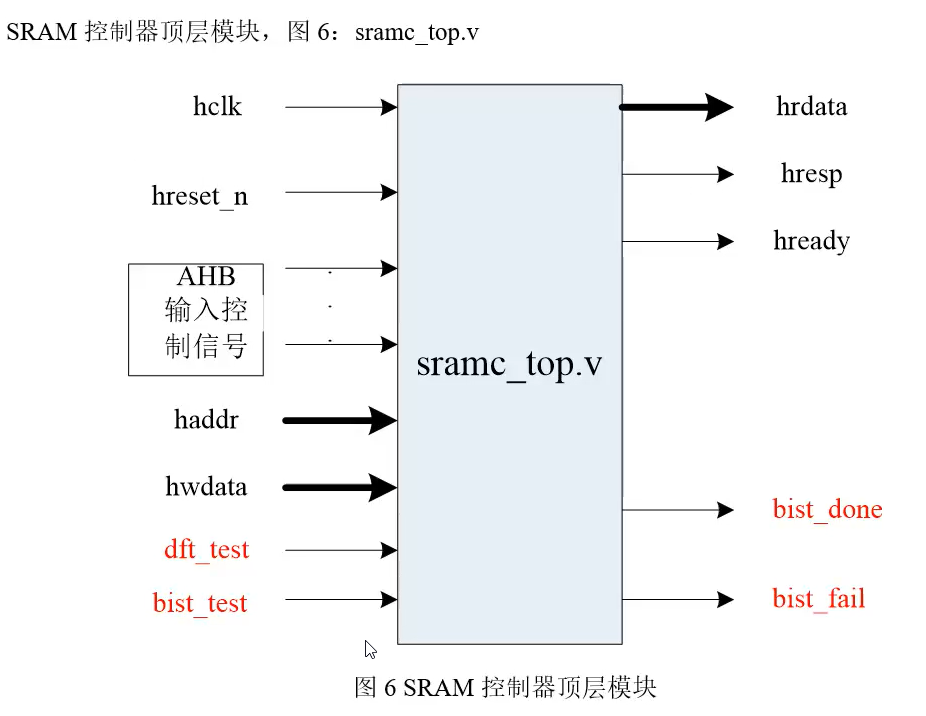

5. 顶层信号列表

- AHB输入输出

- dft和bist相关的输入和输出

7.3 描述微架构图

- AHB时序的处理

- 如何将AHB信号转换为SRAM信号

- 如何生成片选信号