14-Verilog for Verification

Verilog for Verification

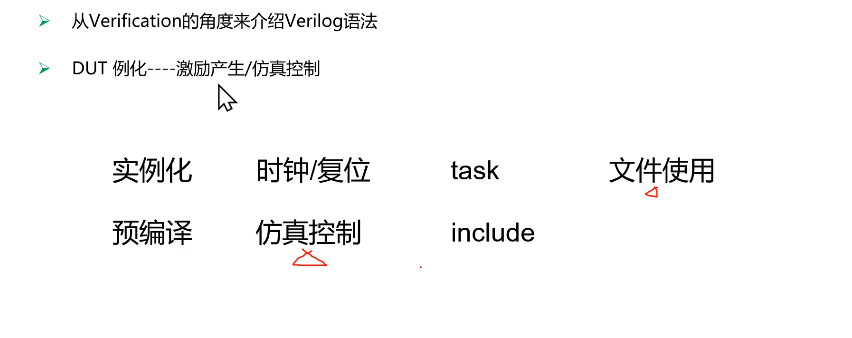

1.引言

-

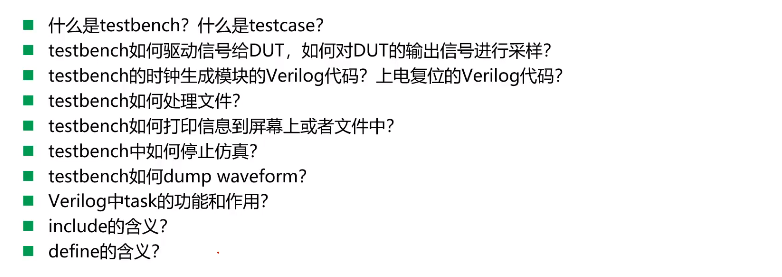

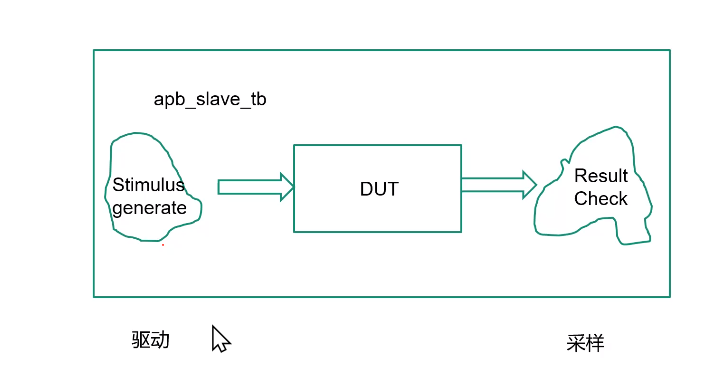

Testbench也是一个模块(module...endmodule)

-

Testbench没有输入和输出,因为它是一个闭环,自己产生激励,灌给module,module输出响应,testbench会捕捉响应,进行比较,自己在自己内部形成闭环

-

完成对待测设计的例化,测试代码的封装,提供测试激励,收集测试结果

-

无需综合,行为级描述优先

module module_name_tb;

//测试代码

endmodule

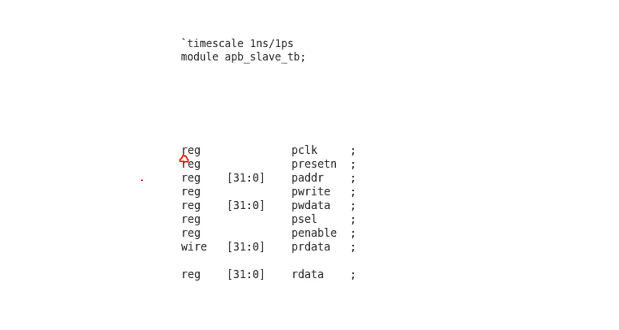

2.变量声明

- 给待测设计的输入端口提供激励

- 通过待测实际的输出端口收集激励

- 提供激励的信号:reg类型信号进行声明,便于在initial和always中进行赋值

- 收集激励的信号:reg或wire,多数情况下使用wire

- 也可以使用logic变量进行声明

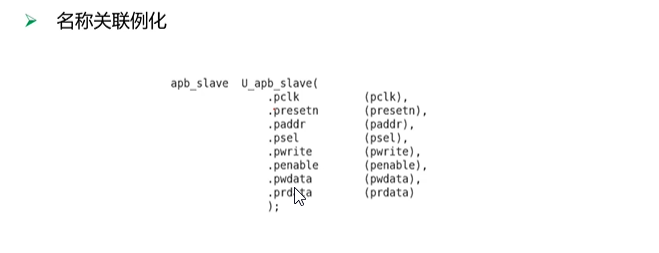

// 名称关联的方式

apd_slave U_apb_slave(

.pclk (pclk),

.prestn (prestn),

.paddr (paddr),

.psel (psel),

.pwrite (pwrite),

.penable (penable),

.pwdata (pwdata),

.prdata (prdata)

);

3.激励

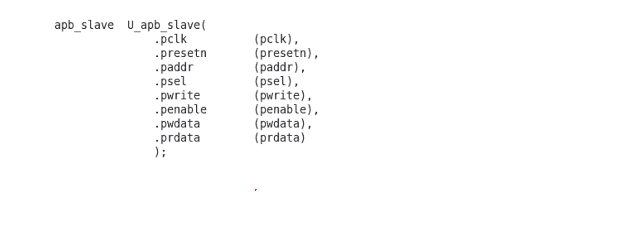

3.1 时钟产生

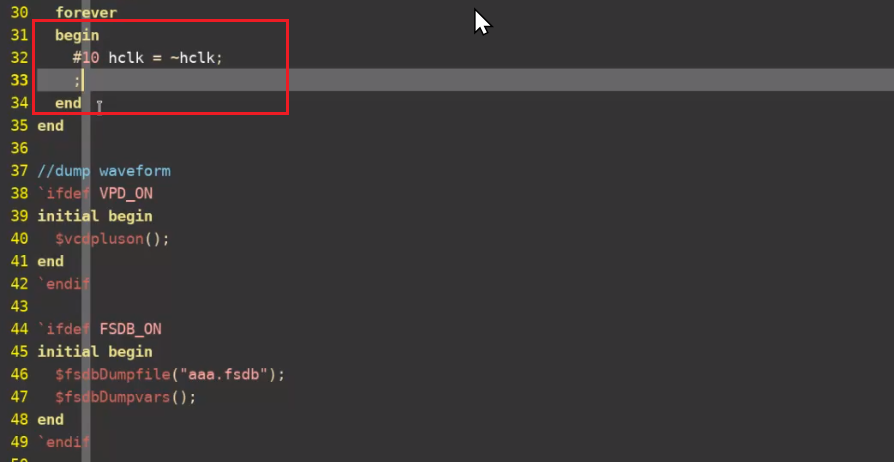

- forever语句,必须写在initial中

- forever后面执行多条语句,加begin end

// clock generate

initial begin

pclk = 0;

forever

begin

#10 pclk = ~pclk; // 时钟周期是20个时间单位

end

3.2 reset信号

- 低电平有效

- 在某个时间点将reset置为0

reg rst_n;

initial begin

rst_n = 1'b0; // 复位信号置为低电平

#45;

rst_n = 1'b1; // 延迟45个时间单位之后,将复位撤销

end

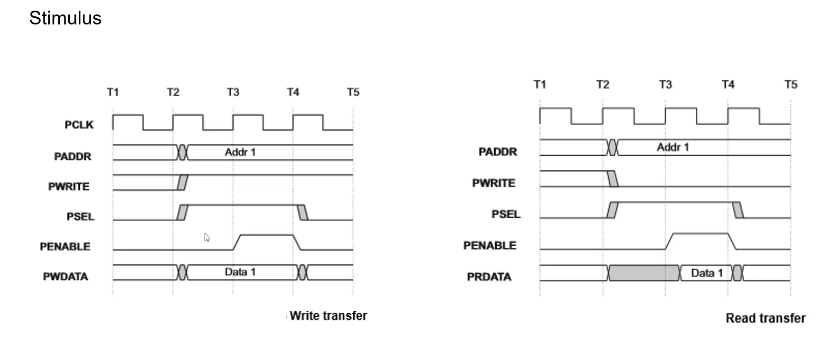

3.3 产生激励

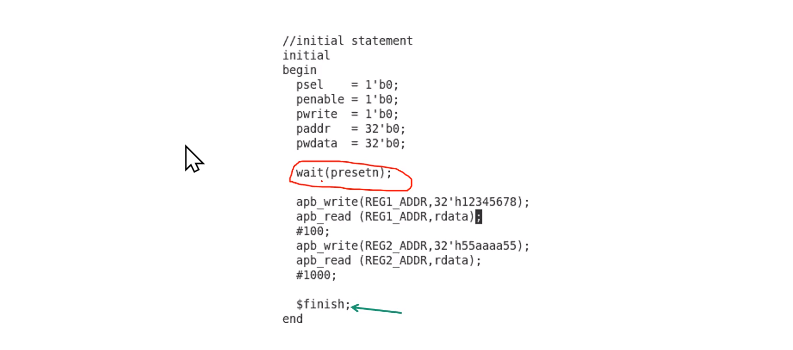

- wait(条件表达式),条件表达式为真的时候解除等待

initial begin

......

wait(rst_n = 1'b1);

wait(sim_start)

......

end

- @(posegde clk) ...

initial

begin

.....

wait(rst_n = 1'b1);

wait(sim_start);

@(posedge pclk);

a = 1'b1;

end

initial

begin

.....

wait(rst_n = 1'b1);

wait(sim_start);

@(posedge pclk);

#3; // 寄存器d到q端的延迟

a = 1'b1;

end

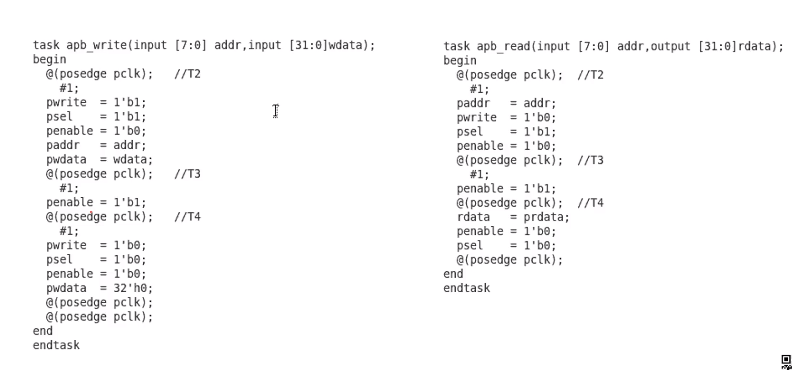

- function是不能有延迟信息语句的

- task是可以具有延迟信息语句的

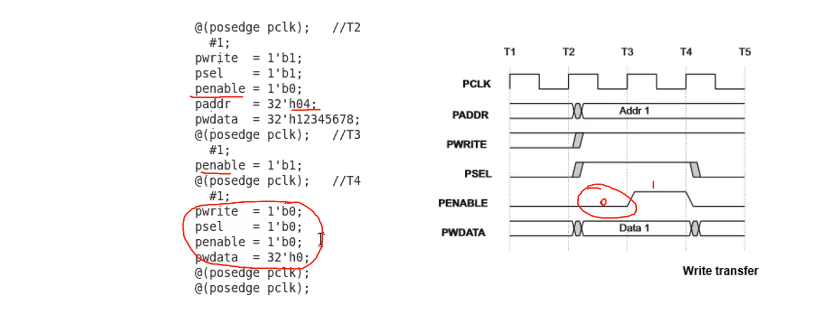

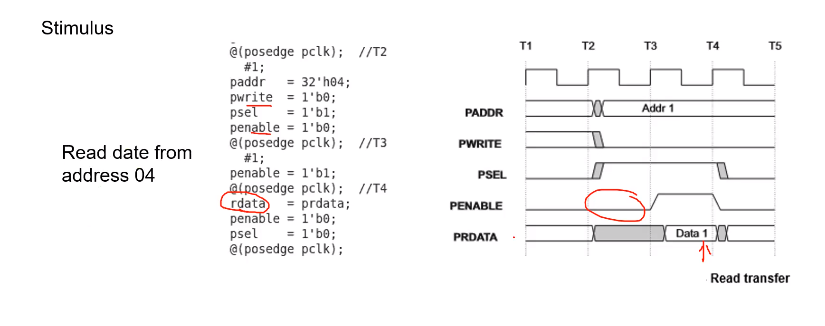

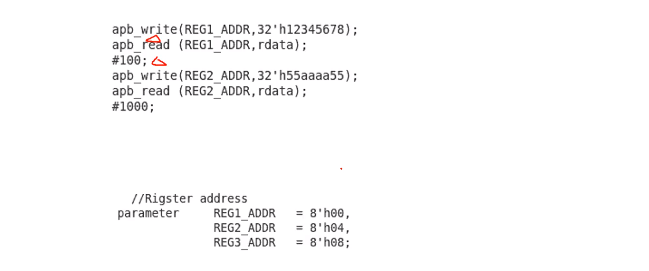

- 将读写操作封装成task

task apb_write(input [31:0] addr,input [31:0] wdata);

begin

end

endtask

task apb_read(input [31:0] addr,output [31:0] rdata);

begin

end

endtask

reg [31:0] memory [1024:0]

FILE0 = $open("block90");

for(address=32'h0,address<32'h80;address=address+1)

$fwriteh(FILE0,32'hFFFFFFFF,"\n")

$fclose(FILE0)

$readmemh("block0",memory);

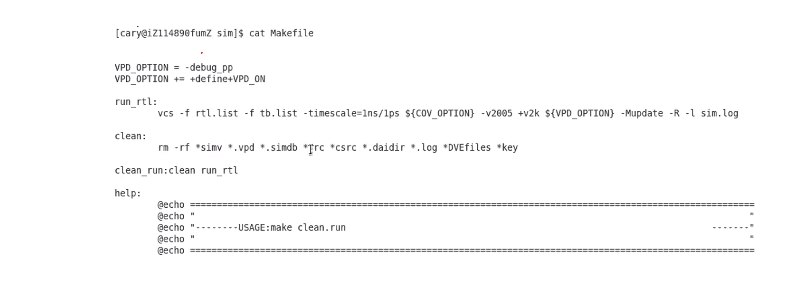

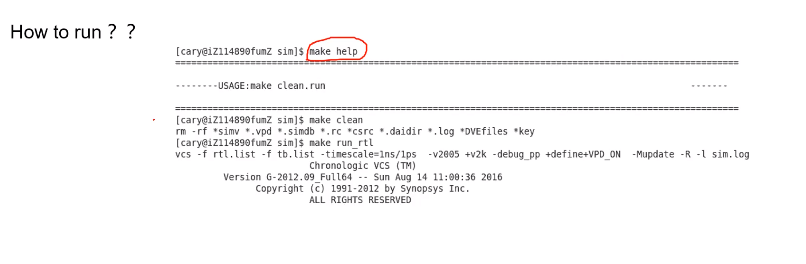

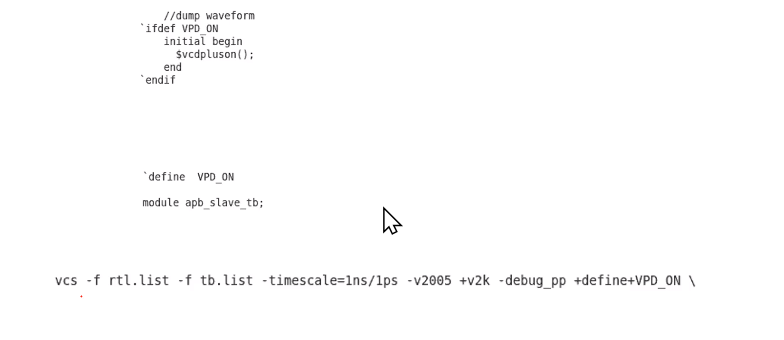

3.4 dump 波形

`ifdef VPD_ON

initial begin

$vcdpluson();

end

`endif

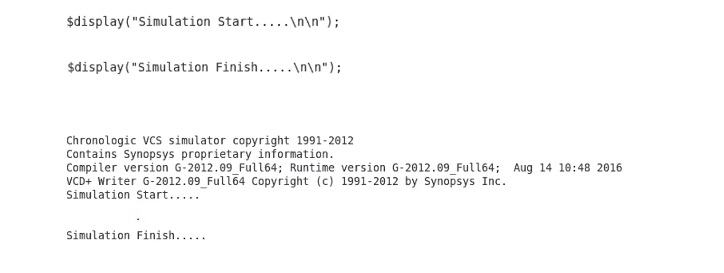

3.5 显示激励

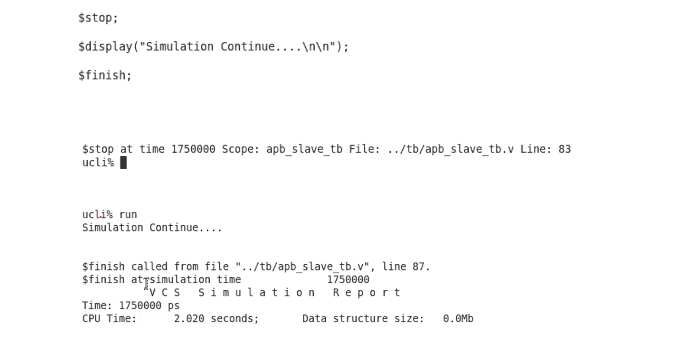

3.6 结束仿真

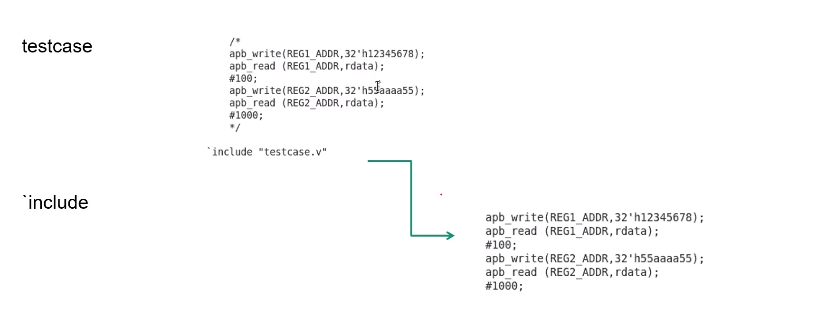

3.7 预编译

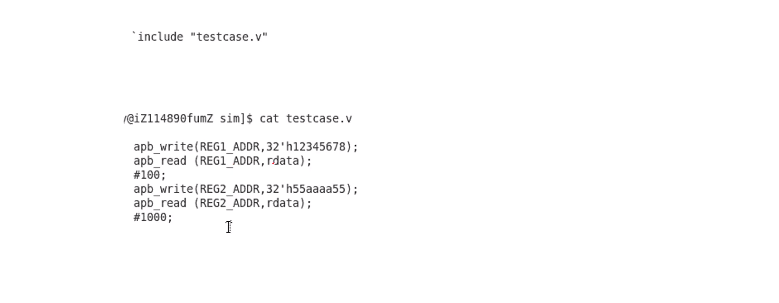

3.8 include

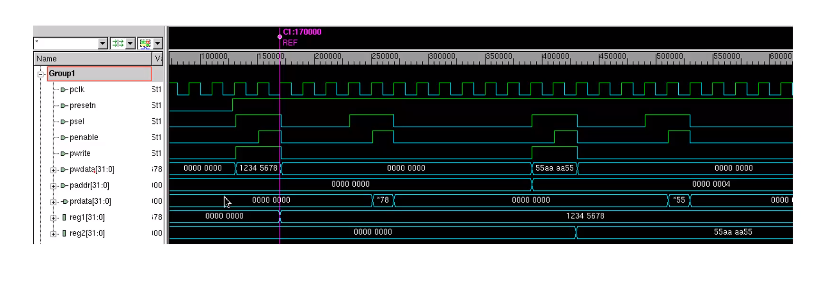

4.实例

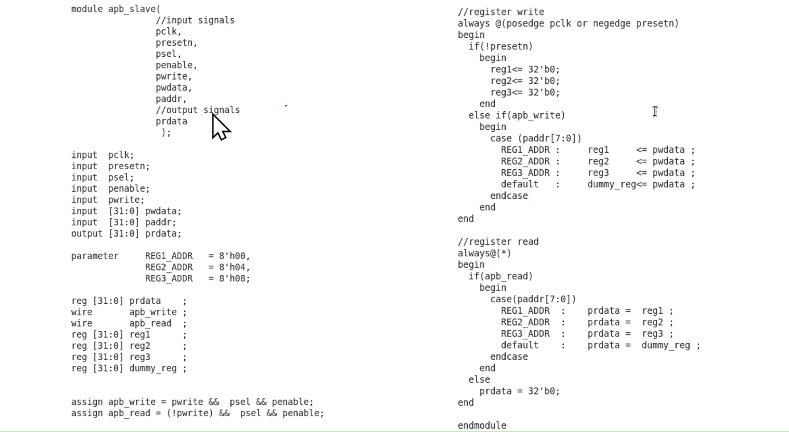

4.1 设计代码

4.2 验证流程

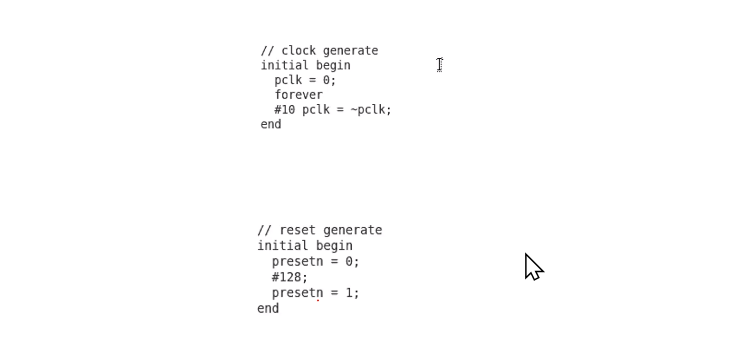

4.3 APB Slave testbench

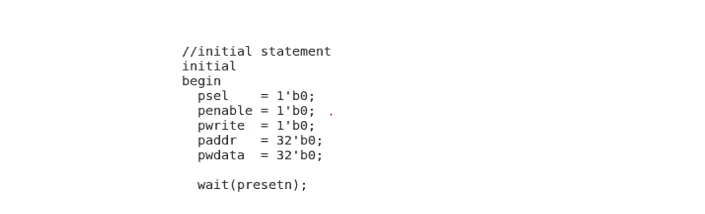

- testbench中输入定义为reg,输出定义为wire

- 例化模块

- 产生时钟和复位

- 产生激励,产生激励的时候要给模块的输入一定的初始值,不给初始值就会产生x态