01-时钟及时钟源

1 什么是时钟?

1.1 时钟定义

跨时钟域处理,是在设计过程中经常要处理的问题,决定芯片的正确和可靠性

电脑中有很多的芯片,每个芯片都是在特定的时钟下进行工作的,时钟信号是连续的脉冲信号;它是按一定的电压幅度在一定时间间隔内连数连续发出的脉冲信号。

1.2 时钟偏斜(clock skew)和时钟抖动(jitter)

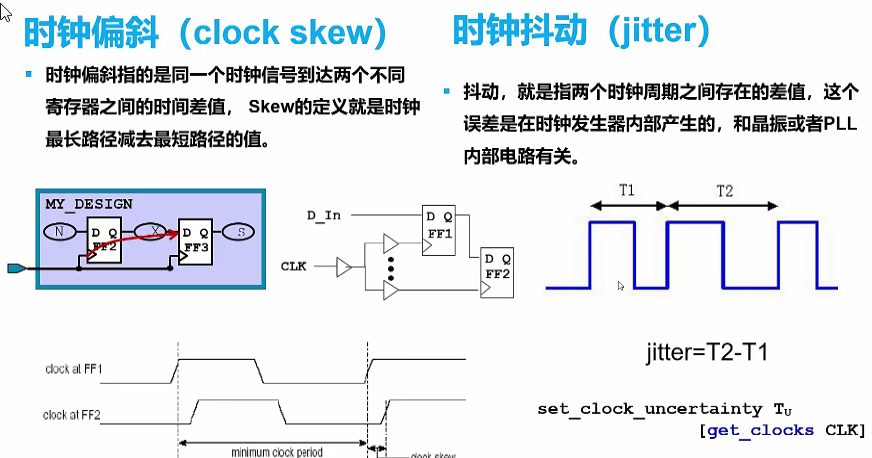

- 时钟的偏斜是与时钟相关的一些特性,有时候会称为clock skew。在实际工作中,时钟会经过很多的一些buffer,来驱动相关的寄存器。经过这些buffer以后,它是一级一级的,粗略的可以看,就是相当于一个时钟的树。

- 如上图所示,在实际设计中,clk到ff1的延迟的信息和到ff2延迟的信息极有可能是不一样的。那么,如何来刻画这两个的差别呢?我们称为clock skew。clock skew是指同一个时钟到达两个不同寄存器之间的差值。一般是在约束的时候,以悲观的方式来处理,那么clock skew的定义就是时钟最长路径减去最短路径的值。比如刚才的电路,到ff1和ff2有两条路径,假设这两个一个是最长,一个是最短的。那么,它们之间的这个差别就是clock skew。

- 时钟的抖动,是这两个时钟周期之间存在的差值。比如上图,一个时钟T1,T2是不太一样的,但是,它是一个同一个时钟。这两个周期存在一个误差,就是T2-T1(jitter),这个误差是在时钟发生器内部产生的。和晶振的内部电路有关系,和时钟的布线没有关联。要刻画这样的一个信息,我们就叫成为时钟的抖动,相当于时钟的不稳定情况。我们在约束的时候需要对clock skew和jitter都做一个刻画。通过set_clock uncertainty,来刻画。时钟的偏斜和适中的抖动。一般会把这两个值作为一个和值来加上去

- clock skew和clock jitter的和值,要通过后端工程师以及晶振信息和PR信息得出一个综合的信息。通过这个值来加相关的约束,这个值一一方面是通过后端工程师,他给你的参考的经验的信息。另外,要去看一下相关的晶振和PR,它本身的一些参数信息。拿到这个信息以后才去做约束设置

2 什么是时钟源?

时钟源顾名思义就是时钟源头

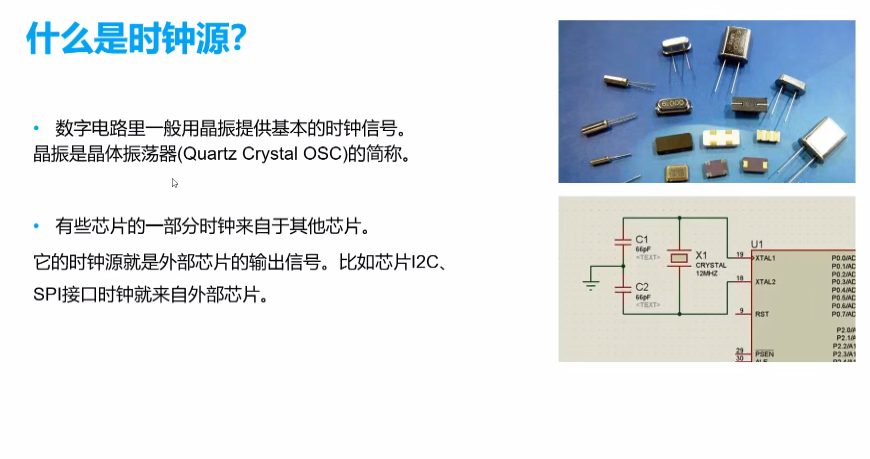

晶振

电路设计中,时钟信号的获得一般有两种方式,第一种,就是说我们通过晶振来提供基本的时钟信号。所以这个时钟的源头就是来自于晶振,晶振简称为晶体振荡器。

用石英晶体(纯净的二氧化硅),是二氧化硅的单晶体。从一块晶体上按一定的方位角切下的薄片称为晶片。在晶片的两个表面。涂一层薄薄的银层后,接上一对金属板焊接引角,并用金属外壳封装,就构成了石英晶体振荡器。

石英晶片之所以能成为震荡器使用,是基于它的压电效应。我们在石英晶片上加上交变的电压,晶体就会产生机械的振动,同时机械的变形振动又会产生交变的电场,在这种相互的变化的过程中,它就可以提供一个相对精确稳定的震荡,也就是时钟的信号。

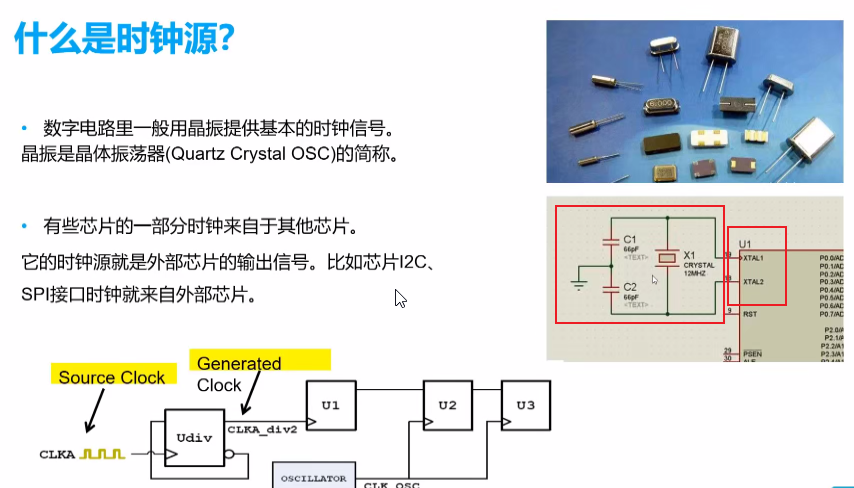

时钟信号来自于外部芯片

另外的时钟源能是来自于其他的芯片或其他的电路。它的时钟源就是外部芯片的输出信号,比如芯片的spi的接口始终就来自于外部的芯片。

上图电路中,有两个管脚,一个是xtal1,xtal2,在这个电路有两种工作模式,一个叫片内时钟震荡的方式,它需要外接振荡器和相关的振荡的电容。它通过这种方式在芯片内部产生时钟信号。这时候如果你的这个时钟信号是通过外部芯片来输入的,那么这个振荡器就撤掉。一般是用xtal1接地,xtal2来接外部的输入时钟信号。这就是一个我们常见的单片机的一个工作时钟的机理。

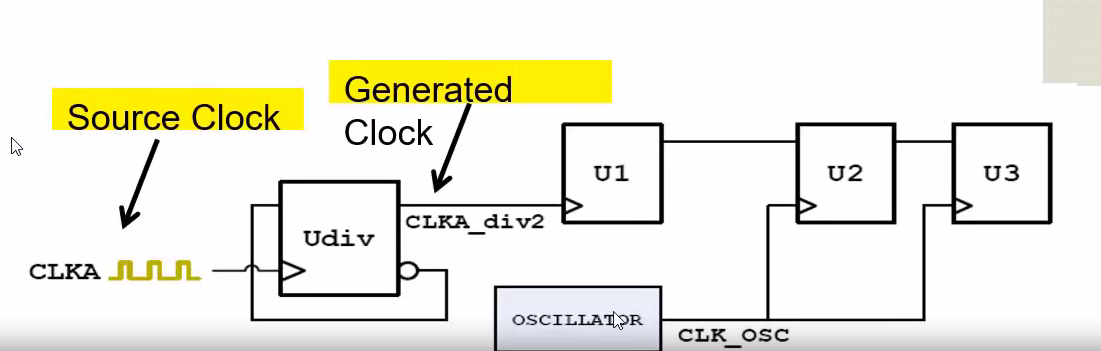

这是初步的电路图,这是我们的clock A,它经过一个触发器分频以后产生一个generated clock发送给相关的寄存器或者模块U1。同时,U2接了一个外界的震荡器,它产生的信号送给相关的模块和触发器。这个design,它的时钟源头是什么呢?首先分频的generate clock时钟肯定不是时钟源头,那么clk就是时钟的源头,那么这个时钟呢,是来自于外部的其他的芯片的信号。同时,振荡器也是这个电路的外部时钟源,所以从这个电路里面讲。这个电路的时钟源,一个是clock A,一个是振荡器产生的clock OSC两个时钟源。