Clock Domain Crossing

Clock Domain Crossing

CDC问题主要有亚稳态问题,多比特信号同步,握手信号同步,异步Fifo等

Topics

- Describe the SoC Design Issues

- Understand the tranditonal verification limitation

- Know about the CDC Issues

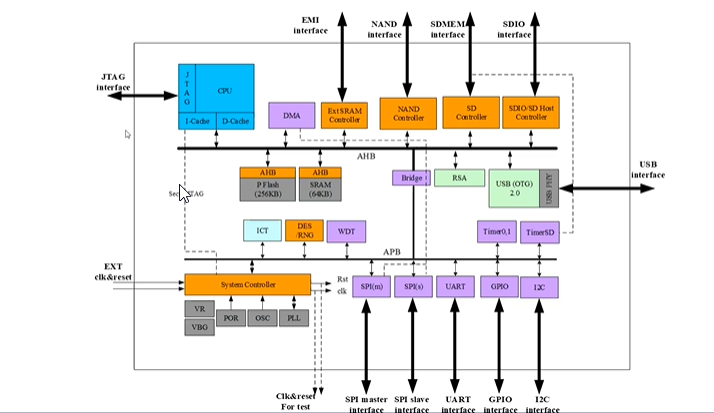

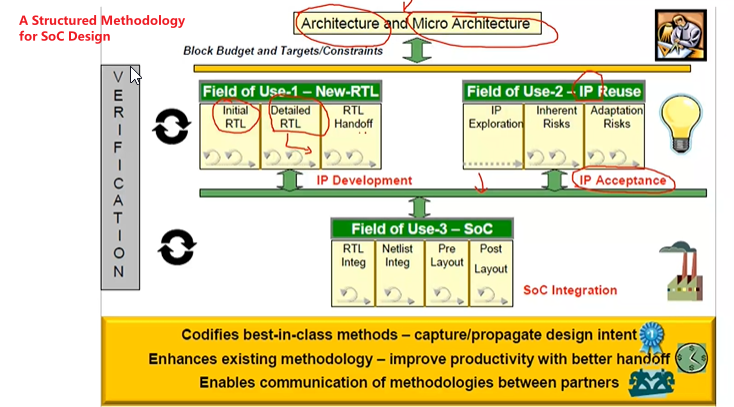

Soc架构

- CPU是整个Soc的大脑,会执行一些指令,这些指令可以控制Soc中的模块,CPU可以给DMA发送指令,还可以给NAND FLASH CONTROLLER发指令....

- CPU有指令的cache(I-Cache),也有数据的Cache(D-Cache),CPU通过JTAG接口与外界连接,进行调试,CPU如果在执行某些代码时出现问题,通过JTAG进行调试

- DMA是一个直接访问的存储器,可以将数据从外存搬移到内存,或者将数据从内部的一个组件搬移到内部的另外一个组件,DMA数据在进行搬移数据的时候,不需要通过CPU进行搬移,可以通过CPU下发一个指令给DMA,DMA进行数据的搬移

- 数据不一定存储在Soc内部,内部的PFLASH,SRAM存储空间都比较小,可以通过外挂存储芯片存储数据,通过控制器来访问外接的存储芯片,比如SRAM芯片和NAND Flash(存储密度更大一些);SD Controller可以访问一些SD卡

- AHB-高速总线,AHB上挂载的都是一些访问速度快的模块,因为要大批量的传输数据

- APB-慢速总线,挂载的模块传输数据量比较小,传输速度慢

- System Controller系统控制器,上电,时钟,复位

- 一个Soc中的模块很多,CPU的工作频率较高,所以时钟域跑的比较快;SPI,UART本身对接的外部接口的变化率比较低,使用CPU的频率去跑,频率大,功耗大,会造成浪费;对于速率要求不高的模块可以降低频率,降低能耗,使用低速总线

- RSA,USB模块有自己的时钟频率

- 不同模块有不同的时钟频率,不同模块之间会有一些交互,所以要解决CDC

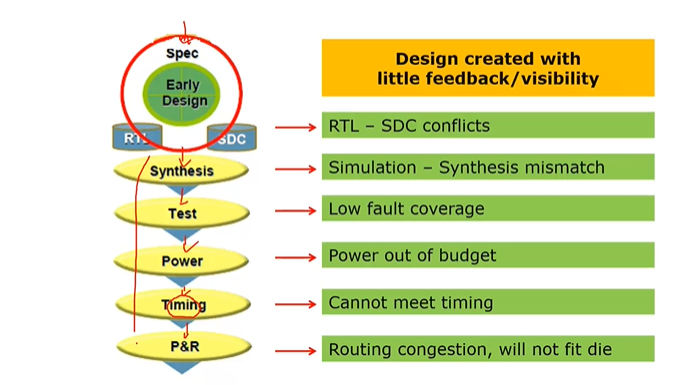

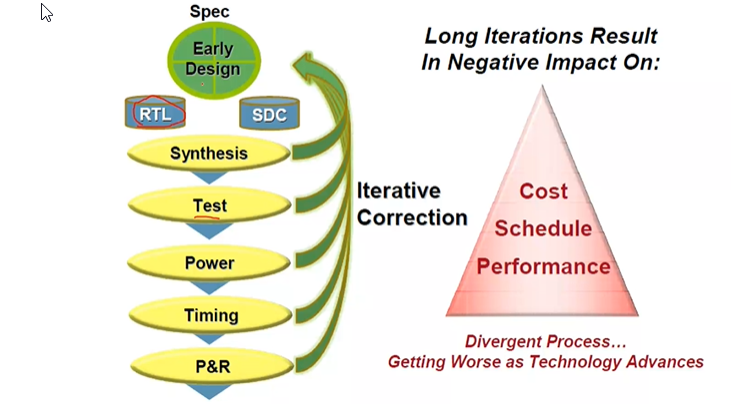

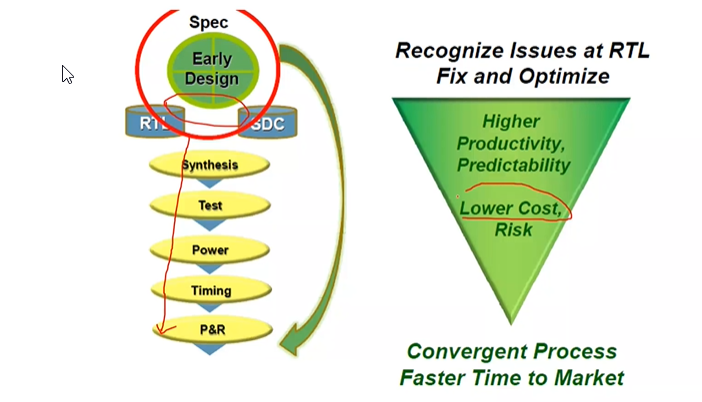

Soc Design Problem

-

很多问题都需要进行修改RTL或者是Spec,发现问题的时间点越接近前段,成本越低,有没有一种方式可以在写RTL的时候,就可以检查这些问题

-

SpyGlass 可以在前期检查问题,效果肯定没有实际的pr,timing,power检查准确

-

不同的IP集成在一起会出现跨时钟域的问题

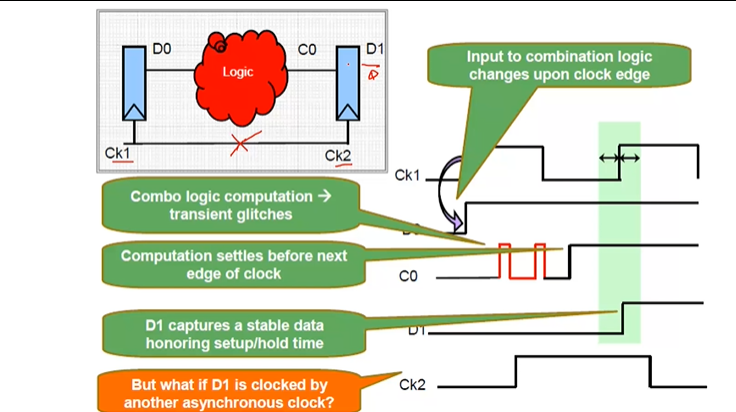

Principle of Synchronous Design

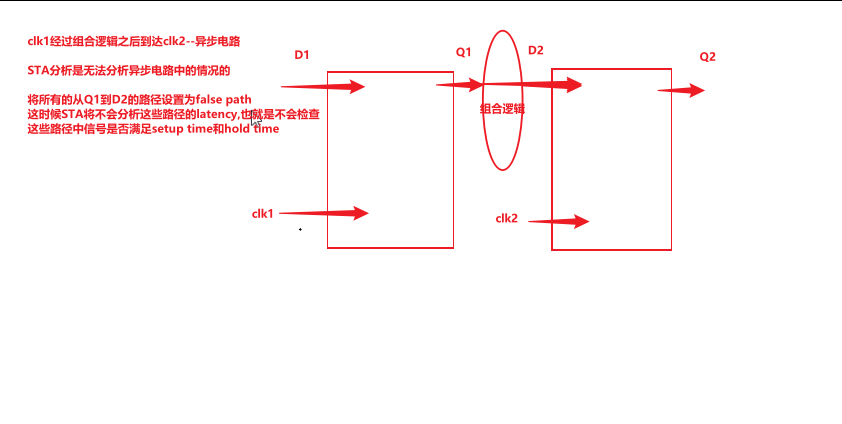

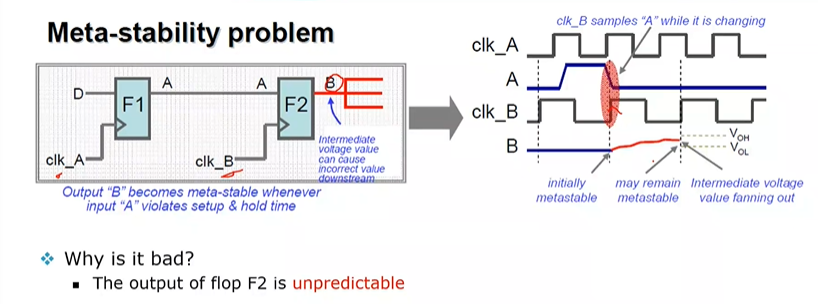

- 上面的设计使用了两个clock,出现跨时钟域的设计,clk1直接连到clk2上就不合理;D0到C0中间经过组合逻辑,会加剧亚稳态的形成

- D0信号是稳定的,经过组合逻辑之后可能在C0会出现毛刺,因为是异步电路,clk2可以在c0端任意时间点内进行采样,这时就有可能会采样到亚稳态

- 如果clk1和clk2是相同的时钟,那么只要保证C0处信号满足在clk2的setup time和hold time就可以,不是产生亚稳态

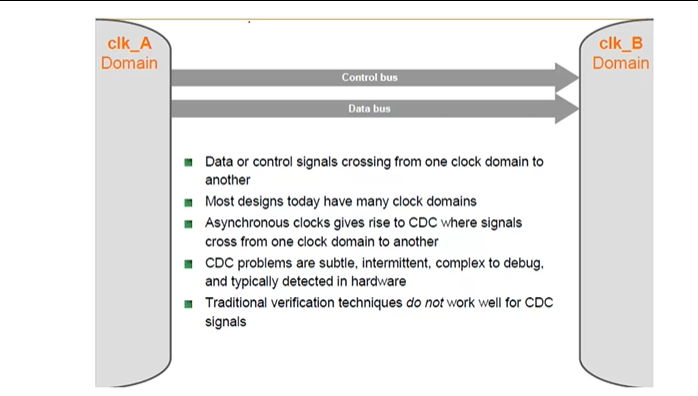

What is a Clock Domain Crossing

- 数据或者控制信号,从一个时钟域跨越到零一个时钟域

- Soc设计有很多时钟域

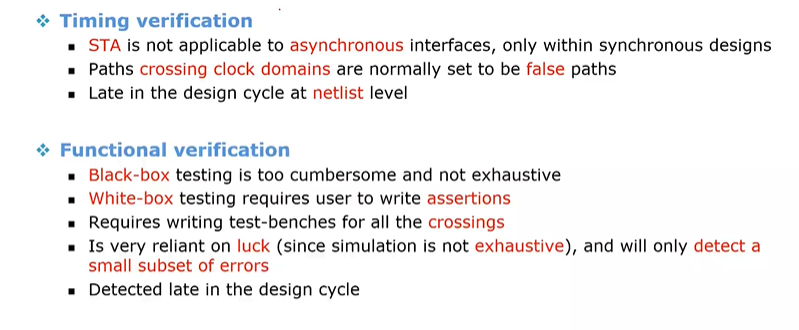

Traditional verification and their Limitation

- STA一般进行同步电路的设计进行分析,STA往往是在netlist生成之后进行的时序分析,但是这个时间点晚于RTLcoding时间节点很长时间,出现的时机也不太合适

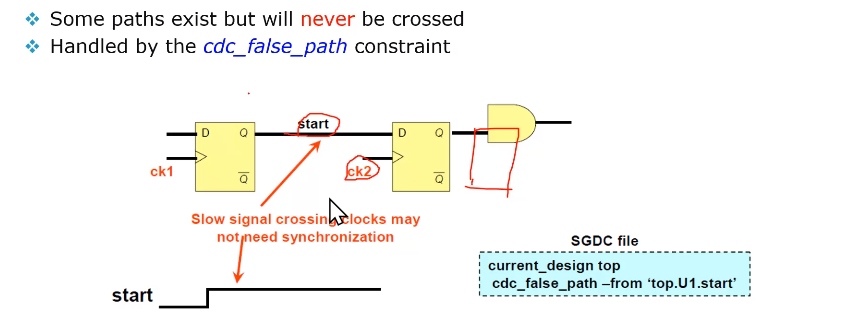

- false path

- 黑盒测试-不关心内部的实现,只关心接口和功能;白盒测试,即关心接口也关心内部的结构,会深入到模块内部进行验证

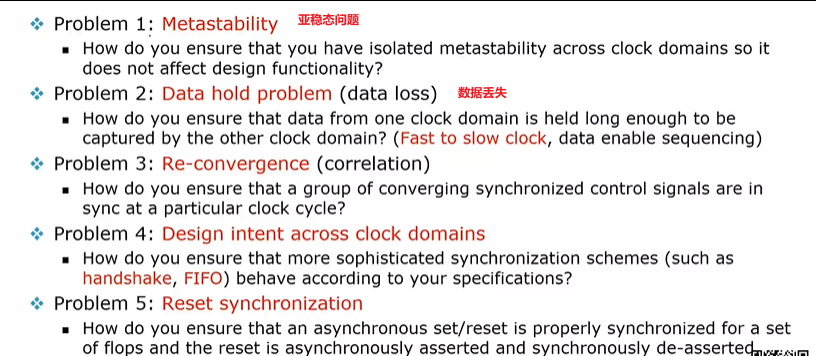

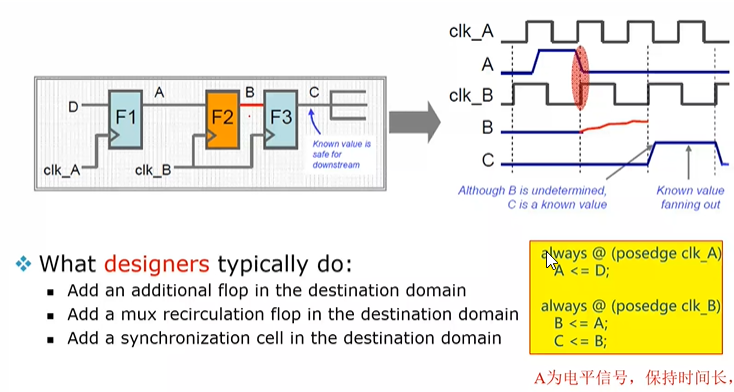

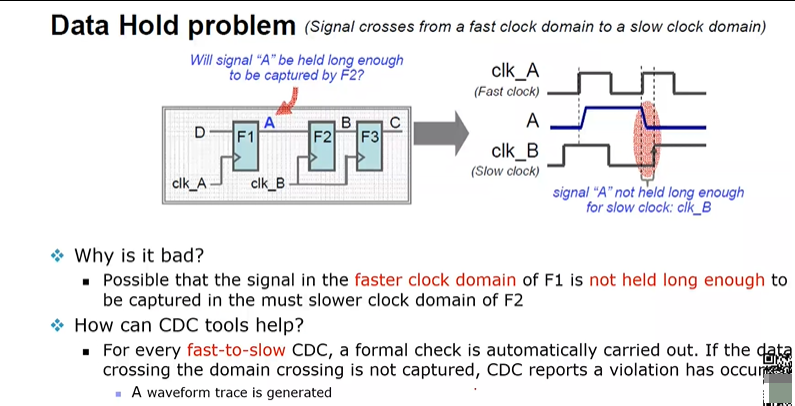

Types of CDC Problems

- data hold问题产生数据丢失,就是一个时钟域频率很快(1G),另一个时钟域信号很慢(1M),信号由快时钟域到慢时钟域传递的时候,在时钟上升沿,可能采集不到快时钟的数据

亚稳态问题

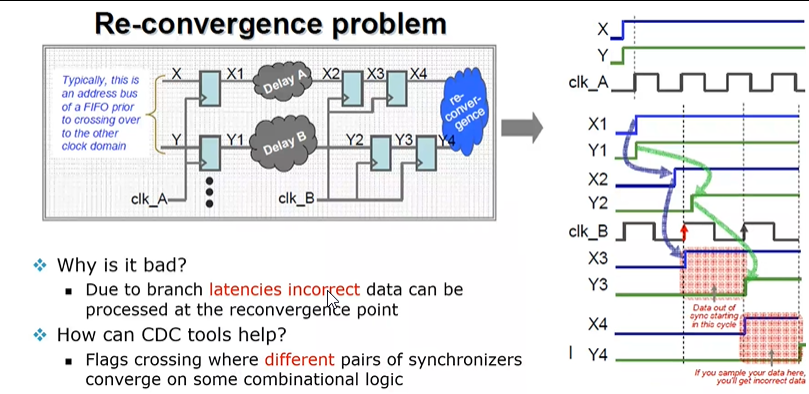

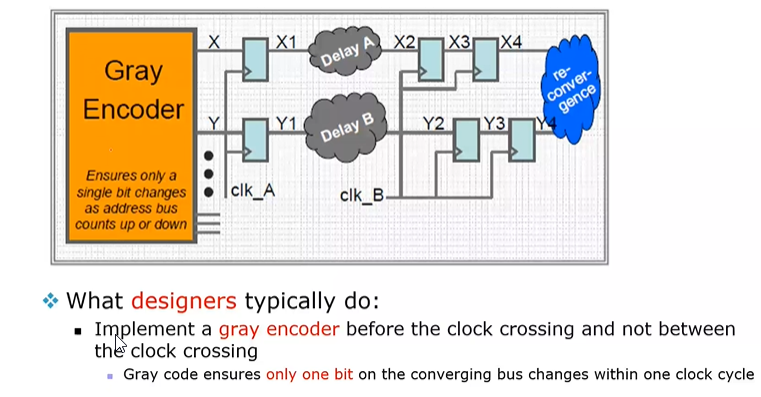

重汇聚问题

- 两个信号分别经过同步器之后,因为同步器导致的latency问题,也会产生亚稳态,CDC工具可以进行检测和解决

- FIFO的地址操作都是加1的操作,使用格雷码进行编码,相邻两个数之间只更改1bit,即使是因为latency的影响,也不会产生新的状态,latency只影响同步时间的早晚

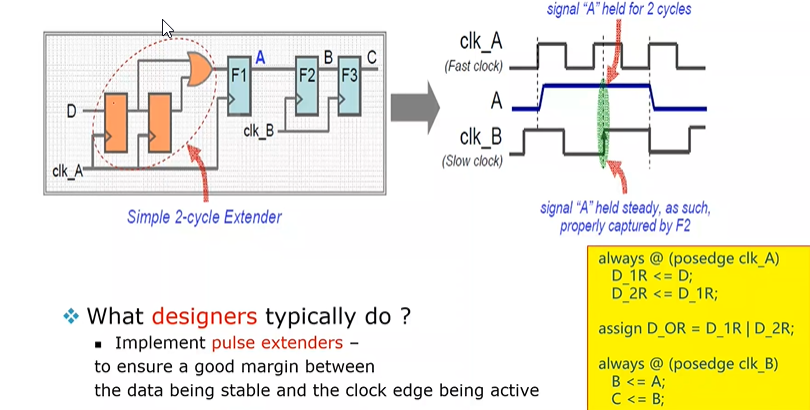

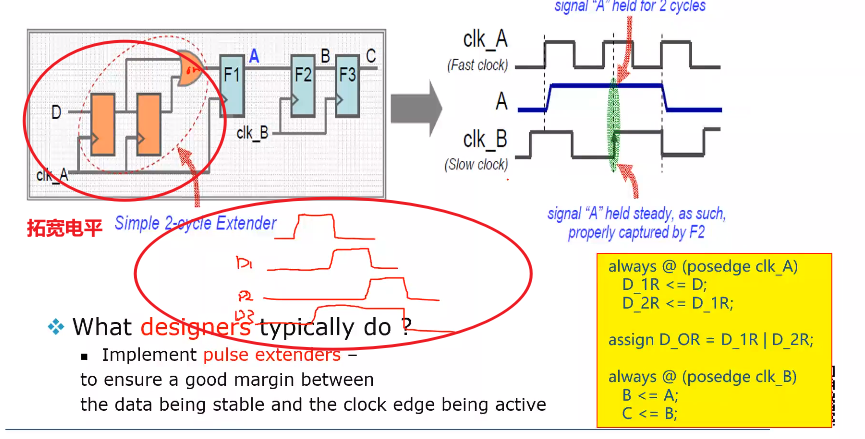

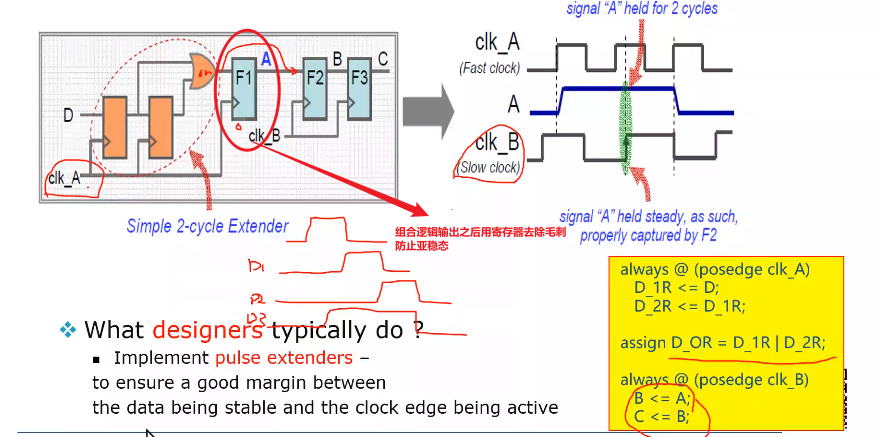

Data hold问题

时钟从快时钟域传递到慢时钟域,由于快时钟域信号窄,可能导致数据丢失

-

当clkA采样clkB的时候,clkB可能已经为0了,解决方式就是对于快的时钟域进行一个展宽

-

实现方式:将快时钟经过两个同步寄存器进行打拍之后,使用一个或门将第一级寄存器输出的信号和第二级寄存器输出的信号连接起来,信号拓宽之后,就可以被捕捉到

-

F1的作用:信号经过组合逻辑之后会出现毛刺现象,为了让信号更加干净,使用一级寄存器将其过滤掉

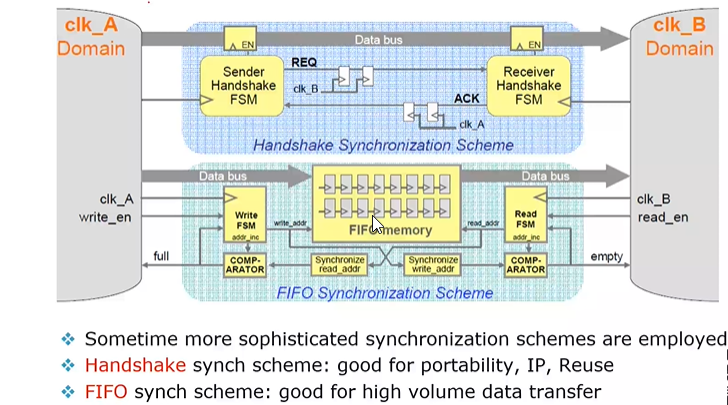

Design Intent(handshake,FIFO)

- 如果传递数据总线data-bus,传递数据,传递的数据之间不是加一和减一的关系,可以使用两种解决方式握手或者是异步FIFO

- 握手:首先数据不经过处理,原数据传递过去,传递的是enable信号;REQ拉高表示data准备好了(数据稳定了),将REQ经过两级打拍器传递到接收端,接收端接收到REQ之后,就可以进行采样数据了;接收端拿到数据之后,还要告诉发送端已经拿到了数据(ACK),发送端拿到ACK信号之后,就可以进行下一组数据的传输

- 握手传递的是1bit信号,优点是面积小,缺点是传递效率不高,传递速度慢

- 异步FIFO:将数据写到FIFO中,将读写指针进行一个同步;优点是性能比较高,缺点是面积较大

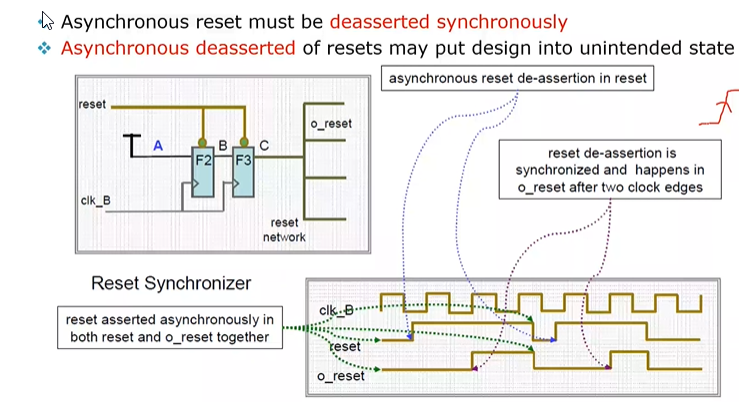

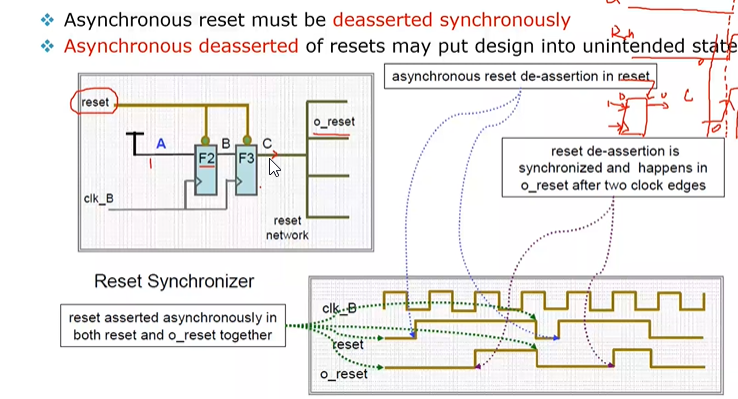

Reset Synchronization

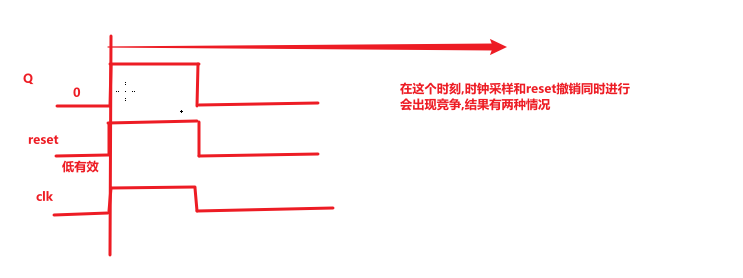

比如时钟是上升沿有效的时钟,假设时钟要去采样一个值,寄存器的输入是1,如果复位信号是低电平有效;在某个时刻,复位信号和时钟同时从0到1跳变,会出现竞争;复位先撤销,时钟先采样再进行复位,Q为1,复位信号撤销的比较晚,就是先复位后采样,Q端为0,出现两种不同的结果(在一个时间点内同时发生,会出现亚稳态)

时钟上升沿之前,复位的撤销需要保持稳定,时钟有效沿之后的一段时间,时钟的复位也需要保持一段时间,类似于setup time和hold time

异步复位:时钟有效沿和reset复位信号是没有关系的

异步复位信号转变为同步复位:就是将reset信号和时钟产生一个相位关系,使用两级寄存器进行同步

一些问题

- 同步时钟域(可能不是一个时钟,但是是同源的时钟,频率和相位是有一定关系的)和异步时钟域(时钟频率和相位是没有关系的)

- 同步跨时钟域不一定是安全的,100MHz与50MHz时钟域跨时钟域,会造成数据丢失

- 列举两个CDC问题

- 亚稳态问题是和时钟频率有关的

- STA检查不到CDC问题

- CTS(clock tree sysnthesis)是PR之间的一个过程,是不能解决跨时钟域问题的

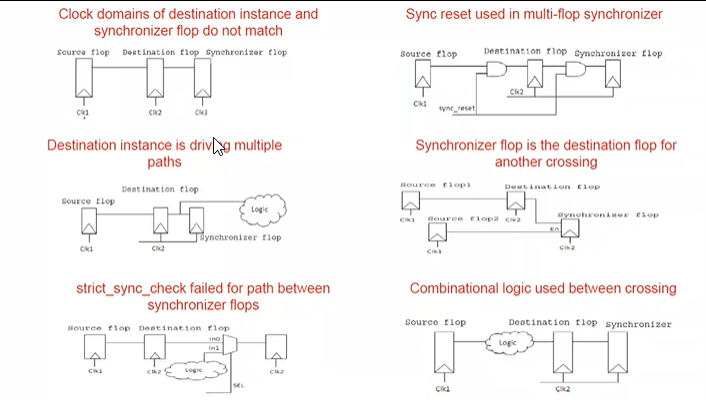

- 三个时钟域有问题

- 发射时钟域不能经过组合逻辑,加大亚稳态风险

- 两个时钟域之间重汇聚问题

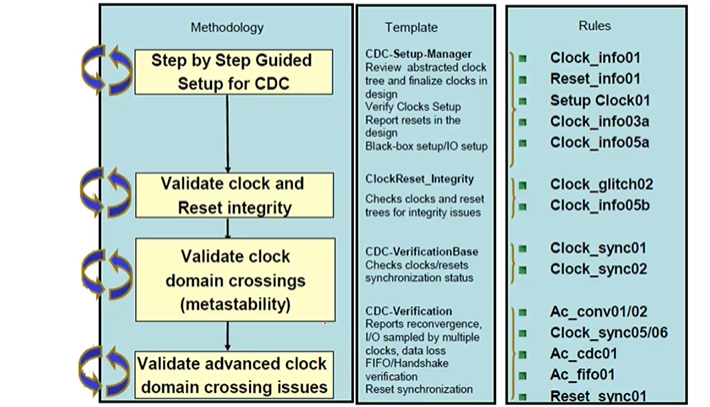

CDC Tool Flow

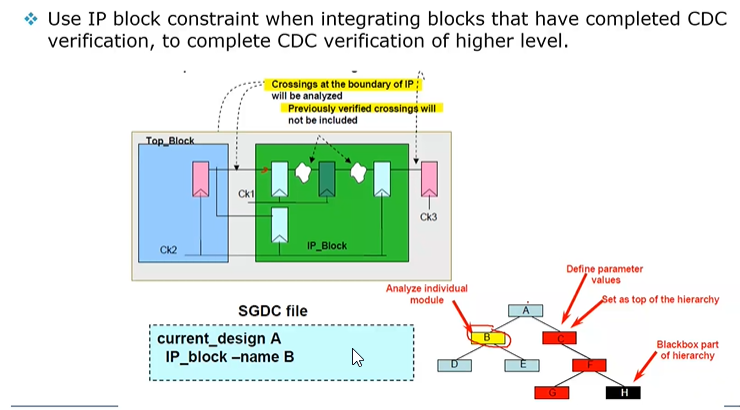

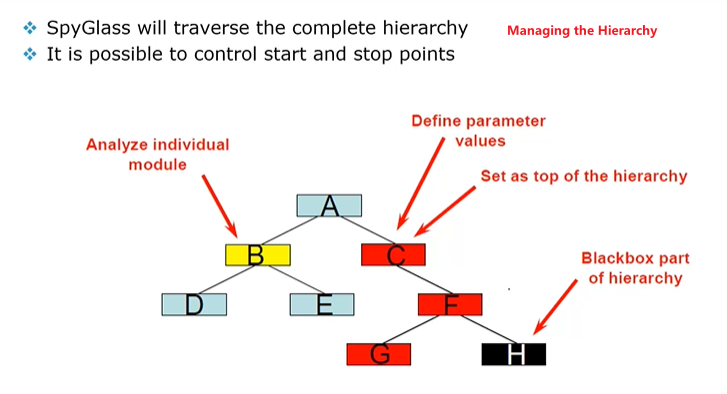

CDC Recommanded Methodology

分治策略,将大模块分为几个小的子模块,先对子模块进行检查