09-Verilog-并发线程

Verilog-线程

并发线程

verilog和C语言有一个最大的不同就是并发性

- 并发--同时进行的过程

module tb_test;

int a;

initial begin

a = 1;

a = 2;

a = 3;

end

initial begin

A1

#1

//a = 1;

end

initial begin

B1

#1

//a = 2;

B2

end

initial begin

C1

#1

C2

end

initial begin

D1

#1

D2

end

endmodule

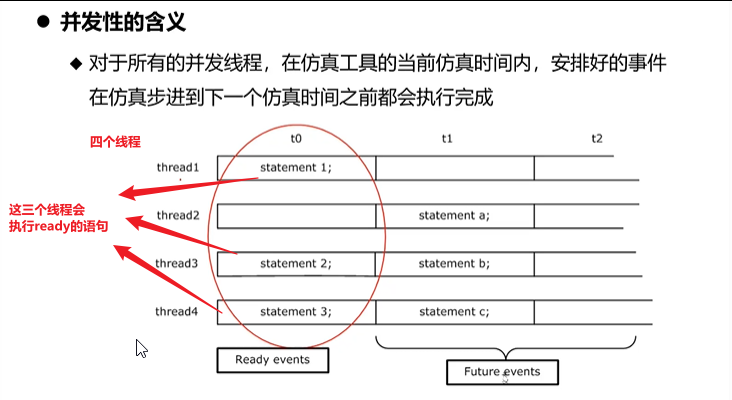

- initial begin end是并发的编程,在0时刻开始执行

- 这里的四个initial begin就相当于上面图中的四个线程thread

- initial是同时执行的,没有先后顺序

- 如果两个initial在同一个时刻对于同一个变量a进行赋值,结果是不确定的,取决于两个线程谁先抢到a

module tb_test;

int a;

initial begin

a = 1; //t0

a = 2; //t0

a = 3; //t0 都是在t0时间点执行的,但是在t0这个时间点,从上到下执行

#1; //语句执行到a = 3得时候,下一条为延迟,程序会等待

end

endmodule

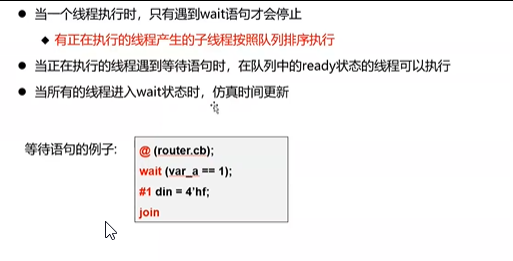

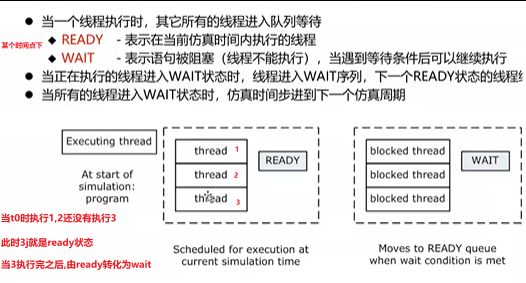

- 一个环境中有多个线程,会分为ready和wait状态的线程

- ready状态就是当前状态还没有执行的线程,wait就是当前时刻下会被阻塞的线程,等待其他线程继续执行

- 当正在执行的线程进入wait状态时,下一个ready状态的线程继续执行

module tb_test;

int a ;

initial begin

a = 1; // 从to时刻开始执行a=1,a=2,a=3,这三条语句没执行完,这个线程处于ready状态

a = 2;

a = 3;

#1

end

initial begin

#1 // t0时刻不执行任何操作,需要等待上面的线程在t0时刻的代码执行完毕之后,两个线程一起进行延迟1个时间单位

end // 在t0时刻,这个线程处于wait状态

// 当第一线程执行完a=1,a=2,a=3三个语句之后,会从ready状态转变为wait状态,此时所有的线程都处于wait状态,进行下一个仿真周期

// 延迟1个时间单位

并发语句合集

- initial 语句在整个仿真事件内只执行一次,initial语句都是并发的

- always语句一直在执行,可以对于电路进行建模,always也是并发的

- assign可以对于组合电路进行建模,assign语句都是并发的

- begin ... end 内部语句从上到下依次执行

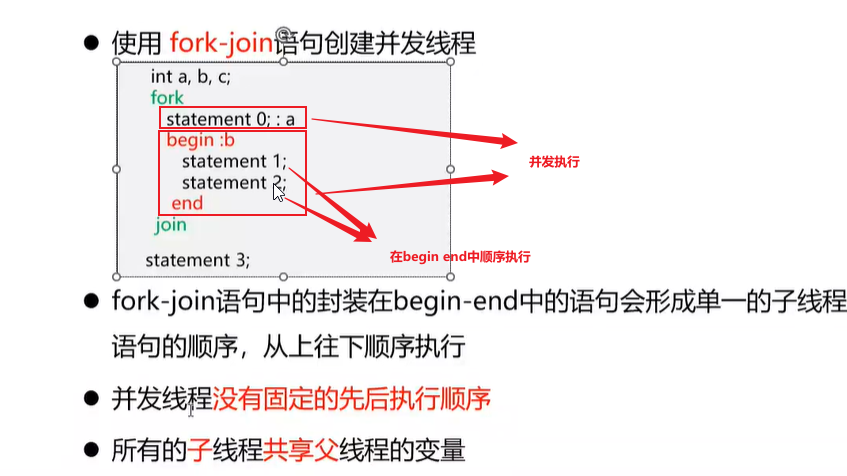

- fork ... join 内部语句并发执行,同一时刻同时执行,与时间无关

int a,b,c;

fork

statement 0;

begin

statement 1;

statement 2;

end

join

statement 3;