05-Verilog基础语法_4

Verilog基础语法

Mixed Model(混合设计模型)

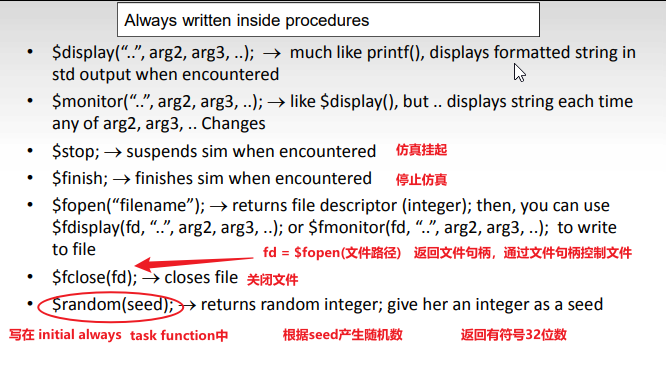

System Tasks(系统任务,系统函数)

- 用随机数驱动验证

fd = $fopen("文件路径及文件名")

// 将含有参数的字符串写到fd打开的文件中

$fdisplay(fd,"xxx",arg1,arg2,arg3...)

// 关闭文件

$fclose(fd)

$random 返回32bit 有符号随机整数

// 范围 -(b-1) - (b-1)

num = $random % b

// 范围:0 - (b-1)

// num = {$random} % b;

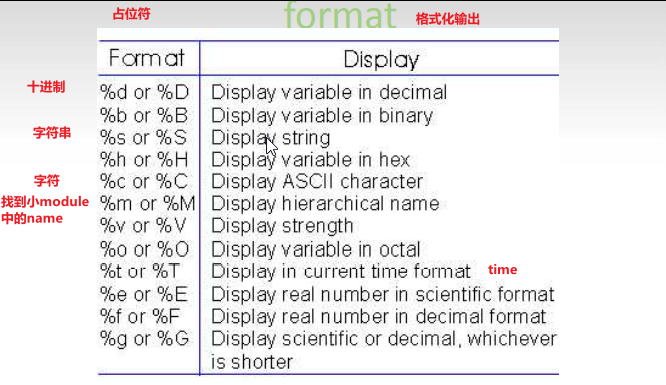

格式化输出

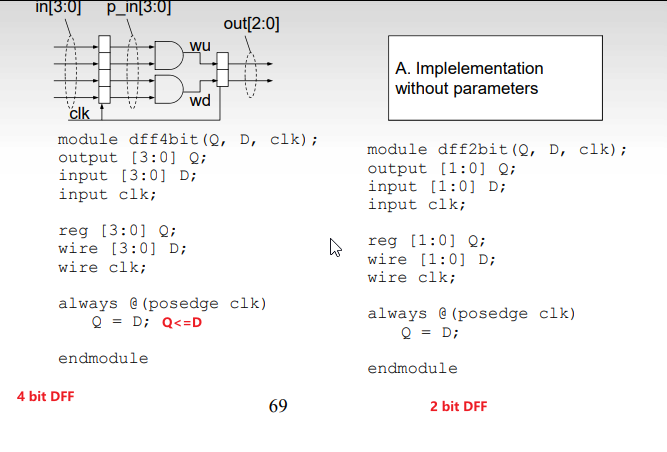

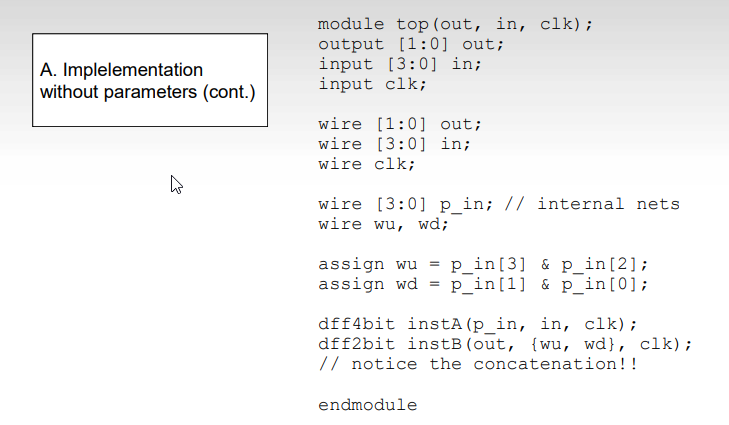

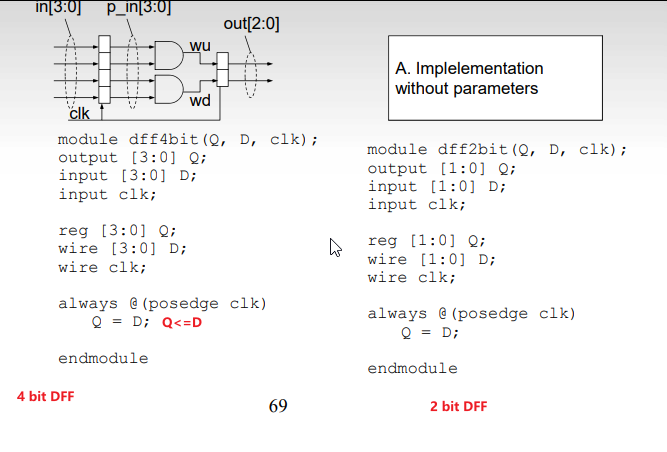

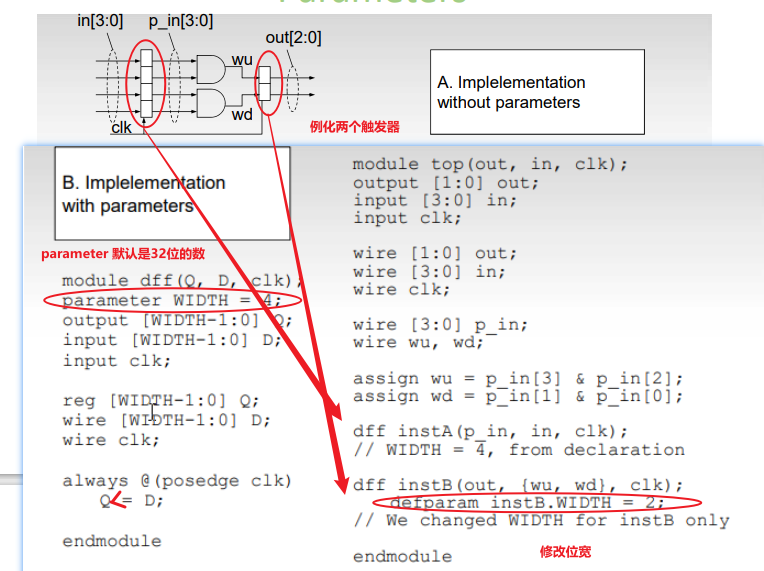

parameter

-

参数化定义,比如设计一个四位的DFF和2位的DFF,位宽不同,可以将位宽写成参数形式,在下次进行设计的时候只需要修改位宽就可以了。

-

使用参数化设计

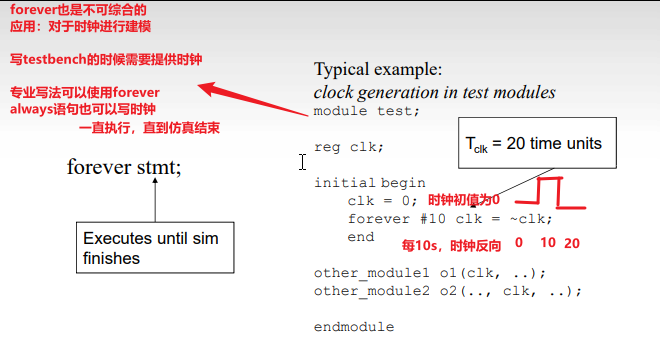

Testbench

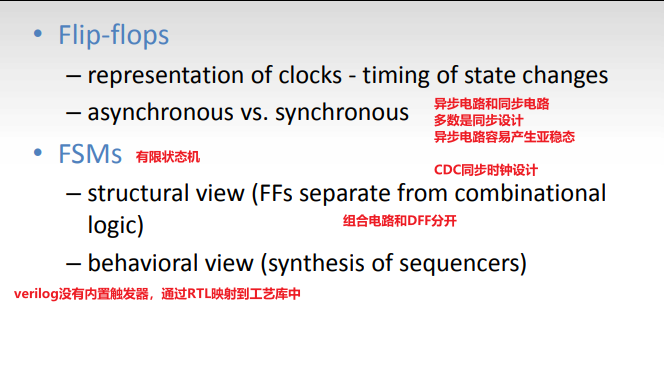

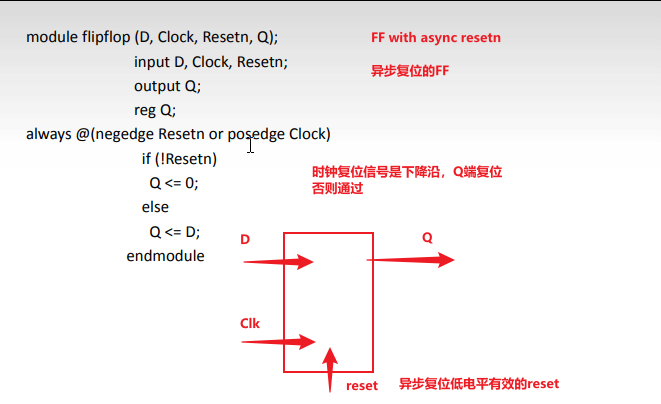

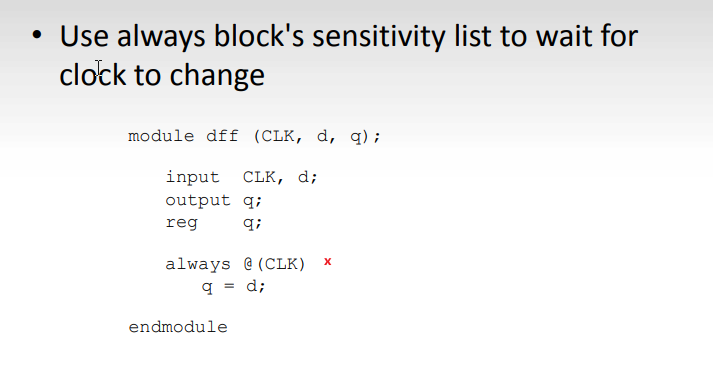

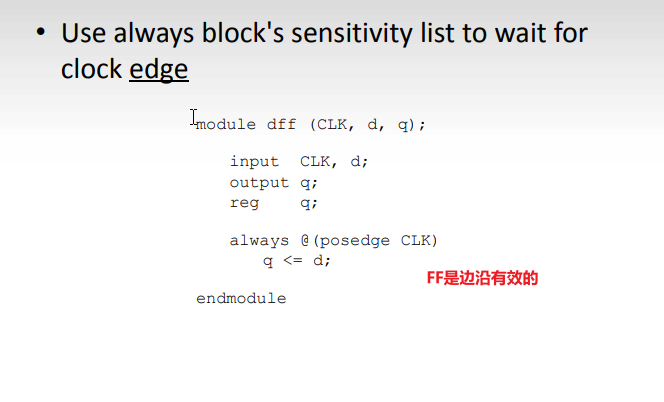

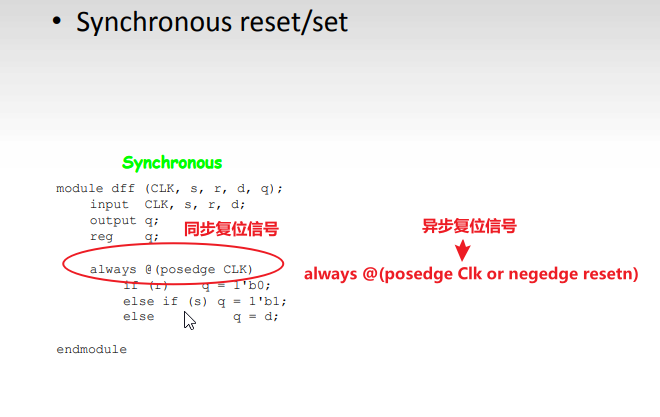

FFs & latch

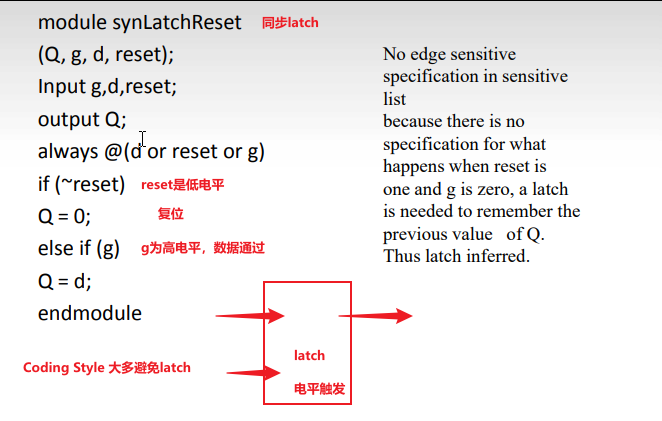

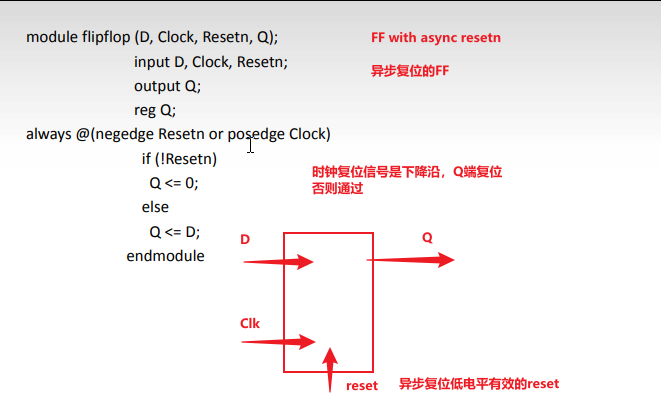

- DFF和Latch建模区别

always @(posedge) // 参数列表有上升沿

if(rst_n)

Q <= 0;

else

Q <= D;

always @(rst_n,Q,d,g) // 参数列表没有上升沿

if(rst_n)

Q <= 0;

else if(g) // if g == 1的时候数据通过,g != 1的时候数据锁存,就形成了锁存器

Q <= d;

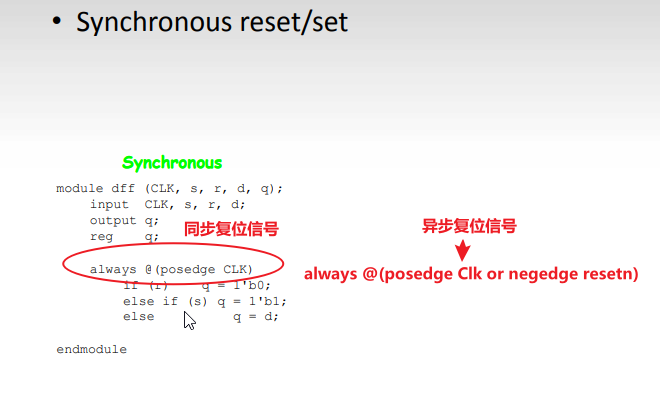

- 同步复位信号,同步在Clk的上升沿上

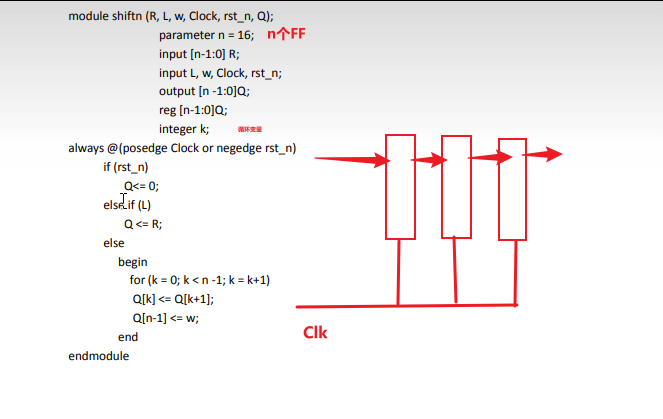

- 移位寄存器

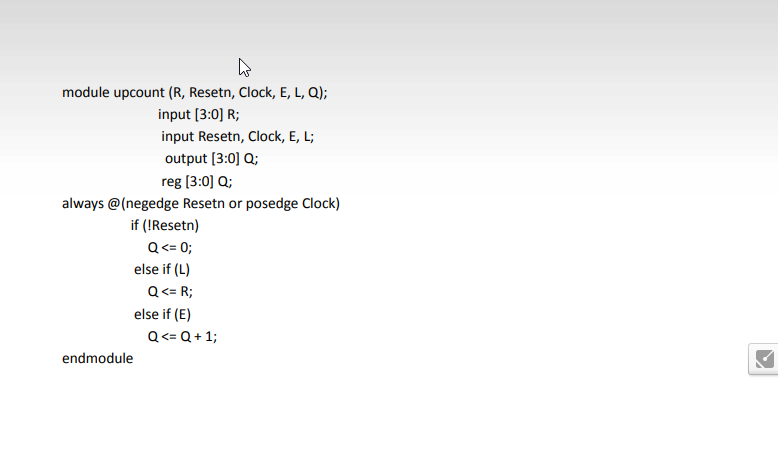

upper counter with load value

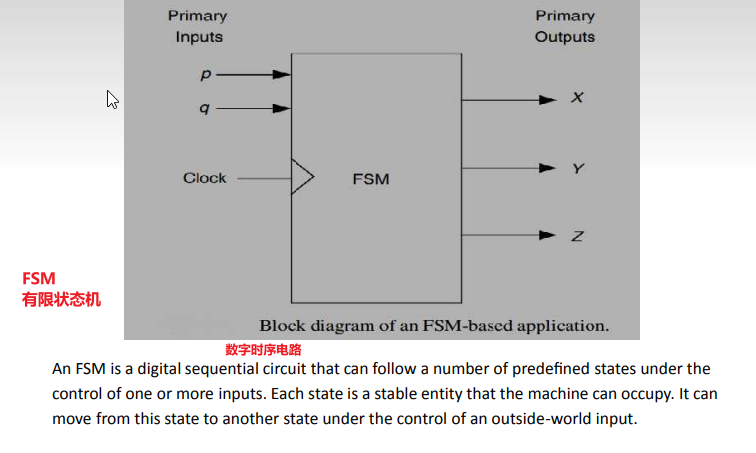

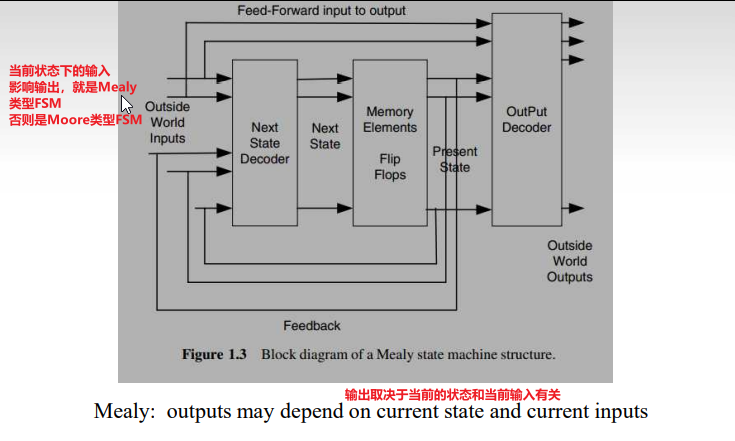

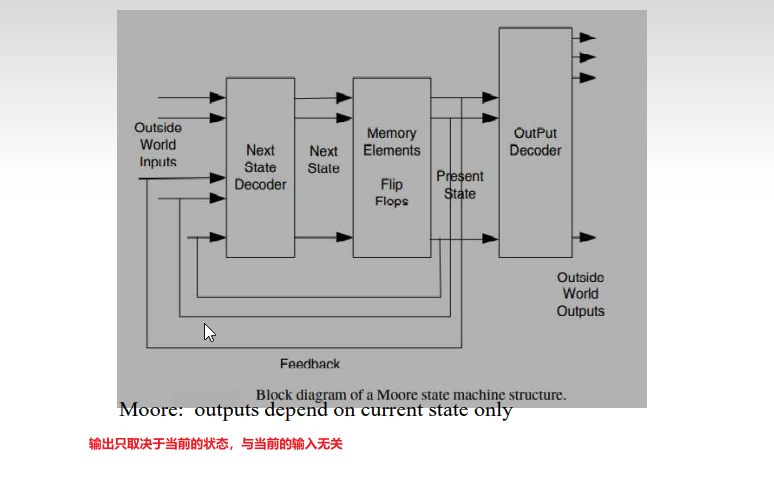

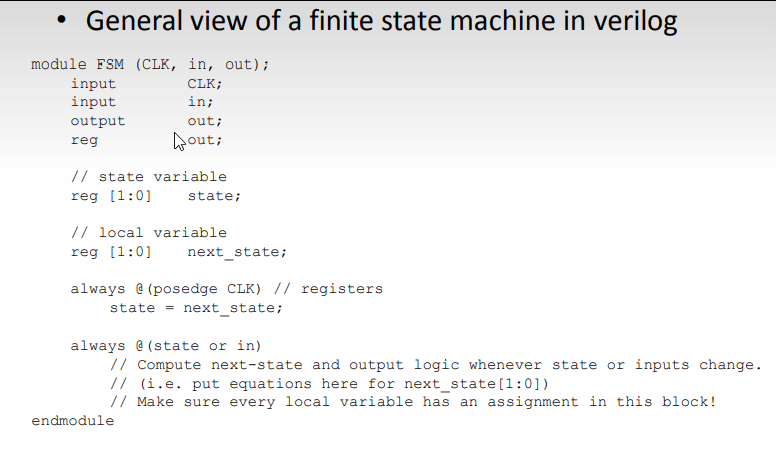

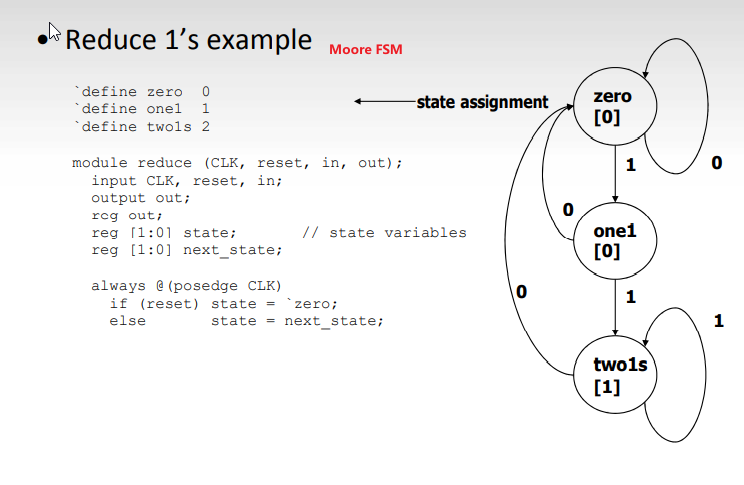

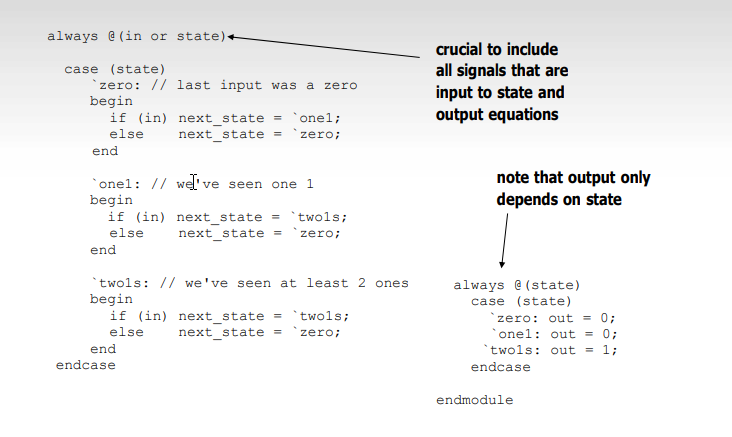

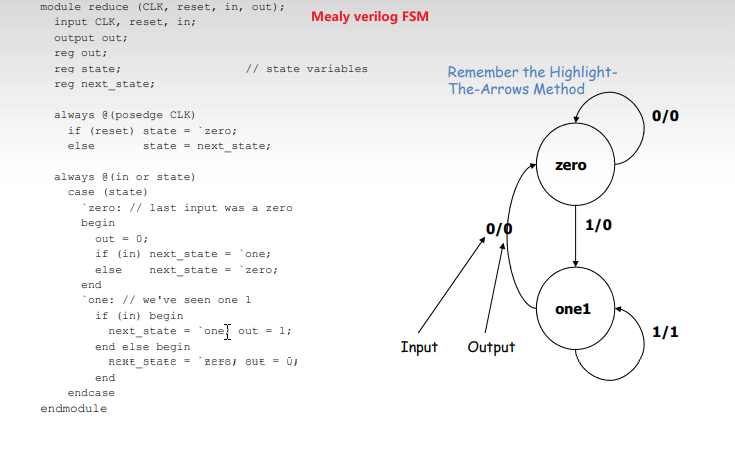

FSM(有限状态机)

- 有限状态机一般写为三段式

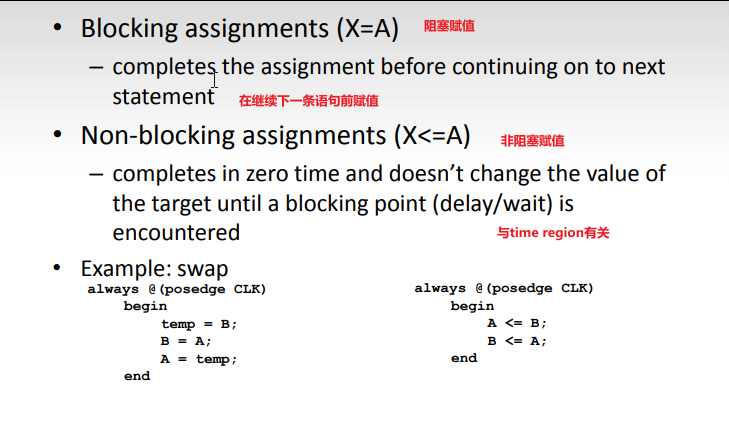

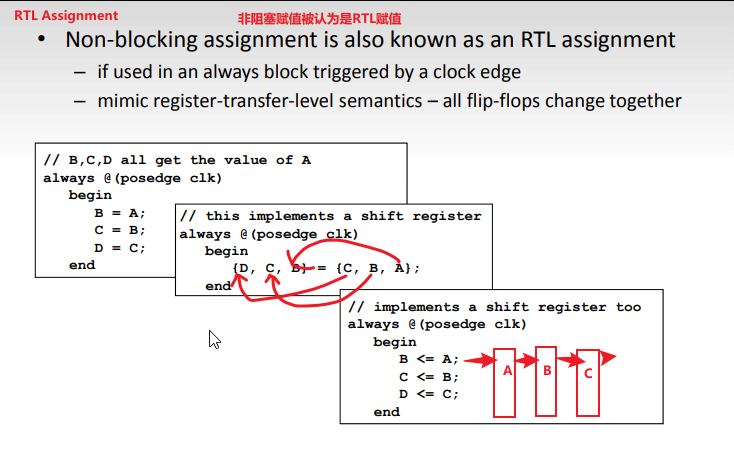

Blocking and Non-Blocking Assignments(阻塞赋值和非阻塞赋值)