29-组合逻辑集成电路-算术运算电路

算术运算电路

1.半加器和全加器

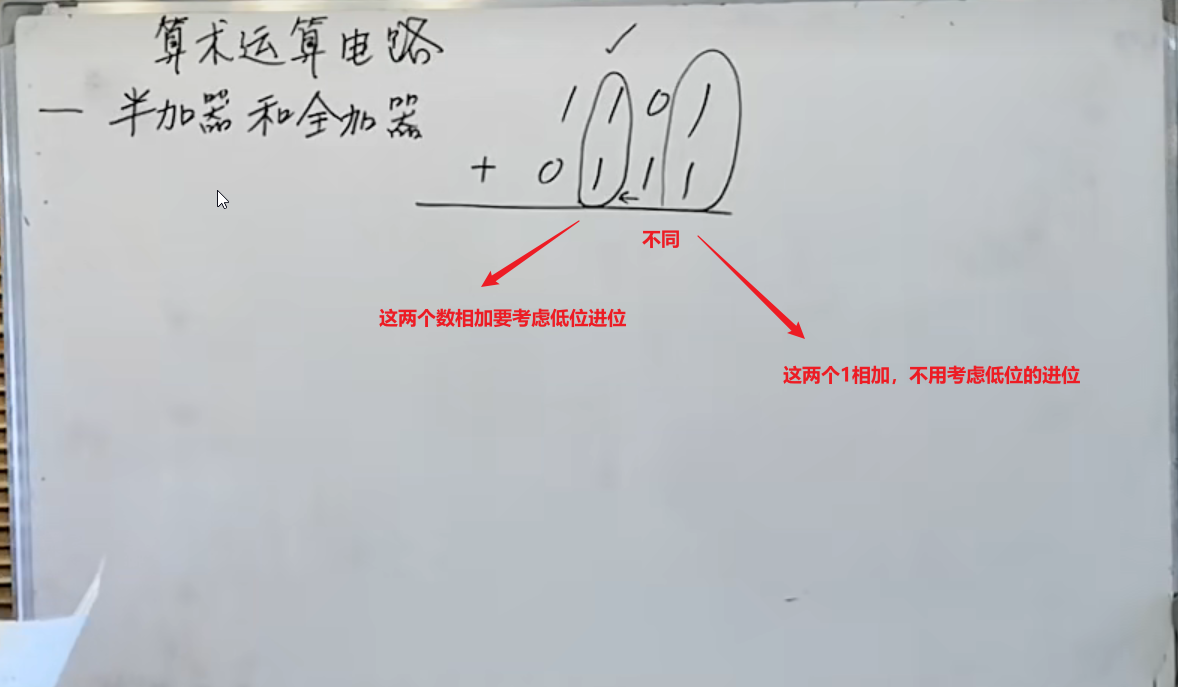

半加器:不考虑低位进位,两个输入

全加器:考虑低位进位,三个输入

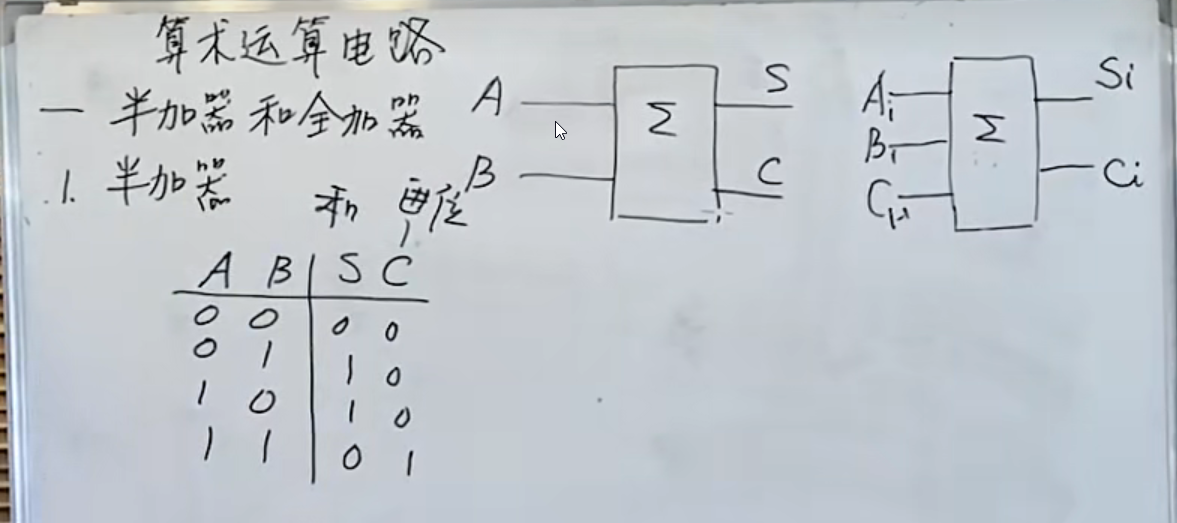

1.1半加器HA

1.2全加器

1.3一位半加器

真值表

表达式

门电路实现

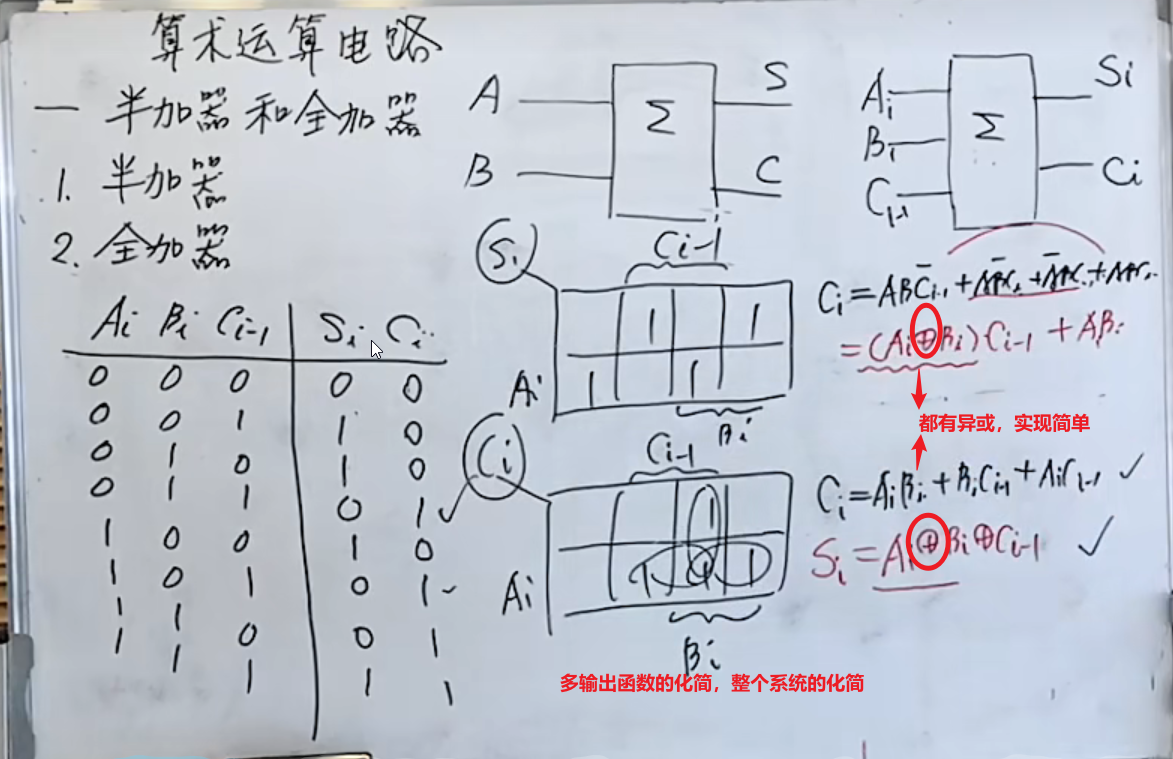

1.4一位全加器

真值表

表达式

门电路实现全加器

用半加器实现全加器

1.5多位加法器

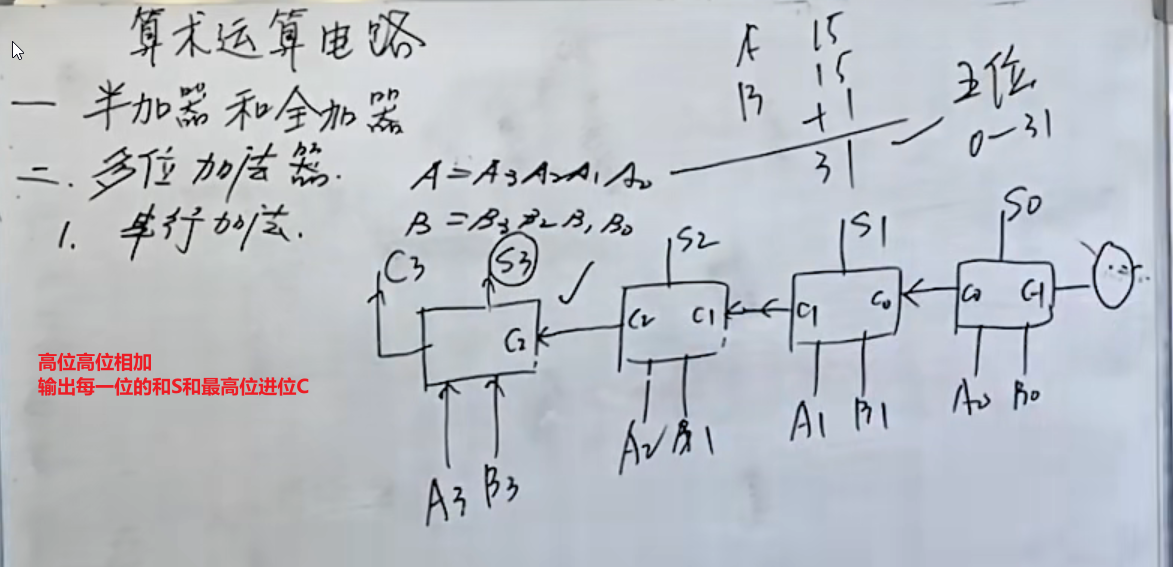

1.5.1 串行加法

- 多位加法器,每一位都要使用一个一位加法器

- 两个四位数相加,最多为五位

- 串行加法器,速度较慢

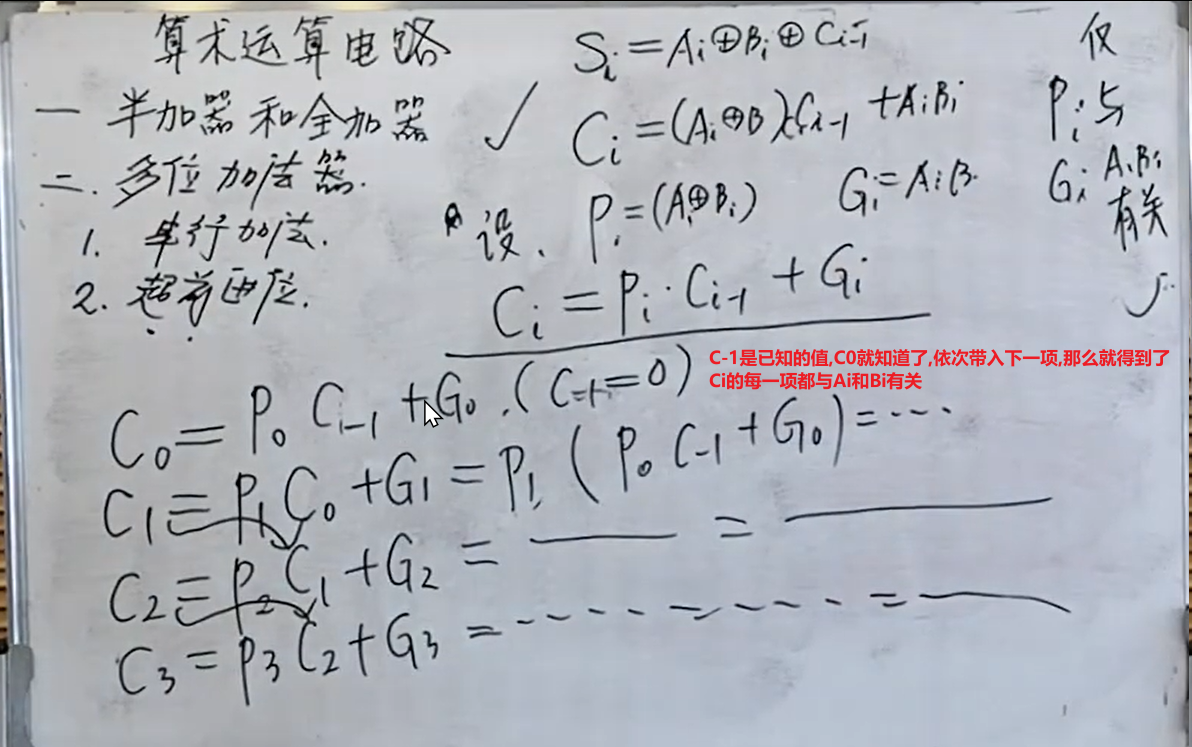

1.5.2 超前进位

- 串行进位,低位运算结果出来之后才能知道进位,进行计算的速度较慢;如果两个多位加进来之后,直接知道每一位对应的进位就可以直接进行计算,加快计算速度

在AB给出之后,Pi和Gi立即就可以知道,Ci-1可能还不知道

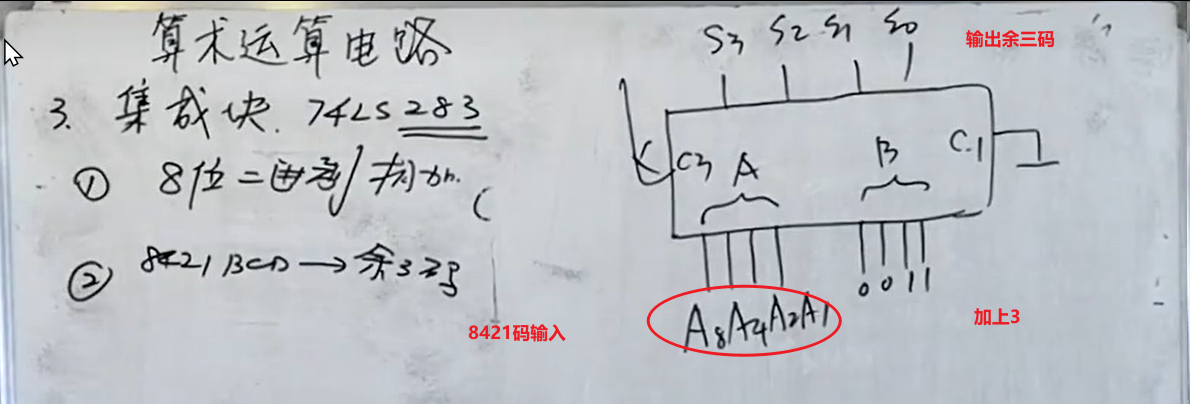

2.集成块74LS283

2.1两个8位二进制数相加

2.2 8421转化为余三码

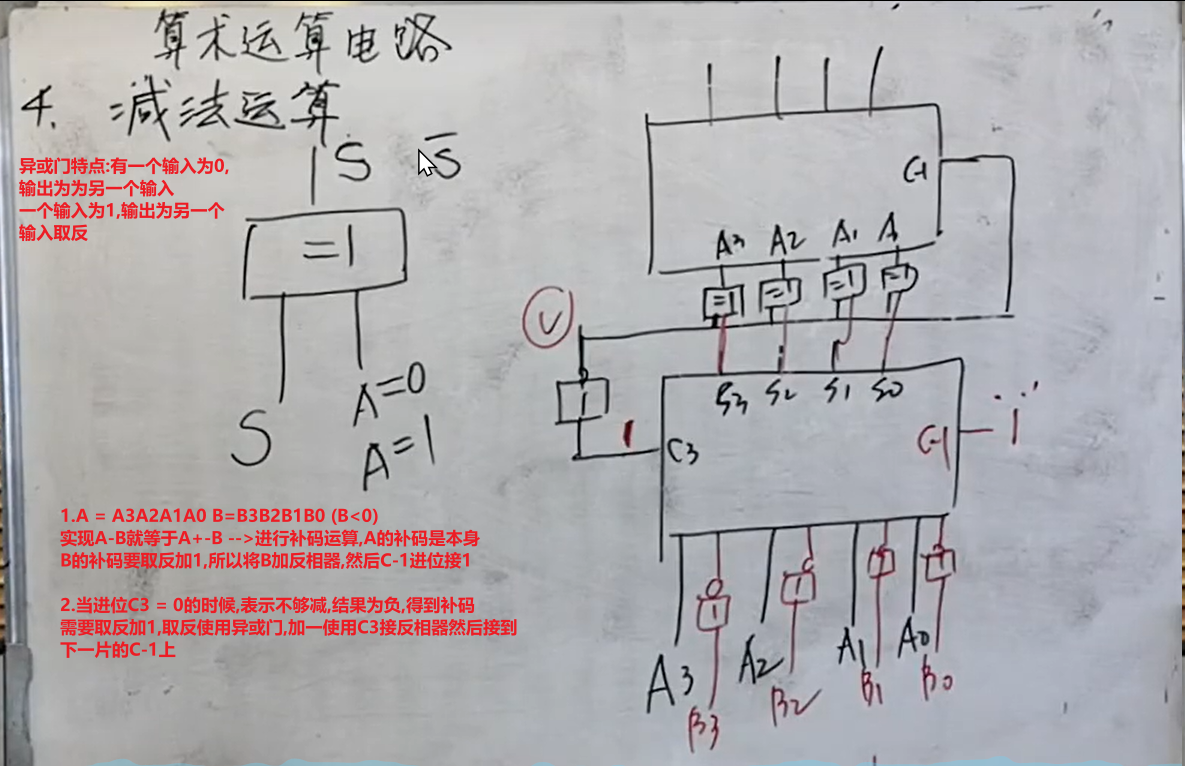

3.减法器

- 进位为1,得到的是原码;进位为负的得到的是补码