01-逻辑仿真工具VCS使用

1 逻辑仿真工具VCS的使用

在书写完成RTL代码之后,确保自己书写的代码和自己想要的逻辑是一致的。

VCS是synopsys公司下的的仿真工具。

1 VCS仿真过程

编译-->仿真-->debug/查看波形

vcs

1.1.1 编译

vcs -sverilog -debug_all full.adder full_adder_tb.v -l com.log

- vcs--是逻辑仿真工具EDA工具的编译源代码命令

- -sverilog--编译命令选项,识别system verilog语法

- -debug_all--编译选项,保存所有的debug信息

- -l com.log--编译选项,将编译过程生成的日志写入com.log文件

- 编译之后会生成simv,simv文件可以进行直接执行

//执行simv文件,生成vpd文件

./simv -l sim.log

//打开vpd文件的图形界面

dve -vpd vcdplus.vpd &

1.1.2 图形界面仿真

- 启动图形界面

dve &

- &--后台使用dve,不占用当前的terminal

- setup,读入simv文件

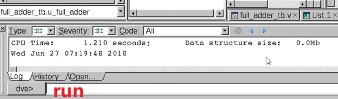

- 输入run执行仿真

- 查看波形

注意:

- 仿真至少有两层,xxx.v及testbench.v

- Hierachy--显示结构,上层为testbench,下层是源代码

2 Verilog Testbench功能

- 产生激励 Generate stimulus--过多长时间给什么样的值

- 将激励输入到待测设计(DUT,design under verification)

- 获取响应 Capture response

- 检查响应的正确性 Check the response for correctness

- 根据验证目标评估验证进度 Measure the progress against the overall verification goals

3 验证一个模块,比如全加器

- 真值表

可以将真值表作为pattern,用于进行验证 - 验证

- 功能完整性

- 穷举法

- 代码覆盖率--所有的代码都在进行仿真的时候用到

3 进行仿真 - 编译

- 仿真

- 查看波形

4 一些概念

输入信号是驱动信号,输出信号是被驱动信号

- 在RTL源代码中

- 如果被驱动信号写到assign语句中,定义为wire型的信号

- Input信号都是wire型,可以省略掉。

- 如果被驱动信号写道always语句块中,定义为reg型的信号

- 在Testbench中

- Testbench中的驱动信号reg

- 驱动信号的类型是reg信号

- 被驱动类型的信号wire类型

注意::进行DUT测试,需要外加Testbench向DUT中灌入一些信号进行测试。所以在DUT中和Testbench中的输入输出信号类型是相反的。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· ollama系列01:轻松3步本地部署deepseek,普通电脑可用

· 25岁的心里话

· 按钮权限的设计及实现