02-RTL代码分析思路

RTL代码分析思路(这里不进行具体代码的分析)

verilog文件是以.v结尾的

1 RTL代码示例

//Date : 2023-01-09

//E-mail : xxxxxx@163.com

//copyright : xxxx

//-------------------------------------------------------------------------------

//module header may includes:

//module name,port,direction,port width and port types

module AndOr {

output X,Y,

input A,B,C

};

assign #10 X = A & B;

assign #10 Y = B | C;

endmodule

- RTL中有内建的and or 一般写& |

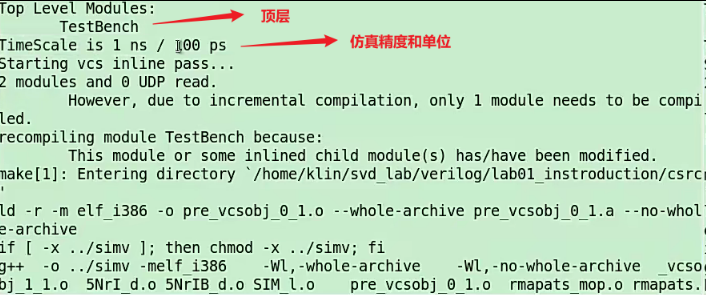

2 使用Makefile进行仿真

Makefile是一个脚本,简单理解为将仿真使用的命令放到脚本中,方便执行

all:compile simulate

compile:

vcs -sverilog -debug_all -timescale=1np/1ps full_adder.v full_adder_tb.v -l com.lg

simulate:

.simv -l sim.log

clean:

@rm -rf csrc DVEfiles simv simv.daidir ucli.key VCS*

@rm -rf *.log *.vpd *.svf *.SDF *Synth *Netlist*

@rm -rf alib-52

make all就会执行all下面的complie和simulate

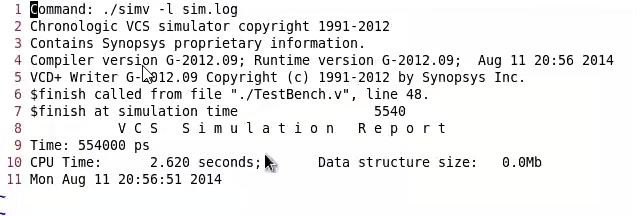

生成sim.log文件

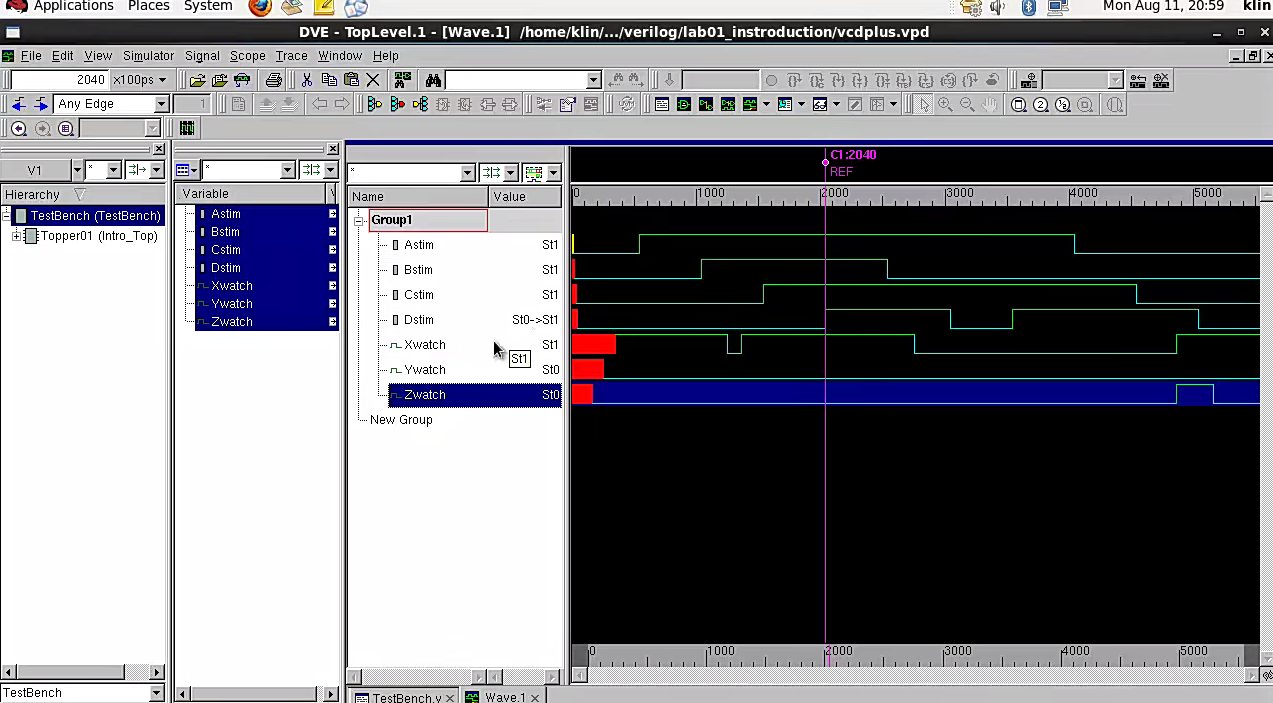

使用 dve查看波形文件

// & 后台运行dve

dve &

设计人员也需要会部分验证

3 进行逻辑综合

3.1 tcl脚本的方式进行逻辑综合

//在linux中使用脚本进行综合

dc_shell -f xxx.tcl

//自动调用design compiler进行综合

- 延时信息--#5 是不可综合的

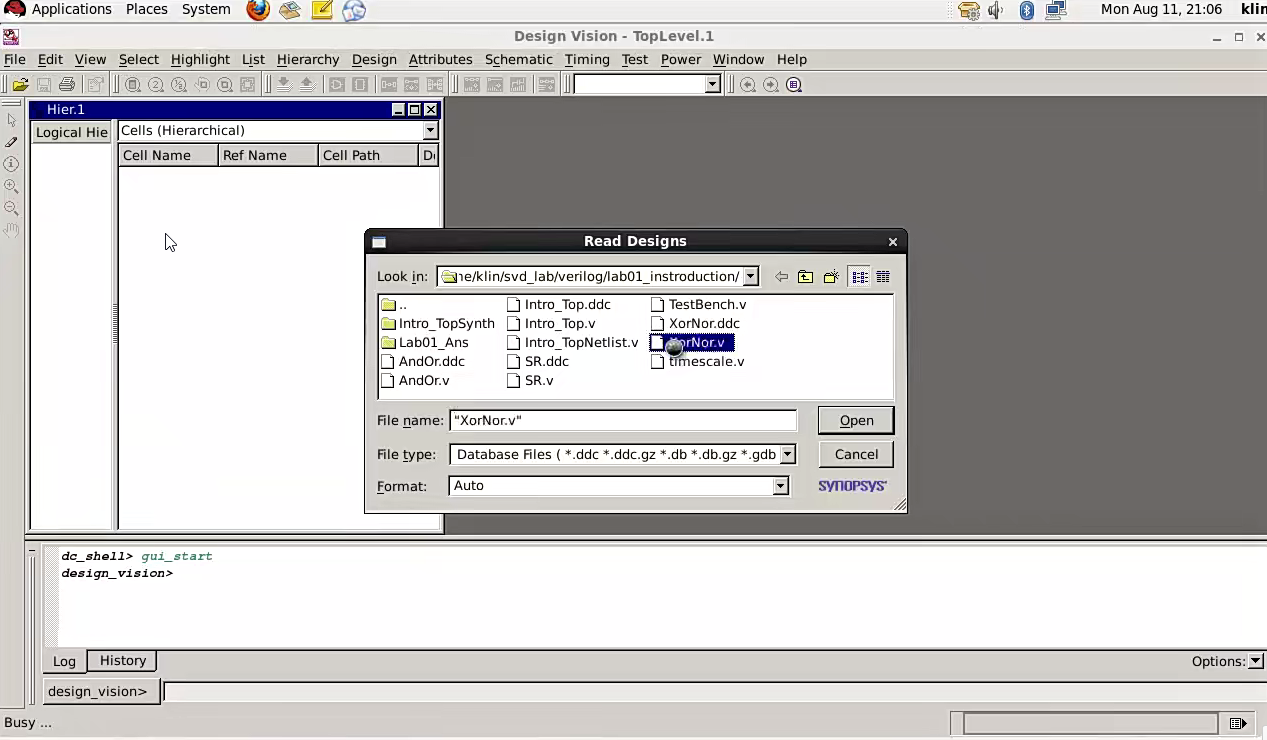

3.2 使用GUI界面方式进行逻辑综合

//调出design compiler的界面工具

design_vision &

详细的过程不在这里进行详细叙述

通过逻辑综合可以看到RTL变成的具体电路

4 一些问题:

- 设计人员需要掌握verilog的testbench,掌握初级的验证

- VCS使用的比较多,使用不同的仿真工具只需要改变工具

- 正常开发的时候通常使用脚本的方式进行仿真和综合,公司中的脚本设计比较完善,就可以直接跑

- 脚本虽好,但是仍然需要进行了解其中的原理

- verdi优点,大型芯片的效率比较高

- 前端设计人员Coding能力和Debug能力,工具使用比较简单

- RTL code在release之前需要进行检查

- 芯片设计人员需要掌握常用的EDA工具