随笔分类 - FPGA

摘要:1.半加器 加法器是数字电路中经常用到的一种基本器件,主要用于两个数或者是多个数相加,加法器又分为半加器(half adder)和全加器(full adder) 半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。 全加器是在半加

阅读全文

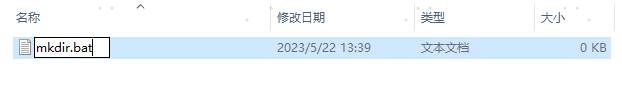

摘要:# **快速创建文件夹的技巧** 1.首先创建文本文档将扩展名更改为**.bt**,**mkdir.bat**  !

阅读全文

摘要:1.译码器 译码器是编码的逆过程,在编码时,每一种二进制代码都赋予了特定的含义,即都代表了一个确定的信号或者是对象;把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器,或者说,译码器可以将输入二机制代码的状态翻译成输出信号,以表示其原来含义的电路 译码器(decoder)是一类

阅读全文

摘要:1.多路选择器 组合逻辑是Verilog设计中的一个重要组成部分,从电路本质上讲,组合逻辑电路的特点是输出信号只是当前时刻输入信号的函数,与其他时刻的输入状态无关,无存储电路,也没有反馈电路 组合逻辑电路输出信号的电平变化仅仅与输入信号的电平变化有关,不涉及信号跳变沿的处理 多路选择器,是数据选择器

阅读全文

摘要:1.FPGA设计流程 1.设计规划 对项目需求了解,划分子功能模块,子功能模块的输入输出信号及通信关系 2.波形绘制 了解子模块的功能,画出框图,搞清楚如何通过输入信号得到输出信号,进而绘制波形图 3.代码编写 参照绘制的波形图 4.代码编译 检查代码中的语法错误 5.逻辑仿真 编写仿真代码,对ve

阅读全文

摘要:# 1.开发环境搭建 需要使用的软件: * QuartusII * ModelSim * Visio * Notepad++ # 2.初识Verilog ## 2.1 Verilog HDL简介 * Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表

阅读全文

摘要:1.module module有出入接口,输出接口 module有时钟和复位 // input clock; rest_n; // n表示低电平复位 //output o_data; module module_a( // module是关键字表示声明一个模块 // module module名 /

阅读全文