随笔分类 - Verilog基础

掌握Verilog基础知识

摘要:Agenda 目的 Verilog概述 Verilog建模 模块 模块组成 书写建议 时延 Verilog基本语法 标识符 可读性 注释 空格 数据类型 操作数 运算符 条件语句 循环语句 函数 Verilog for design module 端口 数据类型 例化模块 参数化 行为描述 过程赋值

阅读全文

摘要:Verilog必须掌握 逻辑仿真工具(VCS)和逻辑综合工具(DC) AndOR module AndOr( output X,Y, input A,B,C ); // A B进行按位与运算 assign #10 X = A & B; // B C按位进行或运算 assign #10 Y = B |

阅读全文

摘要:Verilog Coding Style 1.为什么需要Coding Style 可综合性 - 代码需要综合成网表,如果写了一些不可综合的代码,会出现错误 可读性,代码通常有多个版本,所以需要保证代码的可读性 保证代码质量,方便后续的综合以及后端的布局布线 2.头文件 使用统一的文件头,其中包括:

阅读全文

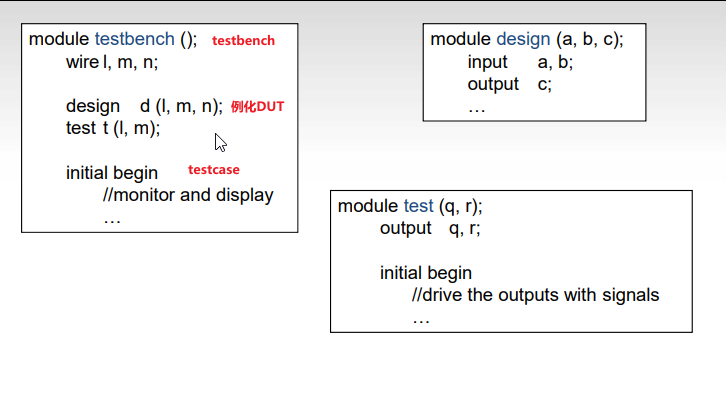

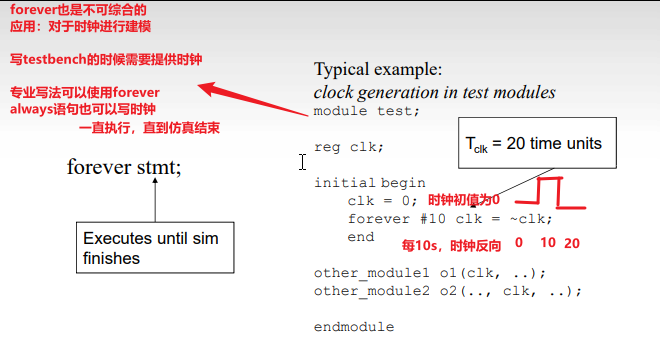

摘要:Verilog for Verification 1.引言 Testbench也是一个模块(module...endmodule) Testbench没有输入和输出,因为它是一个闭环,自己产生激励,灌给module,module输出响应,testbench会捕捉响应,进行比较,自己在自己内部形成闭环

阅读全文

摘要:Verilog for Design 设计人员知道写的RTL可以综合成么样的电路 设计人员对于硬件系统进行描述 验证人员搭建验证环境对设计人员描述的硬件系统进行验证 对Standcell,模拟/定制IP(USB PHY/SRAM等)进行行为级描述 if-else - 可以综合成二选一的mux cas

阅读全文

摘要:同步FIFO和异步FIFO FIFO分为一个同步FIFO,一个异步FIFO,FIFO有读口和写口 读写时钟是一个,就是同步FIFO;读写时钟不是一个,异步FIFO IP核设计中,一般使用同步FIFO设计 SOC设计或者跨时钟域的内容使用异步FIFO RAM FIFO中的数据,存储在寄存器中或者是SR

阅读全文

摘要:# 有限状态机 写RTL的时候,实现一个功能的时候有很多种方法 1. 将系统划分为多个状态,状态之间有状态的转移,第一步,第二步......形成有限状态机 2. 流水线技术设计,从输入到输出有多个步骤,多个步骤可以并行执行 有限状态机,状态是有限的,比如8个状态,16个状态等,在进行设计的时候,状态

阅读全文

摘要:# 经典组合和时序电路 HDL的主流语言 * VHDL * Verilog * System Verilog 硬件描述层次 * 门级(gate-level) * 寄存器传输级(RTL-Level) * 行为级 RTL:Register Transfer Level * 可综合性,写的代码要可综合 *

阅读全文

摘要:Verilog-线程 并发线程 verilog和C语言有一个最大的不同就是并发性 并发--同时进行的过程 module tb_test; int a; initial begin a = 1; a = 2; a = 3; end initial begin A1 #1 //a = 1; end in

阅读全文

摘要:任务Task和函数Function 类似于c语言中的函数 Task task 含有input\output\inout语句 task消耗仿真时间 task中可以写延迟:#20 延迟20个仿真时间单位 时钟周期 @(posedge Clk) 等待下一个时钟周期上升沿 事件 @event 等待某一个事件

阅读全文

摘要:一.数据类型 二值逻辑变量 bit 不赋值的时候,变量初始默认为0 x或z的值会转变为0 bit vector--bit矢量 bit [msb,lsb] variable_name = [initial_value] 位宽:最高位为MSB,最低位为LSB 不加任何描述,默认为unsigned,无符号

阅读全文

摘要:## How to build and test a module    ## System Tasks(系统任

阅读全文

摘要:# Module Module是verilog中的关键字,是对电路建模的最小单元。verilog中构建一个电路,对于一个硬件进行描述在module中进行。  verilog文件是以**.v**结尾的 1 RTL代码示例 //Date : 2023-01-09 //E-mail : xxxxxx@163.com //copyright : xxxx // //module header may include

阅读全文

摘要:# Verilog RTL编程实践 在进行数字IC设计过程中,RTL coding能力是非常重要的。结合逻辑仿真(VCS)和逻辑综合(Design Compiler)工具。看RTL。 ## 1 ASIC Design Flow 1. IDEA 2. Design specification 3. D

阅读全文