一步步分析MIPS数据通路(单周期)

一步步分析MIPS数据通路

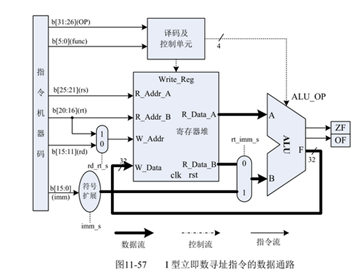

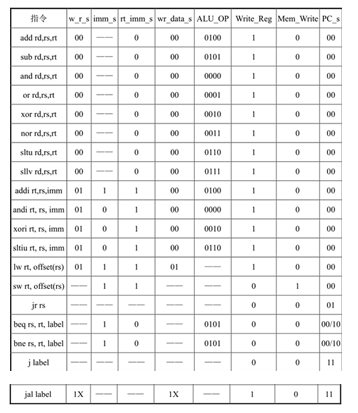

R型指令CPU数据通路:

此时的控制信号有:ALU_OP , Write_Reg。

如何确定单周期CPU完成指令的过程?

-

分析时序电路和组合逻辑:时序电路(需要clk,可以从图上看到clk有四处):指令存储器的读操作、PC值更新、寄存器写操作、标志寄存器的更新。 组合逻辑(不需要clk):寄存器读操作、ALU运算。

-

设计时序:clk上升沿,启动指令存储器依据PC读出指令;

clk高电平(组合逻辑操作):PC自增、指令译码、寄存器读、ALU运算。

Clk下降沿:目的寄存器的写入、PC值更新、标志寄存器更新。

从图中可以看出,红框为clk产生处,只有指令存储器的取指令部分是正的clk,PC的自增、标志寄存器的更新、寄存器堆的写入都是clk#,故可以从图中获得设计的信息。

-

数据通路(通过一条指令来说明):(clk上升)使用当前PC寄存器的值取出一条指令

(clk高电平)指令送到IR寄存器,分段直接送往译码单元和寄存器堆,获得ALU_OP和Write_Reg信号。ALU接收到ALU_OP对两个读出的数据进行运算,同时计算标志寄存器的值。

(clk下降沿)同时激活PC自增、目标寄存器的写入、标志寄存器的更新,根据高电平生成的控制信号来确定是否写入。

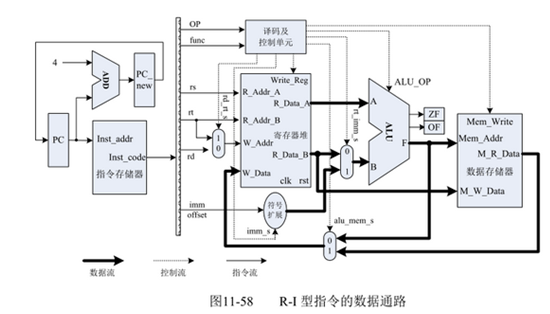

添加I型指令后的数据通路:

首先确定为什么要修改和要修改什么?I型指令不像R型只能完成算术运算,其作用更多是用于数据传输、分支(转移)、访存。访存决定了需要增加到存储器的数据通路。分支跳转决定了需要有对PC进行修改的手段。同时,I型指令格式的不同也代表要对指令寄存器IR指令分段时的结构进行修改。

由于引入了立即数(偏移量)字段,其指令格式从655556(前三个5是寄存器)的分段变成了655 16的形式。只有两个5,因此目的寄存器从原先的第三个5变成了第二个5.添加了控制信号rd_rt_s(1时W_Addr变成rt,否则仍然是rt)来修改W_Data,以控制写入位置写入的寄存器。同时由于要同时兼容R型和I型指令,故把数据的[5:0]同样作为func输入译码,而[15:0]作为立即数imm。为了确定立即数的扩展方式,添加了控制信号imm_s(1则符号扩展,0则0扩展,可以看出新手段往往用1来控制,且命名格式也有规律)。现在,只有两个寄存器,一个作为源、一个作为目的。那么要进行I型指令的运算,另一个源操作数就是扩展后的imm了。于是,添加rt_imm_s(1则imm,0则rt(这里其实指代的是R型指令下rt指向的数据))作为ALU的第二个输入。

还需要解决的问题就是和存储器的交互。在sw(在rs寄存器加上偏移量后指向的地址中写入rt的数据)和lw(取出rs寄存器加上偏移量后的地址指向的数据,再放回到rt寄存器中,因此W_Addr为1)指令中,上面的imm会作为偏移量offset来使用,因此此时imm_s 和rt_imm_s信号都应该置为1(是的,是符号扩展)。通过ALU运算之后,获得需要存放(sw)或者取数(lw)的地址。为了能够表示读还是写入,增加Mem_Write信号(0时为读时为写)。如果是读出数据,那么就要写回到寄存器堆中,由于R型指令(或者I型中的立即数算数指令)是直接把ALU的结果写回寄存器堆,为了控制写回的是哪一数据,添加alu_mem_s信号(0为alu数据,1为存储器mem读出数据)。注意,读可以当作组合逻辑看待(高频时钟),写需要clk(具体看题目中的clk)。

数据通路:以sw为例

(clk上跳沿)指令存储器利用PC读取指令

(clk高电平)指令分段、译码、运算(具体过程同R型)

(clk下跳沿)同时激活PC自增、目标寄存器的写入、标志寄存器的更新。将运算结果写入存储器。

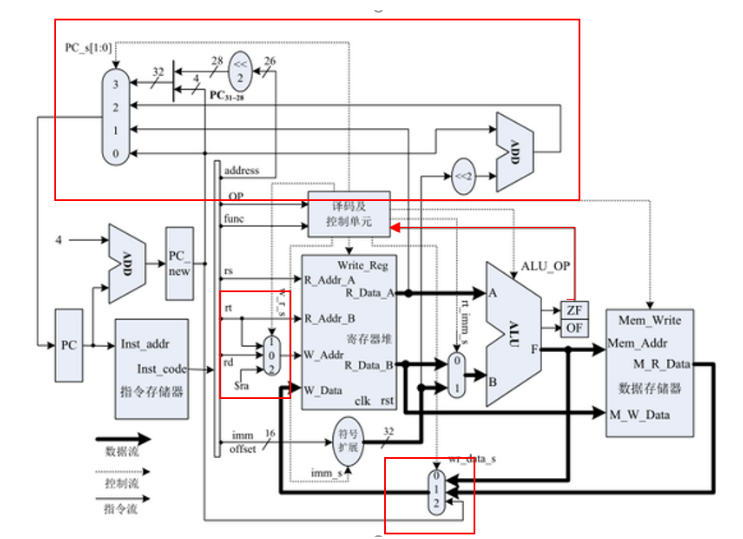

添加转移指令后的数据通路

转移指令主要修改的部件是PC,典型指令有jr(R型指令,无条件跳转),beq(I型指令相等跳转),jal(J型指令,无条件跳转,且当前PC值要存入ra寄存器(一般是堆的高处))。

此处插播子程序调用知识:主程序CALL调用子程序,把PC+4放到堆栈,把新的地址置给PC,运行到RET指令,把堆栈中的PC+4还给PC,然后继续运行。

上图中红色部分是修改的部分。PC的来源从PC_new扩展到了rs(jr指令)、PC+4+offset<<2(beq)、PC+4高四位和指令低26位左移两位拼接。因此需要4选一。

Jr指令的源寄存器应该写为31,因此需要把rd_rt_s改成w_r_s中,添加2作为31号寄存器的地址。同时,由于要把PC+4的值写入寄存器堆,alu_mem_s改名为wr_data_s需要扩展一个2接收PC_new 。

条件转移中PC_s的两种情况:分别对应着转移和不转移。