赋值时'1和'b1有什么区别

历史内容合集

在sv中赋值时,'1和'b1赋值会有什么区别?

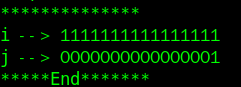

给出一个简单的赋值文件,看看输出结果

module tb;

byte i;

byte j;

initial begin

i = '1;

j = 'b1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

变量i和j都声明为byte型(8 bit),当用'1进行赋值时,所有位均为1;当用'b1进行赋值时,只有最低位是1

这有什么好处呢

我们做个更改

module tb;

parameter SIZE = 8;

bit [SIZE-1 : 0] i;

bit [SIZE-1 : 0] j;

initial begin

i = '1;

j = 'b1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

设置一个参数,此时的输出应和更改之前一致

但如果我们后续更改了参数的数值,比如我们将SIZE的值更改为16,再来看看运行结果

module tb;

parameter SIZE = 16;

bit [SIZE-1 : 0] i;

bit [SIZE-1 : 0] j;

initial begin

i = '1;

j = 'b1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

可以看到,采用'1的赋值方式,无论位宽是多少,都会将所有的位置为1

而如果我们用常见的Verilog赋值方式,当位宽为8 bit时

i = 8'hFF

当位宽改为16 bit时

i = 16'hFFFF

才能实现这个效果,更改时简化了很多步骤

回头看了看Verilog的书,发现其实Verilog也有可以实现这种效果的方法,就是利用补码

i = ~0; //1的补码运算

j = -1; //2的补码运算

放在这个例子中看看运行结果

module tb;

parameter SIZE = 16;

bit [SIZE-1 : 0] i;

bit [SIZE-1 : 0] j;

initial begin

i = ~0;

j = -1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

确实可以实现,再将SIZE的值更改为32

依旧可以将所有位置1

浙公网安备 33010602011771号

浙公网安备 33010602011771号