裸板ZYNQ简单实战-程序固化篇

前言

一般的调试中我们都是通过 JTAG 接口将 FPGA 配置文件和应用程序下载到 ZYNQ 器件中。同样的,我们也可以将尝试把程序存储在非易失性存储器中,在上电或者复位时让程序自动运行,这个过程需要启动引导程序( Boot Loader) 的参与。 Boot Loader 会加载 FPGA 配置文件,以及运行在 ARM 中的软件应用。好吧下面又要开始大段摘抄原子的开发手册了(感谢原子):

对了很重要的一点:在官方的的fsbl工程中是有调试开关的,在src/fsbl_debug.h中增加FSBL_DEBUG_INFO的宏定义,这样就将fsbl中所有的调试信息打开,启动过程中会有各种打印信息。

在 ZYNQ SoC 的启动和配置过程中, 既需要 PS 的配置信息,又需要 PL 的配置信息。 为了简化配置 PS和 PL 的处理过程, ZYNQ 的配置顺序与 Xilinx FPGA 的配置顺序有所不同。 差异来源于以下两种类型的文件:

1、 FPGA BIT 文件——定义 PL 的行为

2、 软件 ELF 文件——运行在 PS 中的程序

在 ZYNQ 中, PS 作为主器件, PL 可以看作是 PS 的一个外设,因此需要由 PS 来配置 PL。这个配置顺序的优势是它允许对 PS 单独上电的时候, 此时 PL 不上电,以减小功耗。 不过也有例外, 就是我们在使用JTAG 下载程序的时候, 此时是使用电脑作为主机来配置 PL。

软件代码和配置 FPGA 的 BIT 文件可以存储在连接到 PS 端的配置存储器件中。 PS 支持多种片外非易失性存储器( Quad SPI Flash, NAND Flash, NOR Flash 或 SD 卡) 。领航者 ZYNQ 开发板从硬件上支持 SD卡和 QSPI 作为配置器件。

ZYNQ SoC 的启动由片上的 BootROM 开始。片上 BootROM 是 ZYNQ 芯片上的一块非易失性存储器,它包含了 ZYNQ 所支持的配置器件的驱动, 而且里面的代码是不可修改的。 BootROM 中的代码首先会在片外的非易失性存储器中寻找一个头文件, 头文件里定义了一些启动信息, 用于配置BootROM 的运行。 这些启动信息包括是程序是否就地执行( excute in place) , FSBL 的偏移地址以及是否为安全模式等。头文件的存在确保 BootROM 能够按照配置器件被格式化后的方式操作。

BootROM 执行之后,下一个配置阶段被称为 First-Stage Boot Loader( FSBL), 它是由设计者所创建的。

FSBL 可以配置 DDR 存储器和硬件设计过程中所定义的一些外设。这些器件需要在加载软件应用及配置 PL之前就初始化完毕。

总结一下 FSBL 的工作内容:

1、 初始化 PS;

2、 如果提供了 BIT 文件,则配置 PL;

3、 加载裸机应用程序到 DDR 中,或者加载 Second-Stage Boot Loader( SSBL);

4、 开始执行裸机应用程序,或者 SSBL。

PL 的配置是通过处理器配置访问接口( Processor Configuration Access Port, PCAP) 进行的,它允许对PL 进行部分配置或者完全配置。有关 PL 的部分配置我们会在其他章节予以介绍。 一旦 PS 启动运行之后, PL 可以在任意时刻被配置, FSBL 和应用程序可以清除、 配置以及使能 PL。要重建一个 ZYNQ 的启动镜像我们需要执行以下文件:

1、 Boot ROM 头文件:控制 Boot ROM 设置,比如就地执行、 加密、 FSBL 偏移量、镜像文件大小等;

2、 First-Stage Boot Loader;

3、 PL 配置文件, 即 BIT 文件;

4、 运行在 PS 上的软件应用程序。

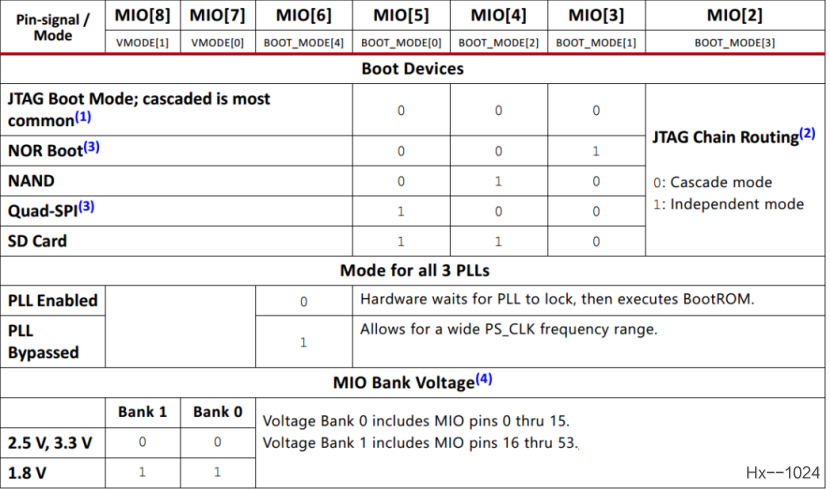

ZYNQ SoC 使用多个模式引脚来决定配置器件的类型, 软件的存储位置以及其他的系统设置, 这些引脚共享 PS 端的 MIO 引脚。 总共有 7 个模式引脚, 分别为 MIO[8:2]。其中,前四个引脚定义启动模式,第五个引脚定义是否使用 PLL, 第六个和第七个引脚定义上电过程中 MIO bank0 和 bank1 的 bank 电压。如下图所示

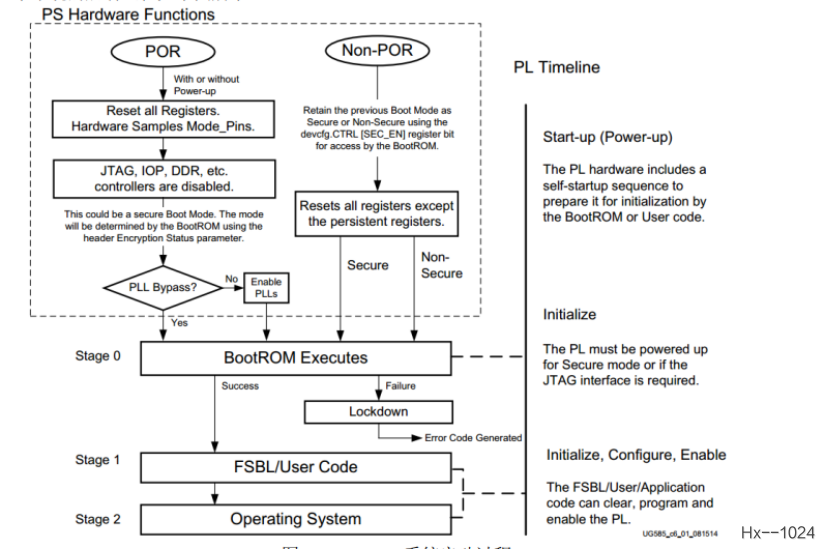

整个系统的启动过程如下

在上电复位( Power On Reset, POR) 之后,硬件会采集模式引脚的状态, 禁用器件内部的模块,并根据模式引脚的设置选择是否使能 PS 的时钟锁相环。而在其他的复位条件下, 比如通过 PS 的复位按键, 硬件不会执行上述的动作

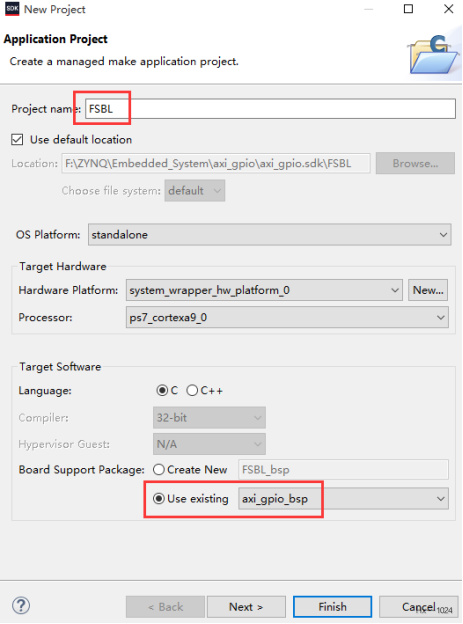

在菜单栏中选择“ File->New->Application Project”,然后在弹出的新建工程界面中设置工程名, 并选择工程中的 BSP, 如下图所示:

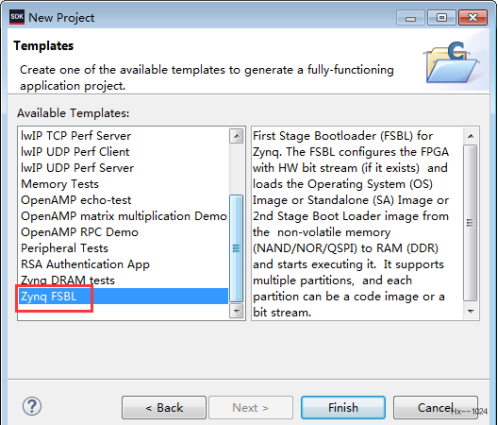

接下来点击 Next, 并在示例工程中选择“ Zynq FSBL”,最后点击“ Finish”如下图所示:

FSBL 工程创建完成之后, SDK 软件会自动执行编译过程,生成 FSBL.elf 文件

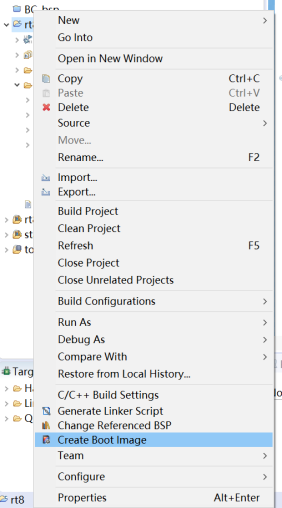

接下来我们就可以使用 FSBL、 BIT 文件和 C 应用程序来创建启动镜像。在需要的工程文件上右键

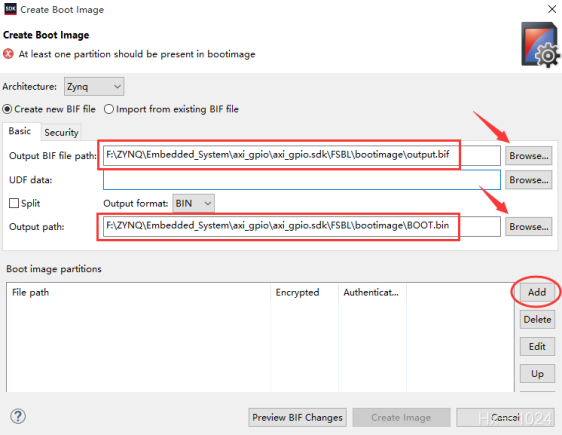

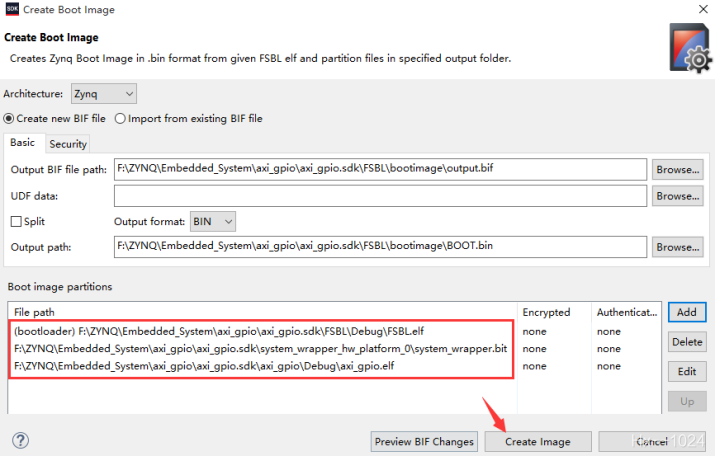

在弹出的创建 Boot Image 对话框中,设置输出文件的路径,如下图所示

在图中,设置了两个文件的输出路径, 路径中的“ bootimage”是我们在 FSBL 目录下新建的文件夹。红色方框中的 BIF 是 Boot Image 的配置文件, BIN 是启动文件。

接下来,点击图中红色圆圈所指示的 Add 按钮来添加用于生成 Boot Image 的文件,弹出如下图所示的界面

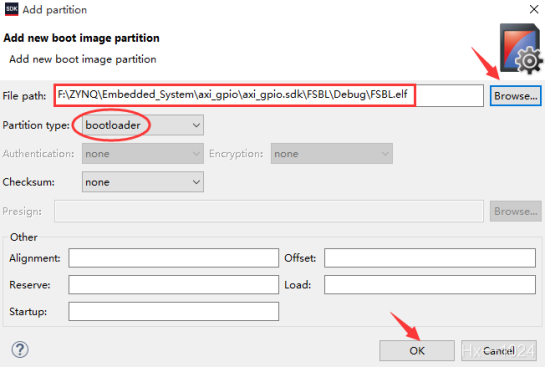

首先添加的是 FSBL, 在 Partion type 一栏默认的文件类型为 bootloader, 然后指定 FSBL.elf 所在的文件路径。点击“OK”后返回图 7.4.7 所示的界面,再次点击“ Add”按钮,添加 FPGA 配置文件,如下图所示:

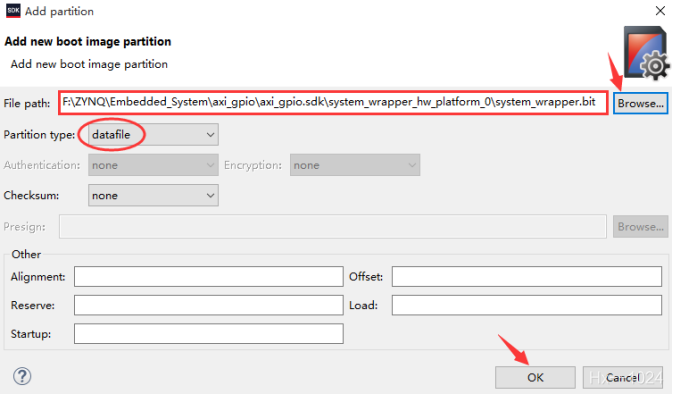

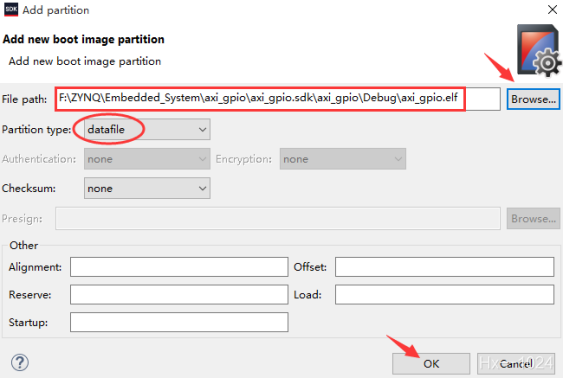

从图可以看到, Partion type 一栏的文件类型变成了 datafile,而 BIT 文件在我们创建SDK 应用时已经导入到 SDK 工程中了。需要注意的是, BIT 文件必须跟在 FSBL 后面,文件添加的顺序不能弄错。

再次点击OK,返回添加添加elf文件

点击“ OK”。 ELF 文件添加完成后, 创建 Boot Image 界面如下图所示:

生成即可

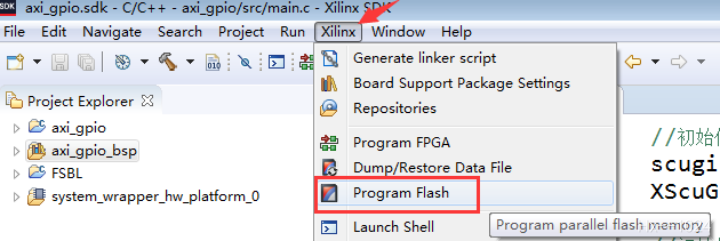

在 SDK 软件的菜单栏中点击“ Xilinx->Program Flash”, 如下图所示:

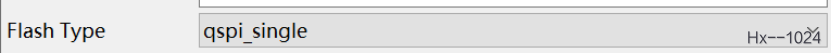

镜像文件和FSBL文件放在如图所示的位上(这个图都偷原子是不是太过分了,实在没办法自己的工程路径会透露个人隐私和咳咳咳,保密第一所以,对不住了)FLASH类型这块选择默认的就行 如下图所示,应该是和原子的FLASH类型不同吧

至此为止大功告成,固化也就成功了(相比之前单片机的一键傻瓜式确实麻烦一些,但是真的不难,从头到尾自己来上这么一次就熟悉了)

浙公网安备 33010602011771号

浙公网安备 33010602011771号