中断

中断的概念

中断是指在程序执行过程中,出现某种紧急事件,CPU暂停执行现行程序,转去执行处理该事件的程序——中断服务程序,执行完后再返回到被暂停的程序继续执行,这一过程称为中断。

中断源

引起中断的设备或事件称为中断源。

-

分类:

可笼统地分为两类:CPU内产生的,称为内部中断;其他的称为外部中断。

- 内部中断包括:由CPU本身产生的中断、由控制器产生的中断、由程序源安排的中断指令引起的中断。

- 外部中断由根据中断事件的紧迫程序将中断源划分为可屏蔽中断和不可屏蔽中断。

- 可屏蔽中断:指可以延时处理的事件。例如打印机的输入输出中断请求,如果CPU正在处理更加紧急的事件,打印机的中断请求就会被暂时屏蔽。被屏蔽的中断请求保存再中断寄存器中,当屏蔽接触后,仍然能够得到响应和处理。

- 不可屏蔽中断:指事件异常紧急,必须马上处理。例如掉电、RAM奇偶校验错误等引起的中断。

外部硬件中断主要有以下几种:

一、I/O设备:如显示器、键盘、打印机等。

二、数据通道:软盘、硬盘、光盘等。

三、实时时钟:如外部的定时电路等。

四、硬件故障:如电源掉电、RAM奇偶校验错误等。

产生于CPU内部的软件中断源有几种:

一、由CPU得运行结果产生:如除数为0、结果溢出、单步执行等。

二、执行中断指令INT:INT3

三、非法操作或指令引起异常处理、地址越界。

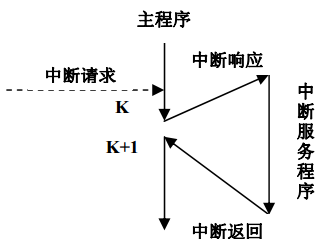

中断处理的基本过程

中断处理的基本过程包括中断请求、中断判优、中断响应、中断服务 和中断返回等五个阶段。

1.中断请求

(1)发生在CPU内部的中断,不需要中断请求,CPU内部的中断控制逻 辑直接接收处理。

(2)外部中断请求由中断源提出。外部中断源利用CPU的中断输入引脚 输入中断请求信号。一般CPU设有两个中断请求输入引脚:可屏蔽中断请求输入引脚(INTR)和不可屏蔽中断请求输入引脚(NMI)。

中断请求触发器

每个中断源发中断请求信号的时间是不确定的,而CPU在何时响应中断也 是不确定的。所以,每个中断源都有一个中断请求触发器,锁存自己的中 断请求信号,并保持到CPU响应这个中断请求之后才将其清除。

中断允许触发器

在CPU内部有一个中断允许触发器,当其为“1”时,允许CPU响应中断, 称为开中断。若其为“0”,不允许CPU响应中断,中断被屏蔽,称为关 中断。

通常,当CPU复位时,中断允许触发器也复位为“0”,即不允许CPU响应中断。当 CPU中断响应时,CPU自动关闭中断,禁止接受另一个新的中断。

2. 中断判优

CPU一次只能接受一个中断源的请求,当多个中断源同时向CPU提出 中断请求时,CPU必须找出中断优先级最高的中断源,这一过程称为 中断判优。中断判优可以采用硬件方法,也可采用软件方法

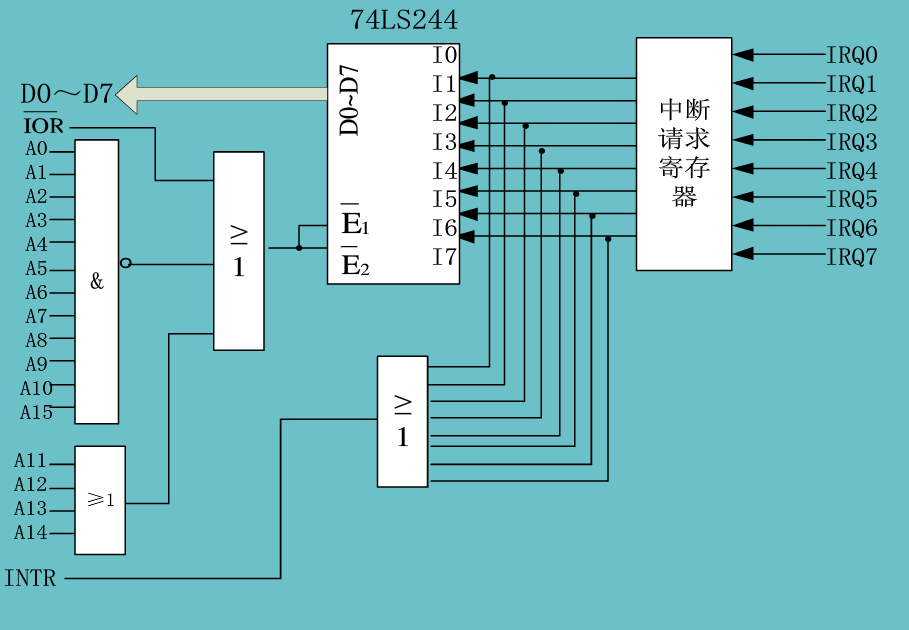

(1)软件判优

CPU检测到中断请求后,首先读取中断请求寄存器的内容,逐位检测它 们的状态,检测到某一位为1,就确定对应的中断源有中断请求,转去 执行它的中断服务程序。只要某一位为1,INTR就会显示高电平,否则低电平。先检测哪一个,哪一个的优先级就高,后检测 哪一个,哪一个优先级就低,检测的顺序就是各中断源的优先级顺序。

图中输入端口地址为87FFH。查询程序:

MOV DX, 87FFH

IN AL, DX ;读中断请求寄存器内容

SHR AL, 1

JC IR0 ;IRQ0有请求,转IR0

SHR AL,1

JC IR1 ;IRQ1有请求,转IR1

SHR AL,1

JC IR2 ;IRQ2有请求,转IR2

……

软件判优耗时较长。如果中断源很多,中断的实时性就很差,但是软 件判优优先权安排灵活。

(2)硬件判优

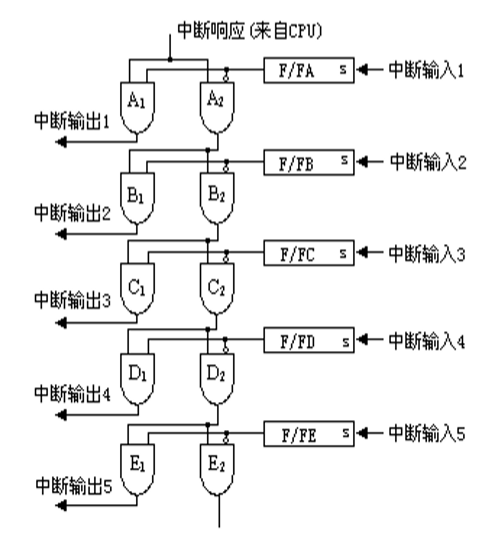

利用专门的硬件电路确定中断源的优先级,有两种常见的方式:菊花 链判优电路和中断控制器判优。

菊花链判优电路

基本设计思想:每个中断源都有一个中断逻辑电路,所有的中断逻辑电路 连成一条链,形如菊花链。排在链前端的中断源优先级最高,越靠后的设 备优先级越低。

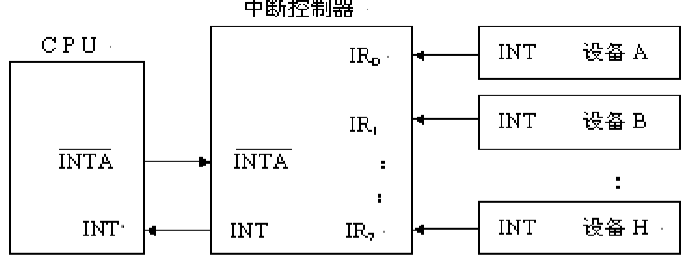

中断控制器判优

中断控制器,如Intel8259A,可以以多种方式设置中断源的中断优先级。 中断控制器中有一个中断优先级判别器,它自动判别出目前提出中断请求 的优先级最高的中断源,并将它的中断向量码送到数据总线,CPU接收中 断向量码并据此找到它的中断服务程序。

3. 中断响应

中断响应时,CPU向中断 源发出中断响应信号,同时:

① 保护硬件现场;

② 关中断,不允许CPU响应中断了;

③ 保护断点;

④ 获得中断服务程序的入口地址。

4. 中断服务

中断服务程序的一般结构为:

(1)保护现场。在中断服务程序的起始部分安排若干条入栈指令,将各 寄存器的内容压入堆栈保存。

(2)开中断。在中断服务程序执行期间允许级别更高的中断请求中断现 行的中断服务程序,实现中断嵌套。

(3)中断服务。完成中断源的具体要求。

(4)恢复现场。中断服务程序结束前,必须恢复主程序的中断现场。通 常是将保存在堆栈中的现场信息弹出到原来的寄存器中。

(5)中断返回。返回到原程序的断点处,继续执行原程序。

5. 中断返回

返回到原程序的断点处,恢复硬件现场,继续执行原程序。中断返回 操作是中断响应操作的逆过程。

中断向量和中断向量表

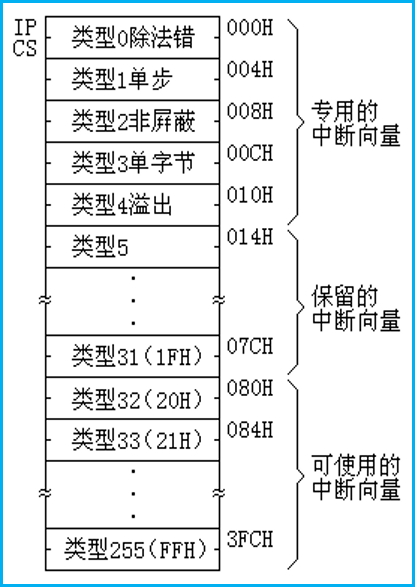

CPU的中断系统可以处理256种中断。每种中断都有对应的中断服务程序。中断服务程序的入口地址称为中断向量。256种中断向量存储在内存中构成一张表,称为中断向量表。

每个中断向量都包括两部分:段基址和偏移地址。因此,存放1个中断向量需要4个内存单元,256种中断向量共需要1K个内存单元。

中断向量表位于内存起始地址00000~003FFH的存储区内。从地址00000H开始,每4个单元存放一个中断向量,其中低地址的两个单元存放中断向量的偏移地址,高地址的两个单元存放中断向量的段基址。256种中断向量按中断向量码从0到255的顺序依次存入中断向量表中。

8086/8088CPU的全部256种中断类型中0~31是微处理器专用中断,从类型32开始直到255作为用户中断类型。用户中断向量由用户填写到中断向量表中,中断服务程序也由用户编写 。

Intel保留前32(031)个中断向量为Intel各种微处理器系列成员专用,其中,类型04的中断向量在8086~Pentium的所有Intel系列微处理器中都相同,其他中断向量预留下来给80286及以上的高档微处理器组成的系统中。这些专用中断向量对应的中断服务程序由系统设置。

- 中断向量在中断向量表中的存放首地址称为向量地址,其值为:中断类型码×4。

- 当CPU调用中断类型码为n的中断服务程序时,首先把n乘以4,得到它的向量地址4n,然后把4n+1:4n两个单元的内容取出并装入IP寄存器;再把(4n+3:4n+2)两个单元的内容取出并装入CS寄存器,CPU就获得了n的中断服务程序的入口地址,进而转去执行中断服务程序。

- CS:IP 两个寄存器指示了 CPU 当前将要读取的指令的地址,其中 CS 为代码段寄存器,而 IP 为指令指针寄存器 。 当读取完指令后,CS:IP 将会自动的改变,基本上是改变 IP ,从而指向下一条要读取的指 令。

8086/8088CPU的5个专用中断类型

-

类型0 除法错中断,除法运算结果溢出或是除以0时发生,屏幕出现错误提示。

-

类型1 单步中断,也称为陷阱中断。如果TF标志位为1,CPU每执行 一条指令后,就停下来等待,并提示CPU内部各寄存器的值和一些附 带信息

TF—陷阱标志,为程序调试而设的。当设置TF=1,CPU处于单步执行指令的方式;当设置TF=0时,CPU正常执行程序。

单步中断使用户可以逐条执行程序,让程序员能够精确了解程序的执行情 况,给用户调试程序提供方便

注:在8086中,没有专门设置TF清0或置1的指令,要使TF清0或置1,需 要通过执行一段程序实现。

例如,使TF标志位置1:

PUSHF ;FLAG标志寄存器压栈

POP AX ;FLAG内容弹出到AX

OR AX, 0100H ;使AX中对应TF的位置为1

PUSH AX

POPF

-

类型2 非屏蔽中断,该中断不能被软件禁止。非屏蔽中断由CPU之外 的硬件产生,通过CPU的NMI引脚输入中断请求信号,上升沿触发。 该中断用于处理紧急事件,如奇偶校验错、电源掉电等

内部中断的中断向量码都是由微处理器直接给出的,但中断类型2虽然属于外部中断,但是它的中断向量码还是由微处理器直接给 出。

-

类型3 断点中断,由一个单字节指令INT3引起的中断,指令代码为 0CCH。它的中断服务程序将该指令所处的位置作为程序断点保存起来。 在调试程序时用这条指令设置断点。

-

类型4 溢出中断,INTO指令的专用向量。如果溢出标志位OF为1,则 INTO指令中断正在执行的程序。如果OF为0,则INTO指令不执行任 何操作,就像不存在一样,程序继续执行下一条指令。例:

MOV BL,126 MOV AL,5 ADD AL,BL ;OF=1 INTO ;执行溢出中断服务程序

硬件中断

8086/8088CPU芯片有两个硬件中断请求信号输入引脚:NMI和INTR,用来接收外部中断源产生的中断请求。NMI引脚接收非屏蔽中断请求,INTR引脚接收可屏蔽中断请求。

(1)非屏蔽中断

非屏蔽中断不能被软件禁止,即不受IF标志位控制。NMI采用上升沿触发,中断类型码为2,由CPU内部译码产生。优先级高于可屏蔽中断。CPU响应这种类型的中断时,将所有内部寄存器存于使用电池的备份存储器或EEPROM中。非屏蔽中断用于处理紧急事件,如存储器奇偶错、电源掉电等

(2)可屏蔽中断

采用电平触发方式,高电平有效。

CPU收到中断请求信号后,检测中断允许标志位IF,若IF=1,CPU响应INTR请求;若IF=0时,CPU屏蔽INTR请求。被屏蔽的中断请求信号可一直保持高电平,直到CPU接收。

中断允许标志位IF可以用指令STI和CLI进行设置。

CPU响应INTR请求时,启动中断响应总线周期,发中断应答信号(INTA) ̅。系统连续产生2个(INTA) ̅脉冲,用于从数据总线接收中断控制器送出的中断类型码。

8088/8086中断的处理流程

- 如果有一个或多个中断条件出现,CPU响应中断。

- 如果检测到内部中 断或非屏蔽中断,CPU从内部获得中断类型码;

- 如果检测到可屏蔽中 断请求,CPU进一步测试IF标志位,如果IF=1,CPU就进入中断响应 总线周期,从中断控制器获取中断类型码。

- 获得中断类型码之后,各种中断的处理过程相同。CPU将中断类型码 放入暂存器保存,以下动作顺序发生:

- 标志寄存器的内容入栈,堆栈指针 SP减2;

- 清除中断标志IF和TF;

- 主程序断点CS的内容入栈,堆栈指针SP再减2;

- 主程序断点IP的内容入栈,堆栈指针SP再减2;

- 根据中断类型码,在中断向量表中取出中断向量装入IP和CS;

- 执行中断服务程序;

- 中断返回,执行IRET指令,从堆栈中弹出IP、 CS和Flags,堆栈指针SP+6。

浙公网安备 33010602011771号

浙公网安备 33010602011771号