FPGA——ROM的使用与仿真,signaltap II的使用,in-system memory content editor的使用

ROM的使用

-

使用quartus实例化字符宽度为8,深度为256的单端口一个ROM,指定mif文件的位置并进行仿真,仿真脚本如下所示

-

`timescale 1ns/1ns `define clk_period 20 module tb_rom_1port(); reg [7:0]addr; reg clk; wire [7:0]q; rom_1port rom_1port_inst ( .address ( addr ), .clock ( clk ), .q ( q ) ); initial clk = 1'b1; always#(`clk_period/2) clk = ~clk; integer i = 0; integer j = 0; initial begin addr = z; #2001; for(i=0; i<=10; i=i+1)begin for(j=0; j<=255; j=j+1)begin addr = j; #`clk_period; end end #2000; $stop; end endmodule -

-

-

-

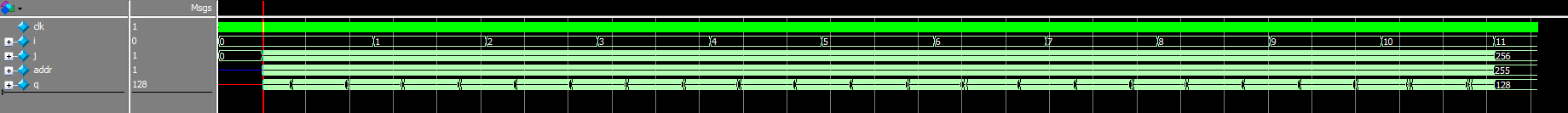

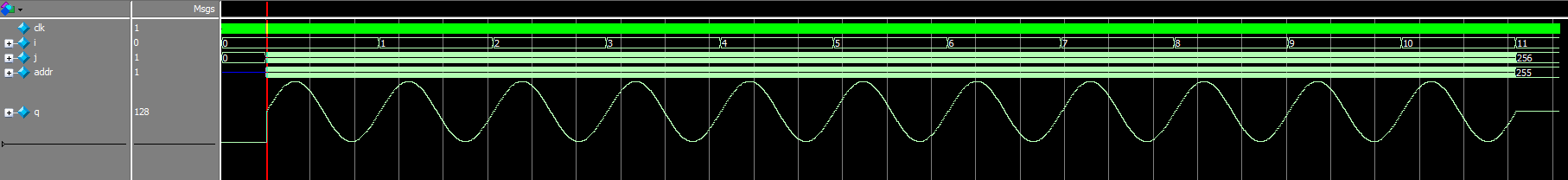

使用上面的脚本对定制的rom仿真后波形如下所示,图3是输出q为字符格式,图5输出为波形的格式(modelsim的功能之一,将数字转换为波形),从图4中可以看出数据的输出同ram一样,地址在时钟上升沿被采样,在下一拍时钟被输出

-

这里要说的并不仅仅是仿真,我们写一个简单的顶层文件,使用signaltap II以及in-system memory content editor,顶层文件如下

-

module rom_top( clk, rst, q); input clk; input rst; output [7:0]q; reg [7:0]addr; rom_1port rom_1port ( .address ( addr ), .clock ( clk ), .q ( q ) ); always@(posedge clk or negedge rst) if(!rst) addr <= 8'd0; else addr <= addr + 1'd1; endmodule -

建立顶层文件后,进行仿真与编译并且新建一个stp文件,

- stp文件是在可视化界面中设置一个脚本

- 将时钟,采样的深度,需要观察的信号都设置好后保存

- 在工程中进行制定引脚等信息,重新进行编译

- 完成后打开之前保存好的stp文件‘

- 连接仿真器,将编译好的文件烧写进去,

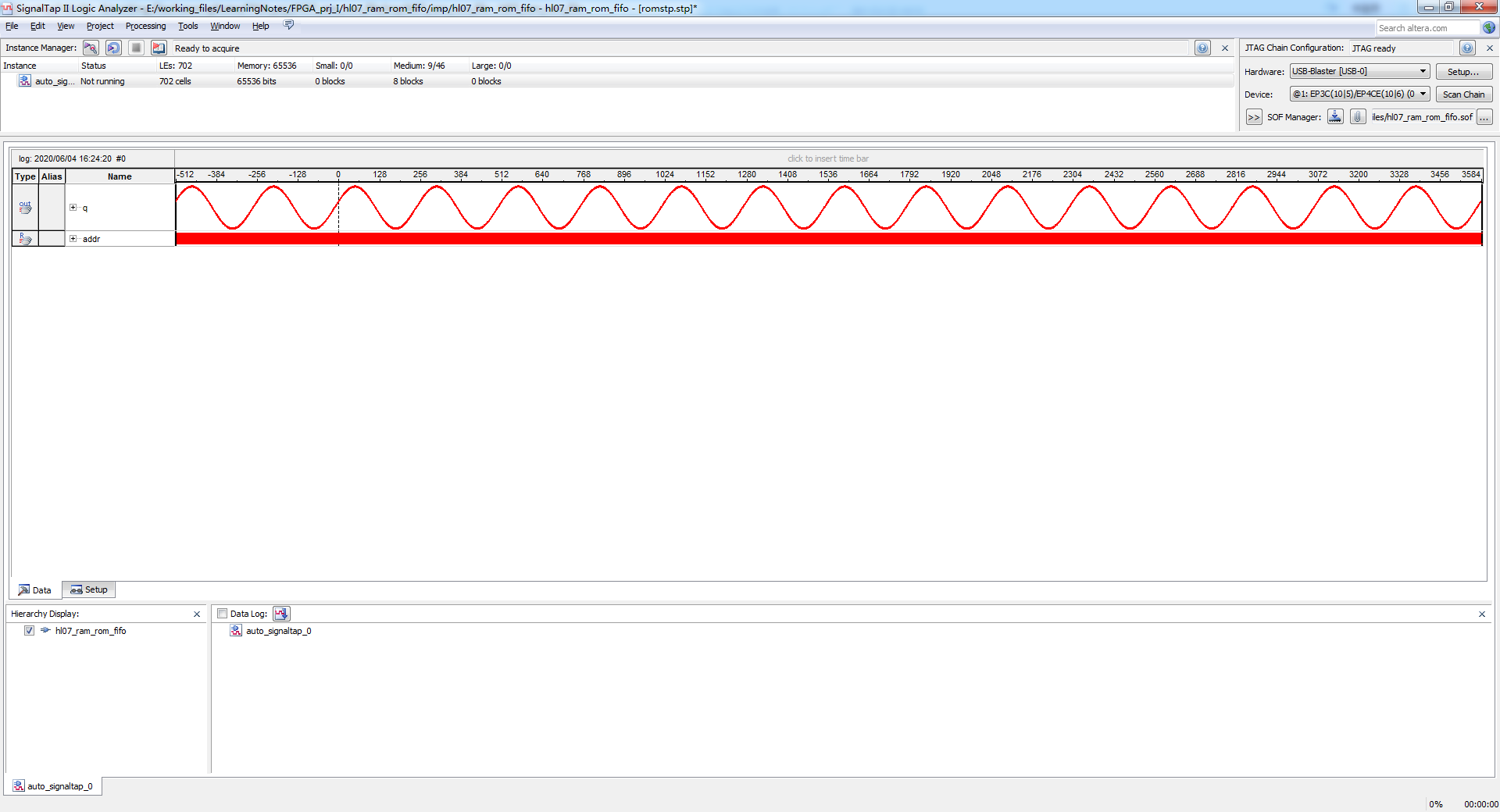

- 选中实例信息,运行后就得到了如下所示

-

-

操作成功后如图所示

-

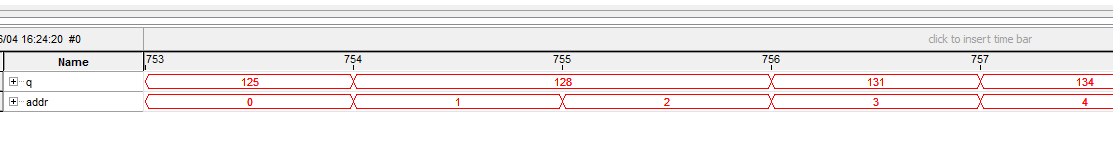

通过设置我们观察了rom输出随着地址的变化

-

-

通过我们在signaltap II中观察到的信号可以看到基本与我们仿真中的相同

-

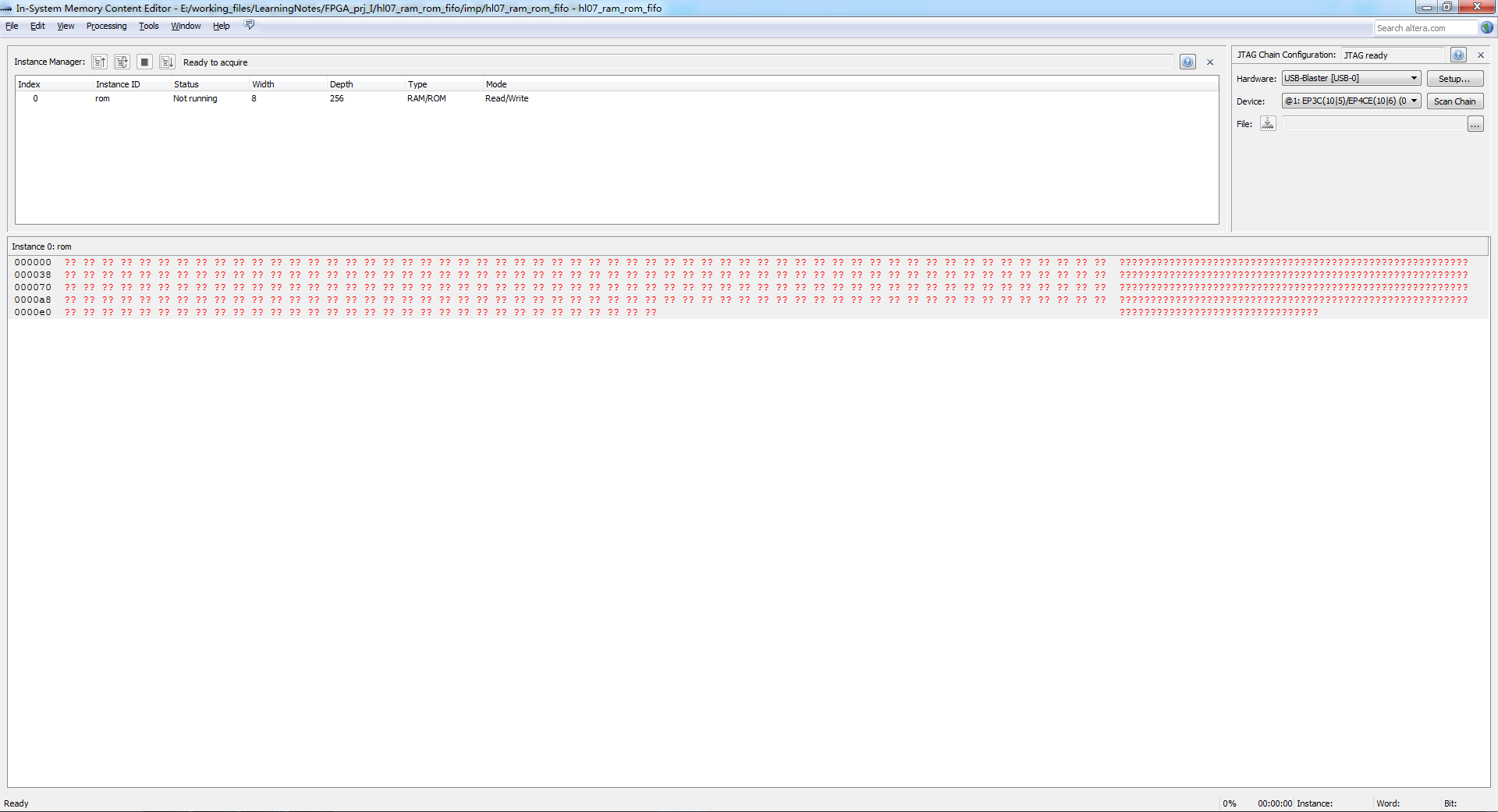

在Tools中打开in-system memory content editor,基本界面如下

-

-

全是问号的原因是因为打开后并没有采集信号,接下来我们对rom进行采集

-

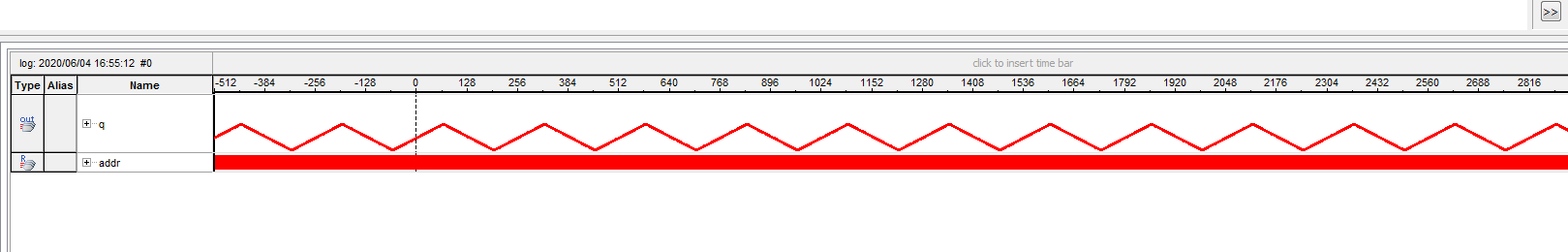

同时我们通过这个工具可以导入另一个已经准备好的mif文件,导入后使用signaltap II进行观察

-

-

可以看到将之前的正弦波替换成了三角波

浙公网安备 33010602011771号

浙公网安备 33010602011771号