Verilog仿真遇到的问题

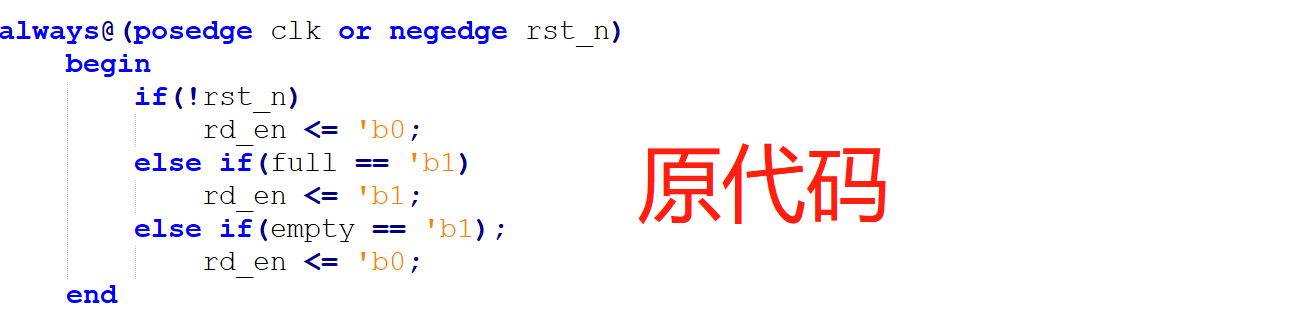

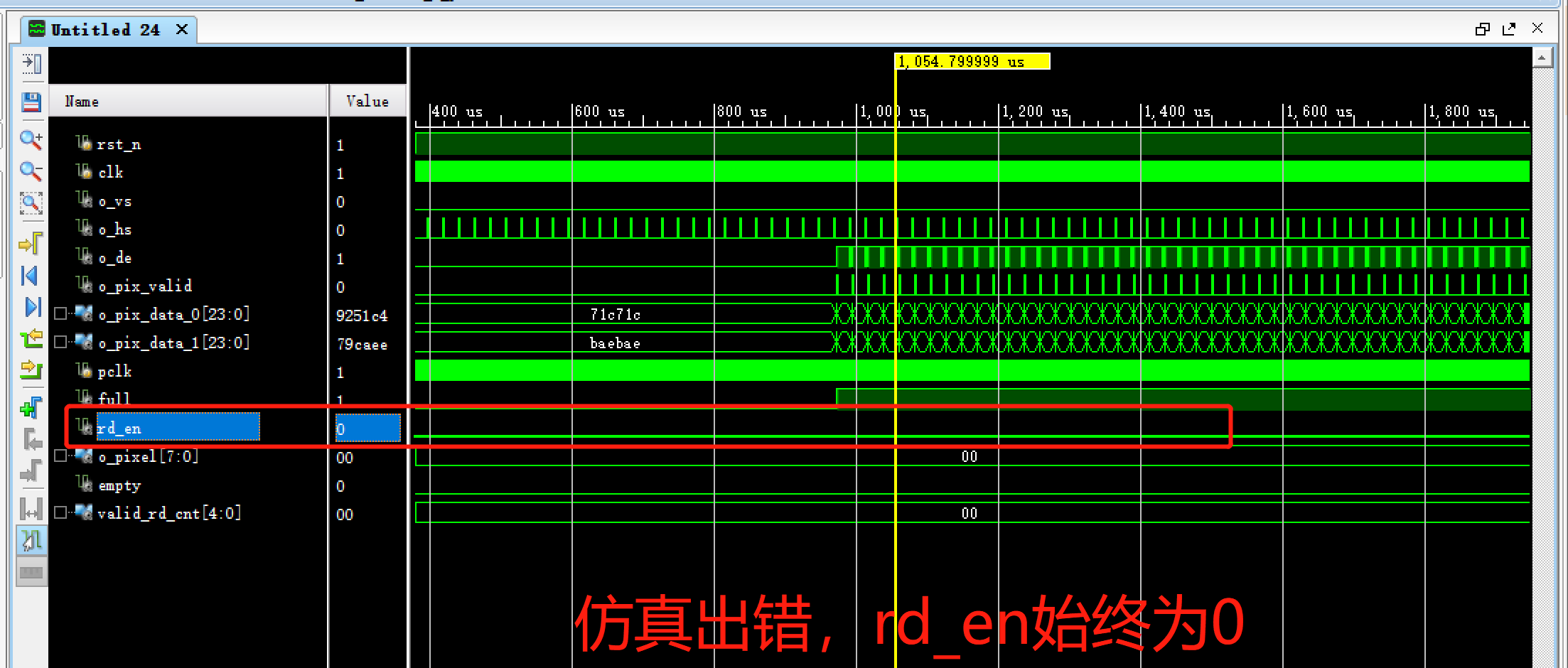

1、Vivado 15.4仿真时编译没有报错,但是仿真不成功,逻辑很简单,full为高电平时,rd_en要拉高,但全程没有拉高!

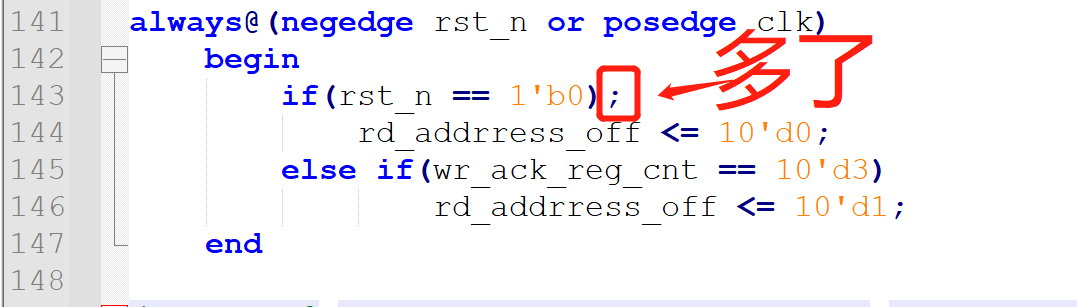

检查语法发现语句" else if( empty == 'b1); "多了一个分号“ ;‘,愚蠢了。

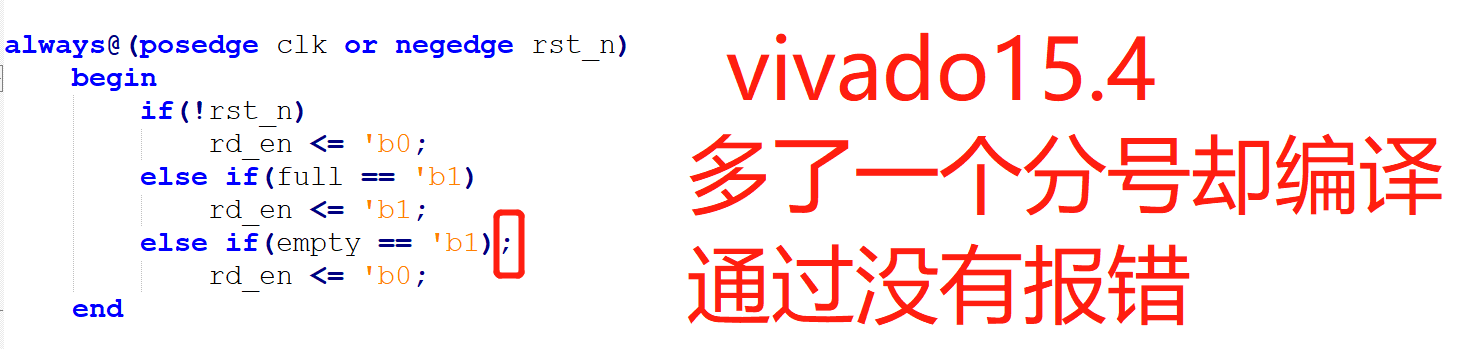

2、前辈指点reg变量不要跨always块赋值,确实,这样容易“打架”(也就是时序矛盾),以及时序逻辑电路的if-else语句块可以不写全,但是组合逻辑电路的if-else语句块要写全

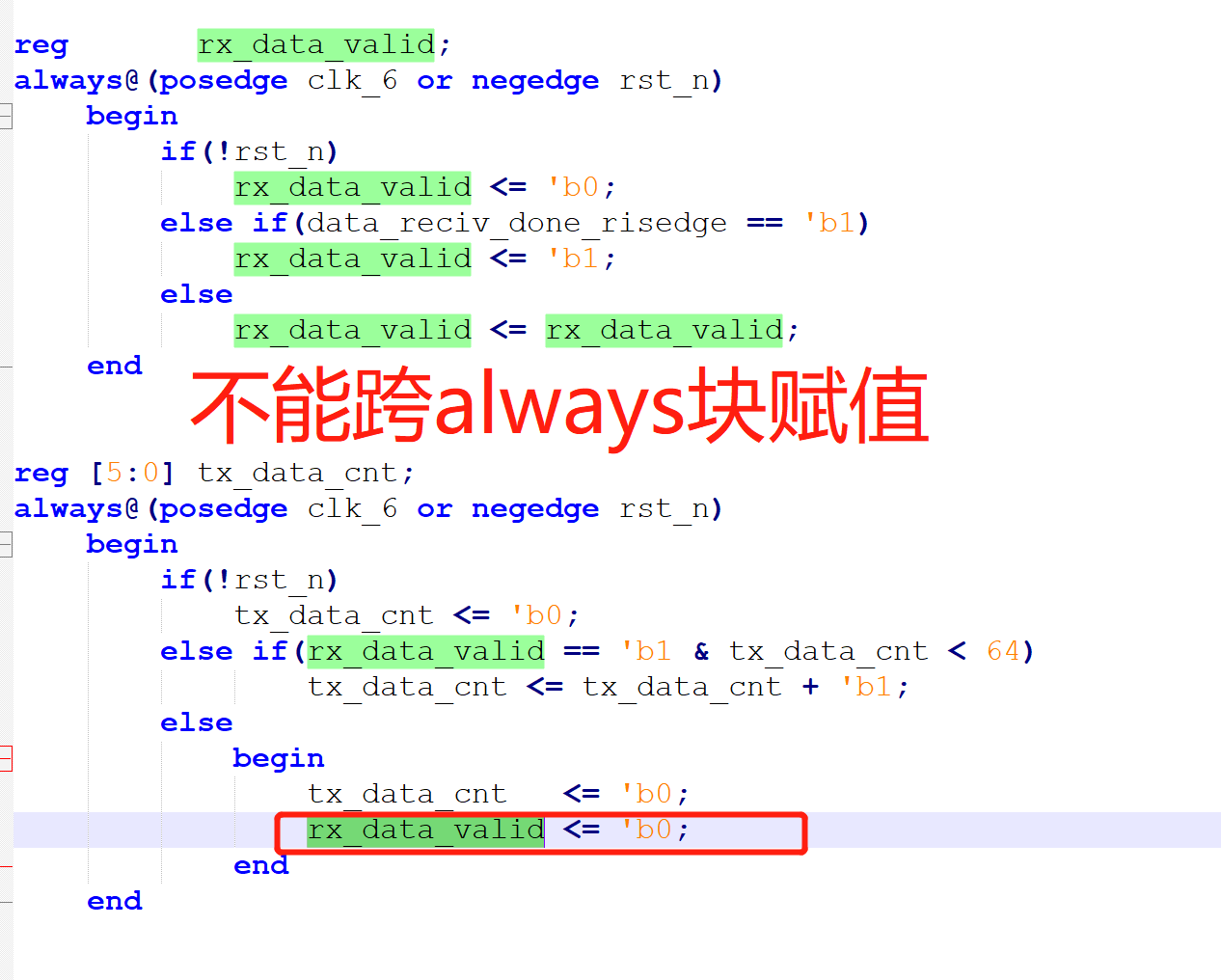

3、不要这样写!在一个clk里面完成了二进制乘法,可能时序上有风险

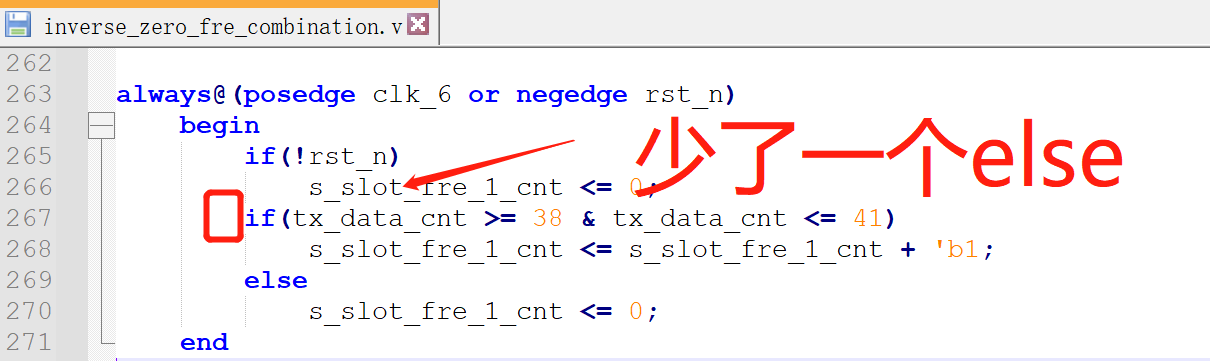

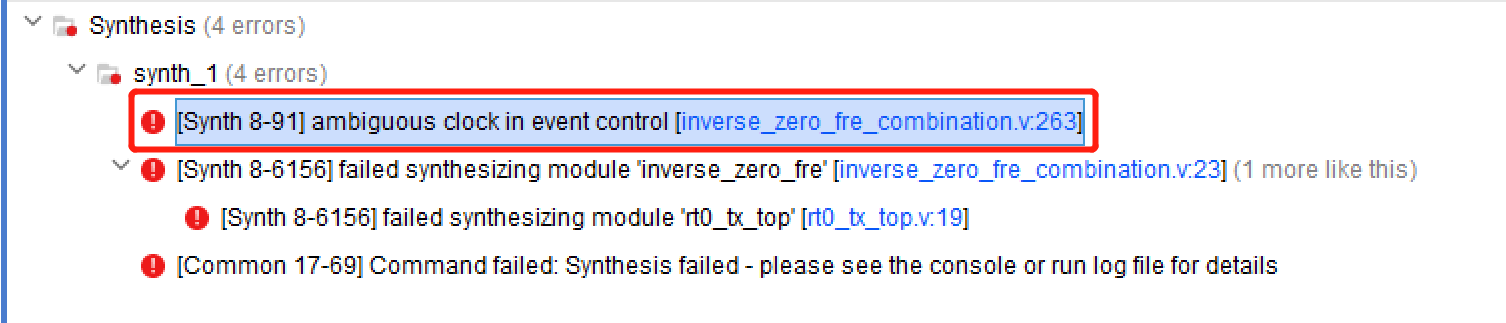

4、if-else掉了else后,仿真会通过,但是综合会报时序冲突

编译报错:模棱两可的时钟

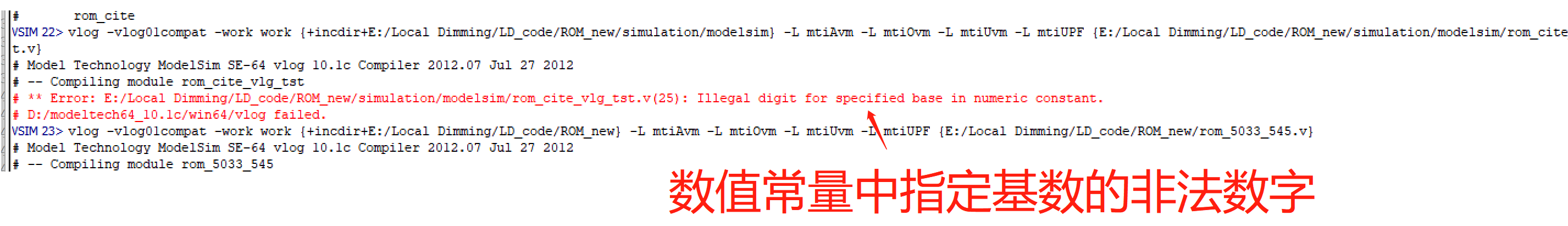

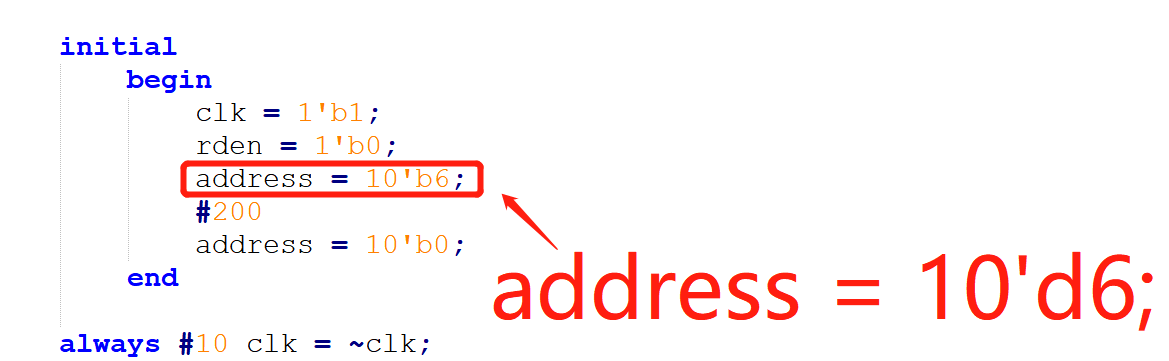

5、仿真编译遇到:Illegal digit for specified base in numeric constant(数值常量中指定基数的非法数字)

排查发现是幅值时基数选错了,10‘d6,写成了10’b6

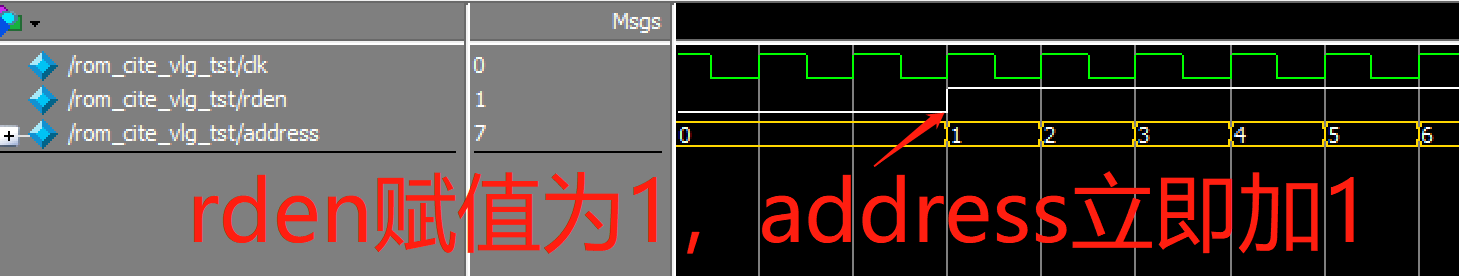

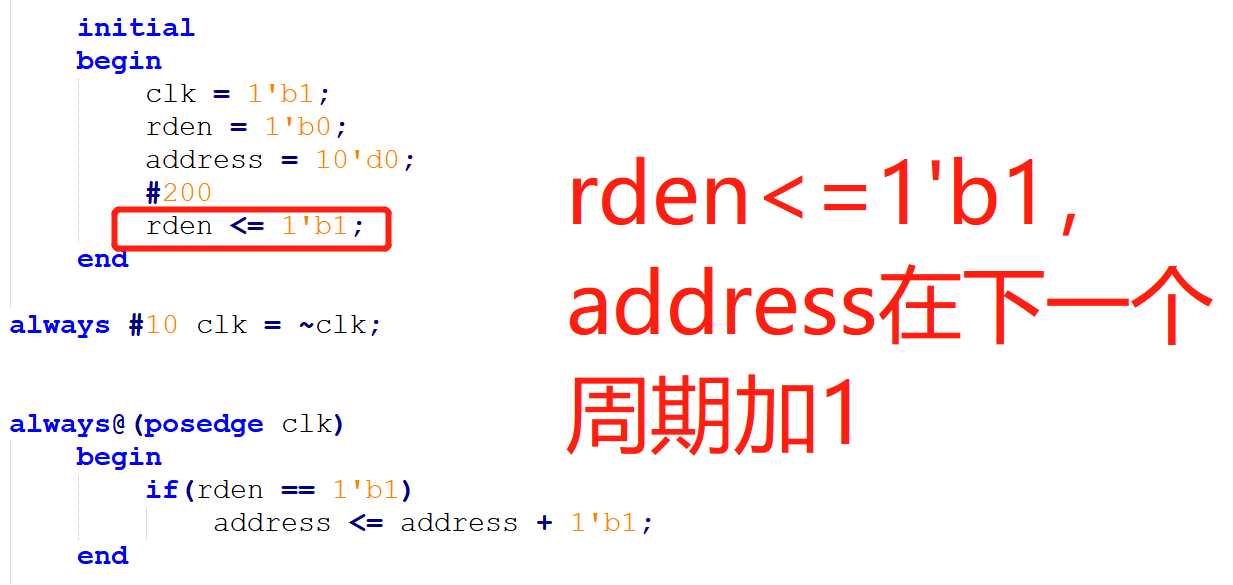

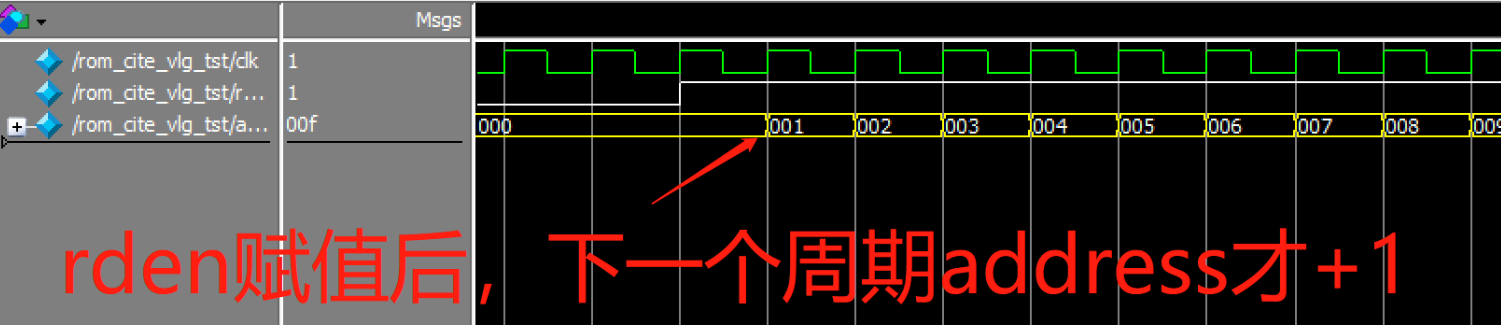

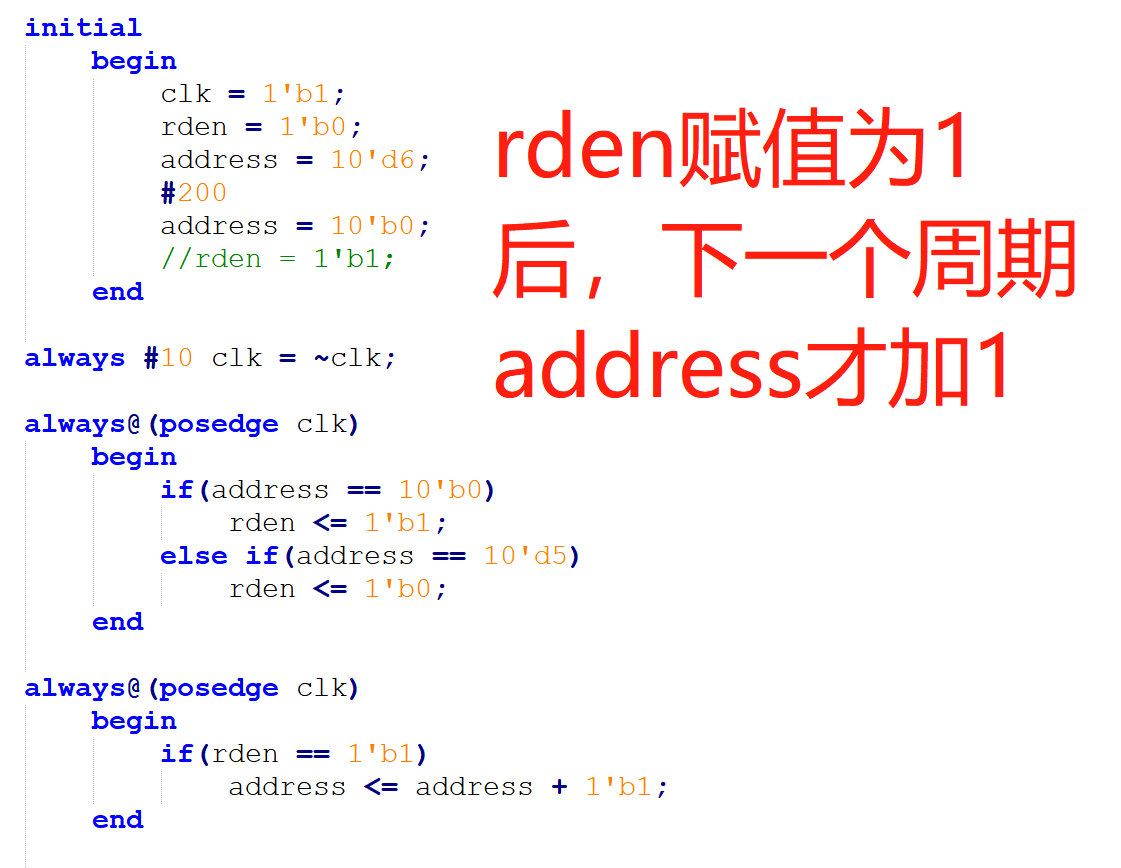

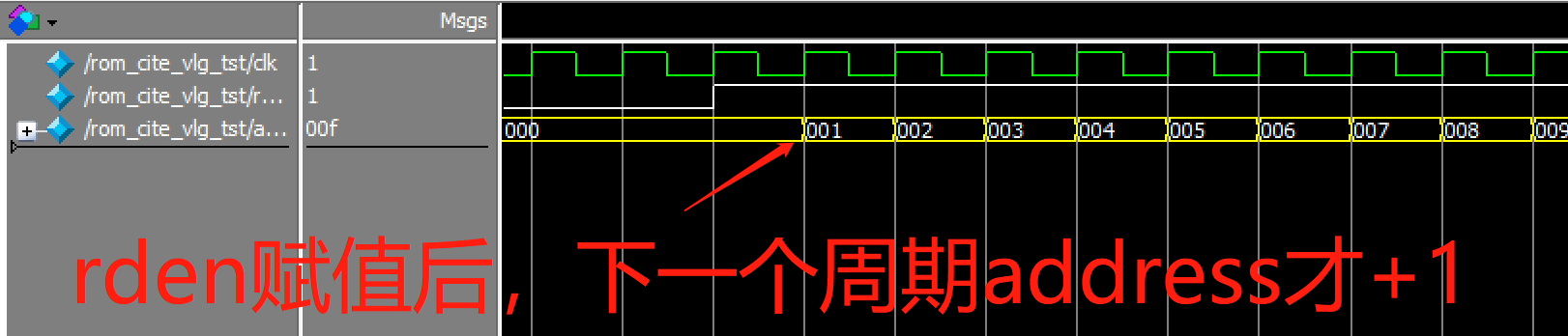

6、遇到一个仿真的问题:

在testbench初始化中赋值rden=1,会立即给address加1;但在我理解看来,address应该是等待下一个周期以后才会address加1;

解决办法有两个:

一种是:rden <= 1'b1;

另一种:延时给rden赋值为1

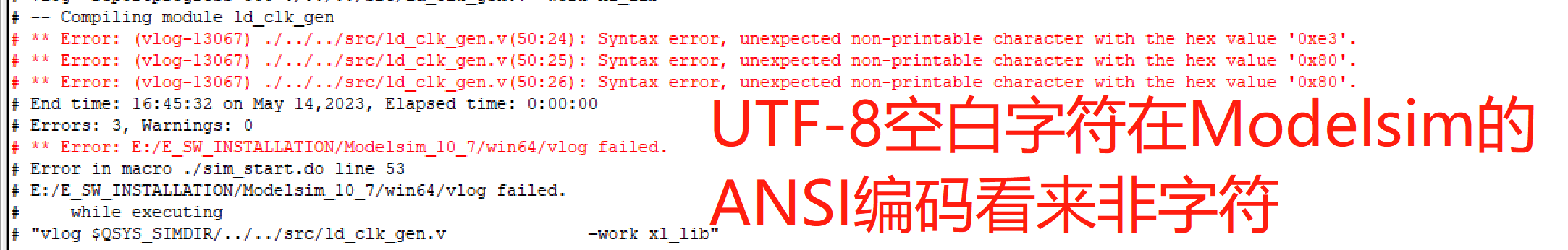

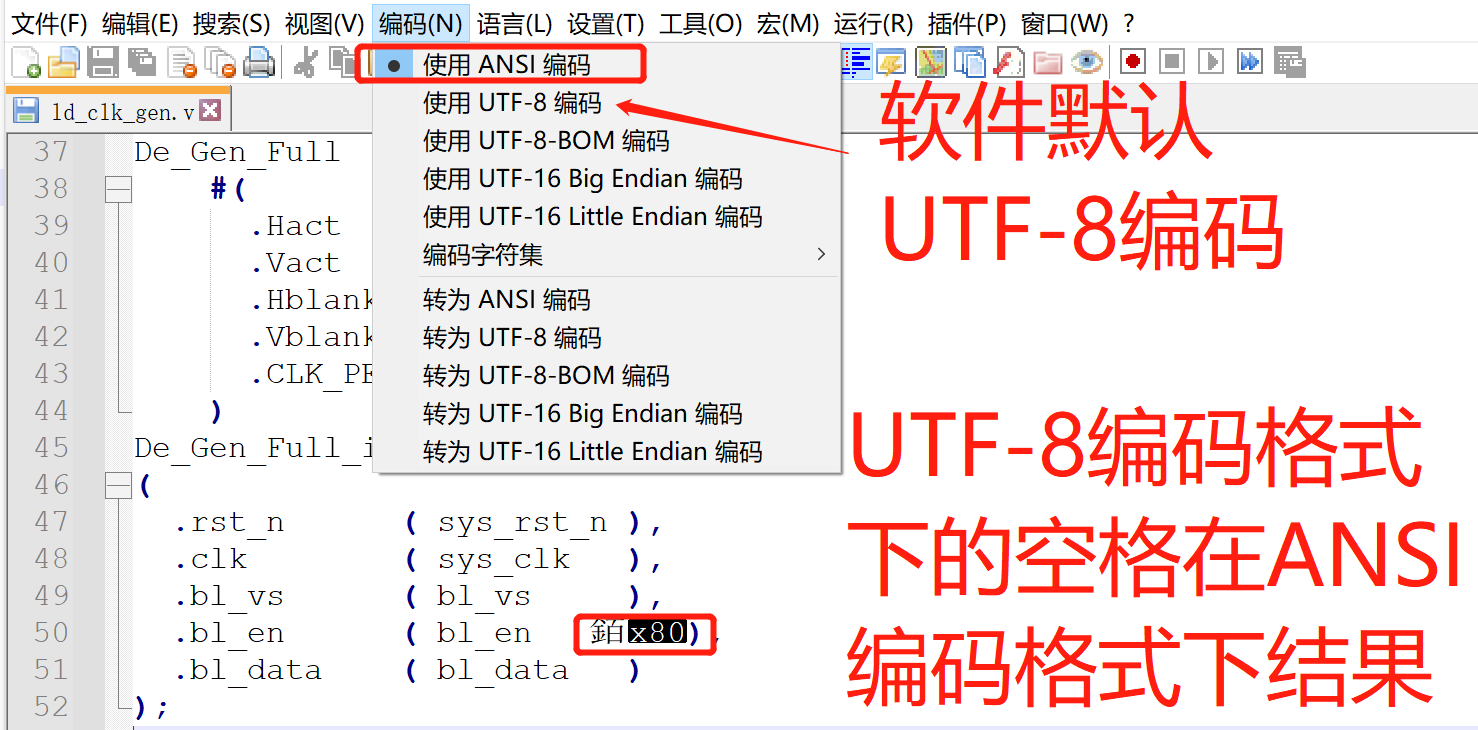

7、代码仿真编译时y语法报错,不可打印的字符:Syntax error, unexpected non-printable character

排查后发现:Modelsim支持ANSI编码,编辑时使用中文打的空格使用UTF-8编码,该空白字符在ANSI编码看来非打印字符,如下:

需要在notepad++等编辑器的编辑里面选择ANSI编码,找到UTF-8编码格式下的中文空白字符删除掉即可。

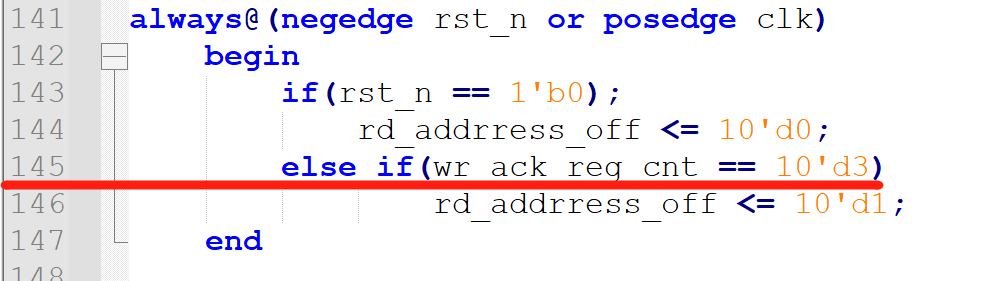

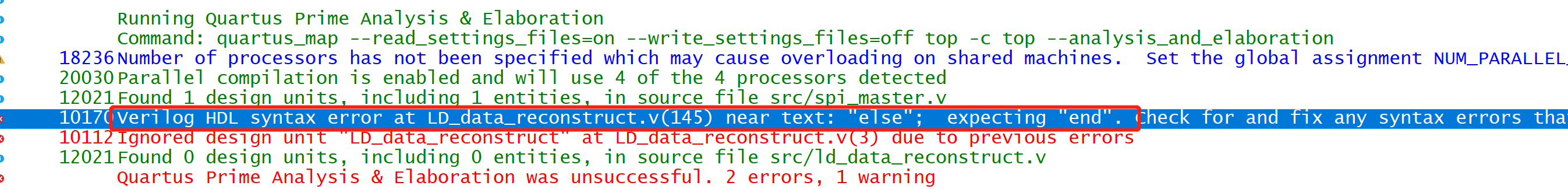

8、编码报错expecting "end",最后发现if(rst_n == 1'b0)后多了冒号