VBY(Video by One)协议

V-by-One(Video by One) 是由日本赛恩电子公司(THine Electornics)开发的适用于平板显示器的信号传输接口标准,也是专门面向图像传输开发出的数字接口标准。

V-by- One的开发目的,是为了替代LVDS。

接口具有较低的功耗并支持高达4Gbps的数据传输(有效数据量达到3.2Gbps)。

VB1接口通过CDR(Clock Data Recovery,时钟数据恢复)的方式进行高速串行数据传输,从根本上解决了传输线时滞问题,同时不需要时钟传输线,因此具有很强的抑制EMI能力。

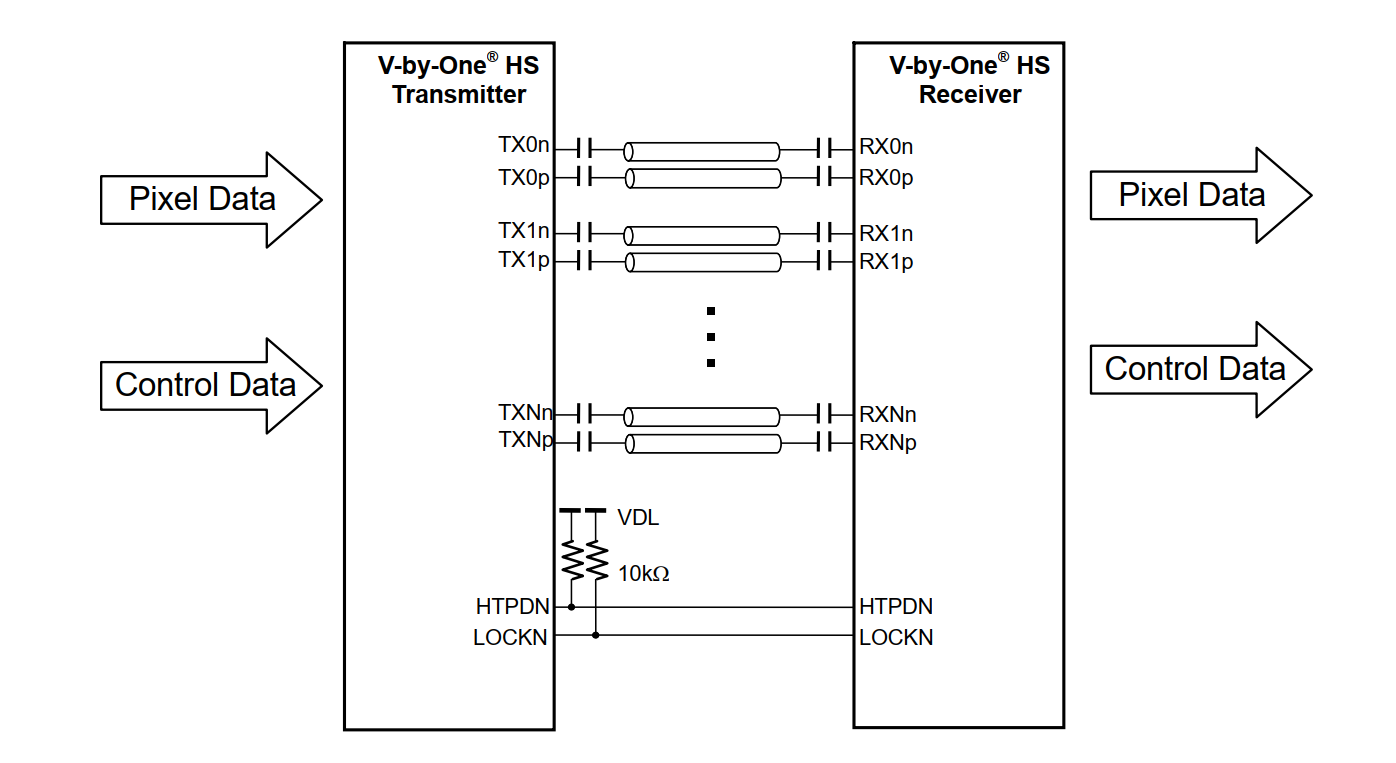

数据信号通过各通道以交流耦合的方式传输面板的显示数据。

1.信号传输通过FPGA的serdes接口(TX/RX),还有两个交互信号(HTPDN与LOCKN),其中交互信号定义如下

HTPDN:对于接收端(玻璃-RX)为输出port,当接收与发送连接上后置低,接收端可上电就直接给出低信号(类似热插拔信号);

对于发送端(主板-TX)为输入port,当为高时表示没有与接收端连上,默认在发送端配置上拉电阻;

LOCKN:对于接收端(玻璃-RX)为输出port,当接收端能锁定到发送端传输过来的时钟信号后置低,表示接收端已锁定时钟;

对于发送端(TX)为输入port,当接收到低电平信号是表面接收端已锁定时钟,接下来可发送训练码及数据信号,同样在发送端默认配置上拉电阻;

LOCKN信号用来表示接收端是否将发射端传输来的时钟信号通过CDR解码成功。

2、信号传输框图:

番外:数据通道所需要的通道数目取决于显示面板的分辨率(4K/8K)、色深(一般8bit)和帧率(60/120/144)。

UHD 4K(3840*2160)/60Hz,8bit灰阶的图像一秒钟需要传输的数据量:3840(列)*2160(行)*3(RGB)*8(bit)*60(帧率)=11,943,936,000 bit,接近12亿bit的数据量

4K60Hz对应8 lane差分数据对,则每lane在1秒内需要处理的数据最少(不包含训练码等数据)为:11,943,936,000 bit/8=1,492,992,000bit≈1.5亿bit

UHD 4K(3840*2160)/120Hz,8bit灰阶的图像一秒钟需要传输的数据量:3840(列)*2160(行)*3(RGB)*8(bit)*120(帧率)=23,887,872,000 bit,接近24亿bit的数据量

4K/120Hz对应16 lane差分数据对,则每lane在1秒内需要处理的数据最少(不包含训练码等数据)为:23,887,872,000 bit/16=1,492,992,000bit ≈1.5亿bit

UHD 8K(7680*4320)/60Hz,8bit灰阶的图像一秒钟需要传输的数据量:7680(列)*4320(行)*3(RGB)*8(bit)*60(帧率)=47,775,744,000 bit,接近48亿bit的数据量

8K/60Hz对应32 lane差分数据对,则每lane在1秒内需要处理的数据最少(不包含训练码等数据)为:47,775,744,000 bit/32=1,492,992,000bit ≈1.5亿bit

UHD 8K(7680*4320)/120Hz,8bit灰阶的图像一秒钟需要传输的数据量:7680(列)*4320(行)*3(RGB)*8(bit)*120(帧率)=95,551,488,000 bit,接近96亿bit的数据量

8K/120Hz对应64 lane差分数据对,则每lane在1秒内需要处理的数据最少(不包含训练码等数据)为:95,551,488,000 bit/64=1,492,992,000bit ≈1.5亿bit

参考

- VBY通信协议:有VBY附件

- 薄膜晶体管液晶显示器显示原理与设计(王东升-BOE董事长)

- LVDS与VB1的对比:LVDS与VB1详细介绍

还有LVDS:https://wenku.baidu.com/view/effa71e5876fb84ae45c3b3567ec102de3bddfd3.html?rec_flag=default&fr=Recommend_RelativeDoc-60272,100007,60308,40340,40397-kpdrec_doc_pc_view-05ad4d7c03768e9951e79b89680203d8ce2f6afe&sxts=1637644459061

1,492,992,000bit ≈