FPGA学习记录3——Quartus2中Test Benches设计

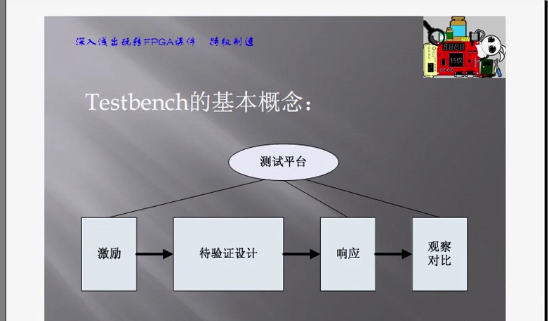

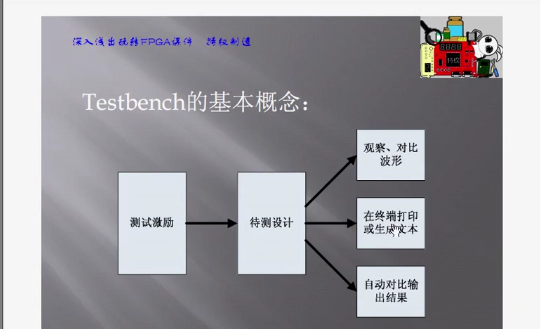

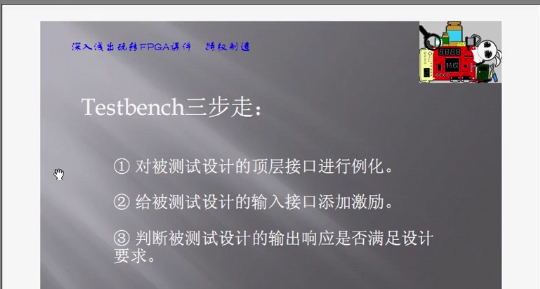

Test Benche 基本概念

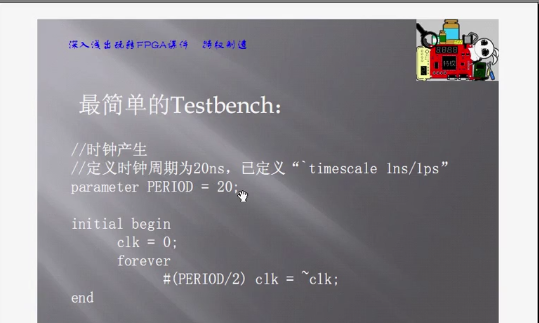

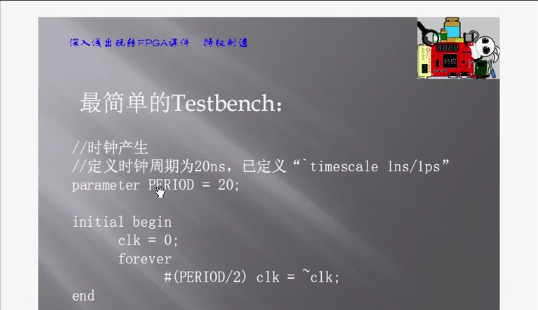

//时钟产生方式1

//定义时钟周期为20ns,已定义"'timescale 1ns/1ps"

parameter PERIOD = 20;

initial begin

clk = 0;

forvere

#(PERIOD/2) clk =~clk;//每10ns clk取反一次

end

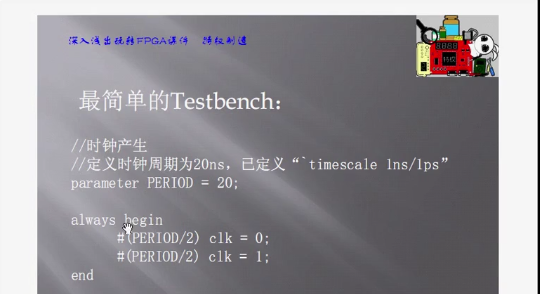

//时钟产生方式2

//定义时钟周期为20ns,已定义"'timescale 1ns/1ps"

parameter PERIOD = 20;

always begin

#(PERIOD/2) clk = 0;

#(PERIOD/2) clk = 1;

end

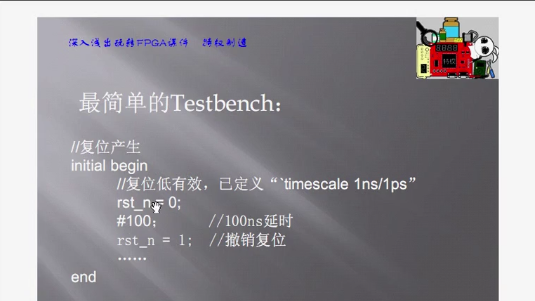

//复位产生方式1

initial begin

//复位低有效,已定义"'timescale 1ns/1ps"

rst_n = 0;

#100;//100ns延时

rst_n = 1;//撤销复位

......

end

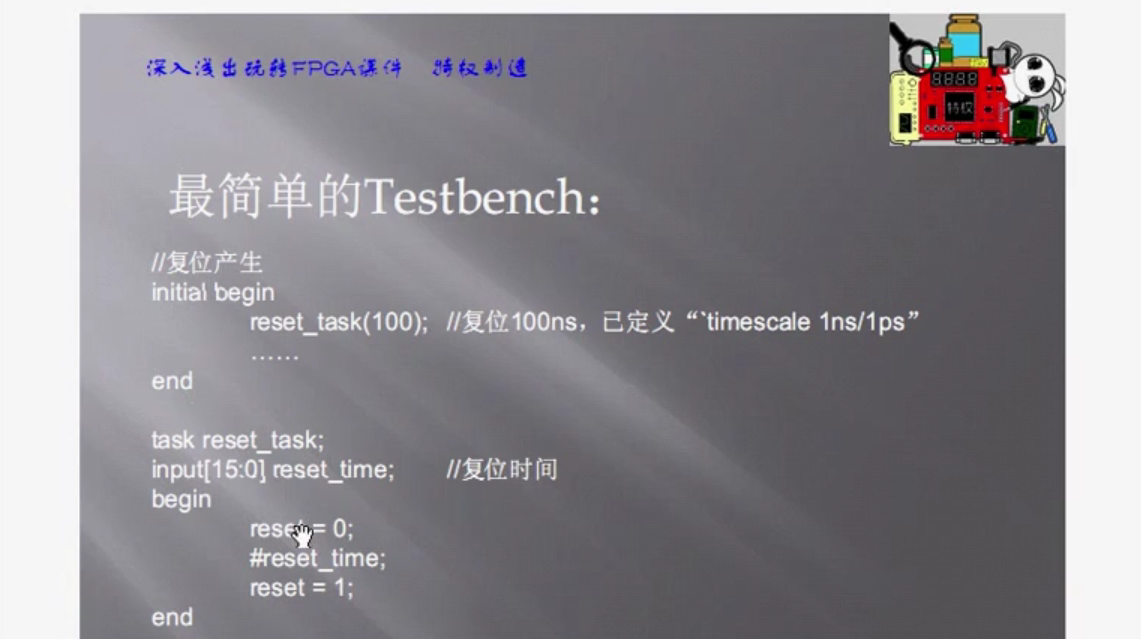

//复位产生方式2

initial begin

reset_task(100);//复位100ns,已定义"'timescale 1ns/1ps"

......

end

task reset_task;

input[15:0]reset_time; //复位时间

begin

reset = 0;

#reset_time;//延迟了100ns

reset = 1;

end

浙公网安备 33010602011771号

浙公网安备 33010602011771号